Fターム[5J056AA11]の内容

Fターム[5J056AA11]の下位に属するFターム

ECLから (6)

TTL、DTLから (1)

I2Lから (1)

MOSから (9)

MES、ショットキーFETから

その他から (3)

ECLへ (1)

TTL、DTLへ

I2Lへ

MOSへ (18)

MES、ショットキーFETへ

信号線 (3)

その他へ (1)

振幅拡大 (172)

振幅縮小 (38)

正電位の振幅→負電位の振幅 (2)

負電位の振幅→正電位の振幅

一方の電位の振幅←→正負の電位の振幅 (5)

直流レベルのシフト (74)

信号幅の変換 (3)

タイミングの調整、遅延、同期 (148)

整合 (285)

Fターム[5J056AA11]に分類される特許

1 - 20 / 246

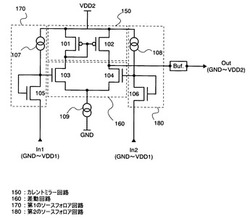

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

低いデューティサイクル歪みを有するレベルシフタ

【課題】低いデューティサイクル歪み及び高い電源電圧マージンの高速レベルシフティング回路を提供する。

【解決手段】レベルシフタ100は、反転回路104と、クロス接続されたレベルシフティングラッチ102と、SRロジックゲートラッチ103とを含み、レベルシフティングラッチ102の第1、第2出力は、SRロジックゲートラッチ103のセット(S)入力ノード121およびリセット(R)入力ノード120に接続され、反転回路104は、レベルシフティングラッチ102の第1入力ノード112に非反転の信号を供給すると共に、第2入力ノード113に反転の信号を供給し、入力信号のロウからハイへの変化はSRロジックゲートラッチ103をリセットし、ハイからロウへの変化はSRロジックゲートラッチ103をセットするように構成されている。

(もっと読む)

デジタルアイソレータおよびフィールド機器

【課題】低消費電力化を図る。

【解決手段】入力側電源3と1次側回路1との間にスイッチ部6を設け、従来は1次側回路1の入力信号端子TINに与えるようにしていた入力信号DINをスイッチ部6へ与えるようにし、入力信号DINのレベルに応じてスイッチ部6のオン/オフを行わせるようにする。また、入力信号端子TINには入力信号DINに代えて、1次側回路1への電源電圧VDD1の供給遮断時に強制的に固定される2次側回路2からの出力信号DOUTのレベルとは逆のレベルの信号(出力信号「H」強制固定の場合は「L」レベルの信号、出力信号「L」強制固定の場合は「H」レベルの信号)を与えるようにする。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

レベルシフト回路及びそれを用いたドライバと表示装置

【課題】低振幅の入力信号を高速に高振幅信号に変換するレベルシフト回路を提供する。

【解決手段】第1及び第2の出力端子の一方を第1電圧レベルに設定する第1のレベルシフト回路10と、第2の電圧端子と、前記第1及び第2の出力端子との間に接続され、前記第1及び第2の出力端子の他方を第2電圧レベルに設定する第2のレベルシフト回路20と、第1の制御信号に基づき、第1及び第2の入力信号が第1及び第2の入力端子に入力される時点で前記第2電圧レベルとされる一つの出力端子について、前記一つの出力端子と第2の給電端子間の電流経路を、前記第1及び第2の入力信号が前記第1及び第2の入力端子に入力される時点を含む所定期間、切断し、前記所定期間の後、前記一つの出力端子と前記第2の給電端子間の電流経路の切断を解除する制御を行う手段を備え、前記第1及び第2の出力端子の出力振幅は、前記第1及び第2の入力信号の振幅よりも大きい。

(もっと読む)

半導体装置

【課題】入力信号のHレベルとLレベルとを同時にレベルシフトすることができ、且つ低

コストで製造できるレベルシフタ、及びレベルシフタを具備する表示装置を提供すること

を目的とする。

【解決手段】単一の導電型のトランジスタで構成されたオフセット回路を用いて、入力信

号をオフセットする。そして、オフセットされた入力信号をオフセット回路と同じ導電型

のトランジスタで構成された論理回路に供給することによって、入力信号のHレベルとL

レベルとを同時にレベルシフトすることができる。また、オフセット回路と論理回路は単

一の導電型のトランジスタで構成されているため、表示装置を低コストで製造することが

できる。

(もっと読む)

レベルシフト回路

【課題】伝播遅延時間を短縮する。

【解決手段】インバータINV1,INV2と、ラッチ回路1と、反転駆動回路2,3と、セレクタ4を備える。N1=VSS2、N2=VSS2、N3=VSS2、N4=VDD2のとき、入力端子INがVDD1→VSS1に変化したとき、トランジスタMP5をオンして大きな電流をVDD2からノードN1に流し高速にノードN1をVSS1→VDD2に変化させる。その後、トランジスタMP5はオフし、ノードN1はインバータINV4でVDD2に保持される。これで、N1=VDD2、N2=VDD2、N3=VDD2、N4=VSS2となる。次に入力端子INがVSS1→VDD1に変化したとき、トランジスタMN2がオンして大きな電流をノードN1からVSS2に流し高速にノードN1をVDD2→VSS2に変化させる。

(もっと読む)

バススイッチ回路

【課題】より確実に信号を伝送することが可能なバススイッチ回路を提供する。

【解決手段】バススイッチ回路は、第1、第2の入出力端子間に接続されたバススイッチ素子を備える。バススイッチ回路は、第1の入出力端子と第1の電源電圧が印加される第1の電圧線との間に接続され、第1の制御信号により制御される第1のスイッチ素子を備える。バススイッチ回路は、第2の入出力端子と第2の電源電圧が印加される第2の電圧線との間に接続され、第2の制御信号により制御される第2のスイッチ素子を備える。バススイッチ回路は、第1の信号と、第2の信号とに基づいて、遅延信号を出力する遅延信号生成回路を備える。バススイッチ回路は、第1の信号、第2の信号、および、遅延信号に基づいて、第1および第2の制御信号を出力する制御信号生成回路と、を備える。

(もっと読む)

回路装置及び電子機器

【課題】断熱的回路動作により消費電力を抑制することができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、第1の基準電圧を基準として電圧が周期的に変化する第1の電源電圧VP、及び第2の基準電圧を基準として電圧が周期的に変化する第2の電源電圧VMが供給されて断熱的回路動作を行う断熱的回路100と、第1の直流電源電圧VDD及び第2の直流電源電圧VSSが供給されて動作する非断熱的回路120と、断熱的回路100と非断熱的回路120との間に設けられるラッチ回路210とを含む。ラッチ回路210は、断熱的回路100からの出力信号D2を、第1の電源電圧VPが極大となり第2の電源電圧VMが極小となるタイミングに対して設定された第1のラッチ期間においてラッチし、出力信号D2のラッチ信号Q2を非断熱的回路120に対して出力する。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

レベルシフト回路

【課題】更なる消費電力低減および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2Aは、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41および第2NMOSトランジスタ42を備える他、第3NMOSトランジスタ43および第4NMOSトランジスタ44をも備える。第1PMOSトランジスタ31および第2PMOSトランジスタ32それぞれのソース端子は、第1基準電位Vddlより高い第2基準電位Vddhに接続される。第3NMOSトランジスタ43および第4NMOSトランジスタ44それぞれのドレイン端子も第2基準電位Vddhに接続される。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

出力回路および出力制御システム

【課題】回路面積の縮小を図りつつ、待機電流をカットオフすることが可能な出力回路を提供する。

【解決手段】出力回路は、第1の電源にソースが接続された出力pMOSトランジスタを備える。出力回路は、第1の出力pMOSトランジスタのドレインと接地との間に接続された出力nMOSトランジスタを備える。出力回路は、出力pMOSトランジスタのドレインと前記出力nMOSトランジスタのドレインとの間に接続された出力端子を備える。出力回路は、前記出力pMOSトランジスタのオン/オフを制御するための第1のゲート制御信号を第1のゲート制御端子から出力する第1のレベルシフタ回路を備える。出力回路は、前記出力nMOSトランジスタのオン/オフを制御するための第2のゲート制御信号を第2のゲート制御端子から出力する第2のレベルシフタ回路と、を備える。

(もっと読む)

レベルコンバータ

【課題】ラッチ回路の初期値が確定可能であり、出力信号の立ち上がり/立ち下がり特性の対称性に優れたレベルコンバータを提供すること。

【解決手段】シフト回路12のラッチ回路31を構成する第1及び第2インバータ回路32,33の出力端子となるノードN1,N2とトランジスタTp1,Tp2との間に初期値設定用のMOSトランジスタTp3,Tp4を挿入接続した。そして、MOSトランジスタTp3のゲートをグランドに接続し、MOSトランジスタTp4のゲートを初期値設定回路34に接続した。初期値設定回路34は、第2の高電位電源VDEが所定レベル以下の場合には該MOSトランジスタTp4のゲート電位を第2の高電位電源VDEとグランドとの間の中間電位に制御し、第2の高電位電源VDEが所定レベルより高い場合には該MOSトランジスタTp4をオンするようそのゲート電位をグランドレベルに制御する。

(もっと読む)

レベルシフト回路および半導体集積回路装置

【課題】回路面積を大きくせずに電源投入時の貫通電流を防止するレベルシフト回路を提供する。

【解決手段】アシスト回路(200)は、第1および第2スイッチ(N21、P21)と、電圧設定回路(300)とを備える。第1および第2スイッチ(N21、P21)は、第1インバータ(101)の出力ノード(BB)と、レベルシフタ(104)の入力ノード(AA)との間に挿入され、第1電源電圧(VDD1)に応答して回路を開閉する。第2電源電圧(VDD2)に基づいて設定電圧を生成する。第1電源電圧(VDD1)が供給される前に第2電源電圧(VDD2)が供給されたときに、レベルシフタ(104)の入力ノード(AA)の電圧を設定電圧に設定する。

(もっと読む)

携帯電話

【課題】回路の誤動作や回路面積の増加を防止しつつ一部の回路の電源電圧を

遮断して消費電力を低減させることができる半導体集積回路を提供する。

【解決手段】チップ内部を複数の回路ブロック(11,12,13……)に分

割するとともに、いずれかの回路ブロックへの電源電圧の供給を遮断可能に構成

し、電源電圧の供給を遮断可能な回路ブロックから他の回路ブロックへ出力され

る信号の経路上であって信号が分岐される前の位置に、信号の伝達を遮断可能な

信号ゲート手段(31)と電源遮断直前の信号を記憶可能な記憶手段(32)と

を含むブロック間インタフェース回路(30)を設けるようにした。

(もっと読む)

半導体集積回路装置

【課題】低コストで低電圧高速動作が可能なI/O回路を備えた半導体集積回路装置を提供する。

【解決手段】I/O回路において、I/O電圧vcc(例えば3.3V)をvcc_18(例えば1.8V)へ低電圧化した場合に、速度劣化を引き起こす部分が、レベル変換部と、メインの大型バッファを駆動するためのプリバッファ部分であることに着目し、レベルアップコンバータLUCとプリバッファPBFの回路に高電圧(電圧vcc)を印加することにより、低コストで低電圧高速動作が可能なI/O回路を実現する。

(もっと読む)

1 - 20 / 246

[ Back to top ]