Fターム[5J056BB58]の内容

Fターム[5J056BB58]に分類される特許

1 - 20 / 102

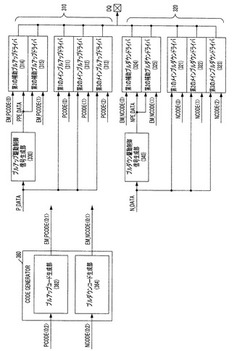

信号送信回路

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

シリアルインターフェース装置、及びシリアルインターフェース方法

【課題】外部装置に接続された所定の入出力端子の信号レベルに基づいて、外部装置に対応したシリアルインターフェースを接続する。

【解決手段】外部装置と接続された入出力端子から得られる信号に基づいて、前記外部装置に対応したシリアルインターフェースを接続するシリアルインターフェース装置であって、前記入出力端子に接続された切り離し可能なプルダウン回路と、前記プルダウン回路の接続又は切り離しを制御するプルダウン制御手段と、前記プルダウン制御手段により前記プルダウン回路が接続されているとき、前記入出力端子の信号レベルを検出する信号レベル検出手段と、前記信号レベル検出手段の検出結果に応じて、前記外部装置に対応したシリアルインターフェースに切り替える切替手段とを有することにより上記課題を解決する。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

半導体装置

【課題】入力信号のHレベルとLレベルとを同時にレベルシフトすることができ、且つ低

コストで製造できるレベルシフタ、及びレベルシフタを具備する表示装置を提供すること

を目的とする。

【解決手段】単一の導電型のトランジスタで構成されたオフセット回路を用いて、入力信

号をオフセットする。そして、オフセットされた入力信号をオフセット回路と同じ導電型

のトランジスタで構成された論理回路に供給することによって、入力信号のHレベルとL

レベルとを同時にレベルシフトすることができる。また、オフセット回路と論理回路は単

一の導電型のトランジスタで構成されているため、表示装置を低コストで製造することが

できる。

(もっと読む)

入出力回路

【課題】回路規模の増大を抑制しながら、コネクタに接続されたチャージャーの種類を的確に認識する。

【解決手段】電源検出回路12は、VBUS端子への外部からの給電を検出する。チャージャー検出回路14は、DP端子およびDM端子の電圧を検出することにより、チャージャーの種類を特定する。チャージャー検出回路14は、DP端子およびDM端子の少なくとも一方のオープン、プルアップ、プルダウンまたは両端子間のショートを検出する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

タイミング制御回路、タイミング制御方法、及びシステム

【課題】タイミングマージンの減少を抑制すること。

【解決手段】システム装置21に形成された制御回路36は、可変容量35の容量値を制御し、トレーニング回路45にタイミングトレーニングを実行させる。トレーニング回路45は、メモリ12がデータDQに基づく正常なデータを書き込むことができる設定値の最大値と最小値を出力する。制御回路36は、その最大値及び最小値に基づいてデータDQのウインドウ幅を算出し、より大きなウインドウ幅に対応する容量値を可変容量35に設定する。

(もっと読む)

通信モジュール、リーダライタ

【課題】部品を内蔵できる配線板を有する通信モジュールであって、アンテナの特性に応じて整合の調整が可能な通信モジュールおよびこれを用いたリーダライタを提供すること。

【解決手段】配線板と、配線板に備えられた通信処理用ICと、通信処理用ICに電気的に接続されて配線板に備えられた、外部に設けられるアンテナとの整合をとる整合回路と、を具備し、整合回路が、キャパシタまたはインダクタを少なくとも含む受動素子回路網の回路であり、該受動素子回路網を構成する回路エレメントのうちの少なくともひとつが、配線板に内蔵された第1の受動素子部品と、配線板の面上に実装された、該第1の受動素子部品と同じ種の受動素子部品である第2の受動素子部品との並列接続または直列接続でできた回路エレメントである。

(もっと読む)

スイッチ装置および試験装置

【課題】入力電圧範囲の大きな半導体スイッチ装置を提供する。

【解決手段】外部から入力される制御電圧に応じて第1端子および第2端子間を電気的に接続または切断するスイッチ装置であって、第1端子および第2端子の間にソースおよびドレインが接続され、当該スイッチ装置に入力される入力電圧とゲート電圧との差に応じてオンまたはオフとなるメインスイッチと、制御電圧および入力電圧に応じて第1基準電圧を電圧シフトさせた駆動電圧をメインスイッチのゲートに供給する制御部と、を備えるスイッチ装置を提供する。

(もっと読む)

入出力回路

【課題】昇圧した電圧でLCDを駆動するような場合でも、その共用の入出力端子から実用的な出力データ信号の出力が可能となる。

【解決手段】入出力回路100において、スリーステート出力バッファが出力データ信号とLCD駆動信号の両方に対してそれぞれ第1、第2出力バッファ106、108として設けられ、第1出力バッファ106を構成するPチャンネルMOSトランジスタ116のソース端子に電源電圧V1が供給され、且つ出力データ信号が出力として選択されていない状態でPチャンネルMOSトランジスタ116、118のバックゲート端子に電源電圧V1から昇圧された昇圧電圧V2が供給され、更に、第2出力バッファ108を構成するPチャンネルMOSトランジスタ116のソース端子とバックゲート端子とに昇圧電圧V2が供給される。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路における、低電圧動作、高耐圧、低消費電流、高速動作、検査容易化を目的とする。

【解決手段】第1のレベルシフト要素(1)として、低い電圧の場合に電源ONで動作状態として用い、電源電圧が高い場合には素子の耐圧を確保して電源OFFし停止状態で用いる低電源電圧用レベルシフト回路を備え、第2のレベルシフト要素(2)として、電源電圧が低い場合には電源OFFし停止状態で用い、電源電圧が高い場合に、素子の耐圧を確保して電源ONし動作状態で用いる高電源電圧用レベルシフト回路とを備え、電源電圧によって切り替えられるように構成する。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

半導体スイッチ

【課題】端子切替時の挿入損失の増加を抑制した半導体スイッチを提供する。

【解決手段】実施形態によれば、電源回路部と制御回路部とスイッチ部とを備えた半導体スイッチが提供される。前記電源回路部は、内部電位生成回路と第1のトランジスタとを有する。前記内部電位生成回路部は、電源線に接続され、入力電位よりも高い第1の電位を生成する。前記第1のトランジスタは、前記内部電位生成回路の入力と出力との間に接続され、前記第1の電位が前記入力電位よりも低下したときオンして前記第1の電位を前記入力電位以上に保持するようにしきい値電圧が設定されたことを特徴とする。前記制御回路部は、前記第1の電位を供給され、ハイレベルまたはローレベルの制御信号を出力する。前記スイッチ部は、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体チップおよびその設計方法

【課題】設計期間が短く、面積効率が高く、電源配線における電圧降下が小さな半導体チップと、その設計方法を提供する。

【解決手段】この半導体チップは、複数の電源ドメインD1〜D4に分割された内部回路2を備える。互いに異なる電流駆動能力を有する複数種類のレギュレータR1,R2を予め準備しておき、各電源領域毎に、当該電源領域の最大負荷電流を供給するために必要なレギュレータの種類と数を選択し、選択した1または2以上のレギュレータによって当該電源領域用の電源回路を構成する。したがって、設計期間が短くて済む。

(もっと読む)

出力バッファ回路及びその制御方法

【課題】高耐圧トランジスタを用いないで高電圧出力と高速出力とを両立させる出力バッファ回路を提供する。

【解決手段】第1及び第2の電源が供給され、第1の電源系の入力論理信号を第2の電源系の出力論理信号に変換して出力する出力バッファ回路であって、第2の電源と接地との間にソースドレインが直列に接続された第1乃至第4のトランジスタと、第2の電源電圧が大きいときに、第1の電源電圧を出力し、第2の電源電圧が小さいときに接地電圧を出力する第1制御電圧生成回路と、入力論理信号が接地レベルのときに第2の電源の電圧値を出力し、入力論理信号が第1の電源電圧レベルのときに第1制御電圧生成回路の出力電圧と略同一電圧レベルの信号を出力する第2制御電圧生成回路と、を備える。

(もっと読む)

回路装置及びシステム

【課題】出力モードを切り換えることにより効率的な通信ができる回路装置及びシステム等を提供すること。

【解決手段】回路装置100は、バスHBSを介してホスト装置200に信号を出力する出力回路110と、出力回路110を制御する出力制御回路120とを含む。出力回路110は、出力ノードNQと第1の電源ノードVSSとの間に設けられる第1の導電型のトランジスターTNと、出力ノードNQと第2の電源ノードVDDとの間に設けられる第2の導電型のトランジスターTPとを含む。出力制御回路120は、第1の出力モードでは、第1の導電型のトランジスターTN及び第2の導電型のトランジスターTPのいずれか一方をオフにし、他方をオン・オフする制御を行い、第2の出力モードでは、第1の導電型のトランジスターTN及び第2の導電型のトランジスターTPを排他的にオン・オフする制御を行う。

(もっと読む)

バス接続回路を備えた半導体装置及びそのバス接続方法

【課題】 バスラインにプルアップ抵抗が接続されているか否かに関わらず所望のバス通信動作を得ることができる半導体装置及びそのバス接続方法を提供する。

【解決手段】 バスラインに内部プルダウン抵抗を介してプルダウン電圧を印加し、プルダウン電圧の印加時のバスラインの電圧レベルに応じてバスラインへの半導体装置外の外部プルアップ抵抗の接続があるか否かを判定する外部プルアップ判定手段と、バスラインへの外部プルアップ抵抗の接続がないと判定されたときプルダウン電圧の印加を停止してバスラインに内部プルアップ抵抗を介してプルアップ電圧を印加し、一方、バスラインへの外部プルアップ抵抗の接続があると判定されたときプルダウン電圧の印加を停止する内部プルアップ設定手段と、を備える。

(もっと読む)

半導体集積回路装置

【課題】論理機能を有するシステムの小型化を図る。

【解決手段】第1電源電圧が印加される第1外部入力端子、第2電源電圧が印加される第2外部入力端子、第1入力信号が印加される第3外部入力端子、第2入力信号が印加される第4外部入力端子、接地電位が印加される第5外部入力端子及び信号を出力するための外部出力端子を有する。更に、第3外部入力端子からの信号を入力し信号レベルを変換して出力するレベルシフト回路及びその回路の出力信号を入力して外部出力端子に出力し第2入力信号に応じて出力をハイインピーダンス状態にすることが可能なトライステートバッファ回路を有する。レベルシフト回路は前段及び後段部分から構成され、第1電源電圧は前段部分の電源電圧として、第2電源電圧は後段部分及びトライステートバッファ回路の電源電圧として供給される。接地電圧はレベルシフト回路及びトライステートバッファ回路の接地電圧とされる。

(もっと読む)

1 - 20 / 102

[ Back to top ]