Fターム[5J056DD01]の内容

Fターム[5J056DD01]の下位に属するFターム

バイポーラトランジスタ (120)

SIT

FET (1,892)

トランジスタの組合せ (2,266)

Fターム[5J056DD01]に分類される特許

1 - 16 / 16

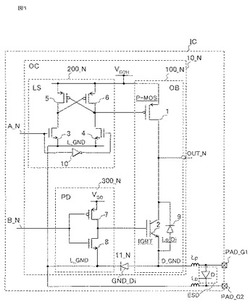

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

半導体装置

【課題】半導体素子の劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置40は、正極41及び負極42と、正極41と負極42の間に配置される出力電極43と、正極41と出力電極43を接続する正側スイッチング素子51と、正極41と出力電極43を接続し、正側スイッチング素子51とは電流を逆方向に流す正側ダイオード52と、負極42と出力電極43を接続する負側スイッチング素子61と、負極42と出力電極43を接続し、負側スイッチング素子61とは電流を逆方向に流す負側ダイオード62と、を備える。正極41及び負極42の電極厚さは、出力電極43の電極厚さよりも薄く設定される。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路のdv/dt等に起因するコモンモードノイズによる誤判定を抑制し、ロバスト性の高いスイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】レベルシフト回路のオフセットが設けられたセット用負荷の信号レベルとリセット用負荷との信号レベルとを比較し、セット用負荷のレベルがリセット用負荷のレベルに比べ前記オフセットより低くなったことを判定して前記セットパルスを検出する

(もっと読む)

容量性信号結合を用いた高電圧駆動回路及び関連する装置及び方法

【課題】ほぼ1つの面内に形成された駆動電極と感知電極とを備えた高電圧駆動回路を提供する。

【解決手段】装置は、駆動回路と感知回路との間の信号の転送を、駆動電極および感知電極を介して容量性手段によって行い、かつIGBTなどの高電圧装置を高電圧トランジスタを使用せずに駆動することが可能にされ、これにより高電圧ゲート駆動回路及びICを製造する場合、SOIなどの高価な製造工程を使用する必要がなくなる。

(もっと読む)

表示装置

【課題】レベルシフト回路を備える表示装置において、レベルシフト動作の信頼性を向上させる。

【解決手段】前記レベルシフト回路は、半導体層がポリシリコン層で構成される第1薄膜トランジスタと、前記第1薄膜トランジスタの第2電極に接続される波形整形回路と、前記第1薄膜トランジスタの第2電極と、基準電源との間に接続される定電流源とスイッチ素子とを有し、前記第1薄膜トランジスタの制御電極にはバイアス電圧が入力され、前記第1薄膜トランジスタの第1電極には入力信号が入力される。

(もっと読む)

集積III族窒化物電力変換回路

電力段及びドライバ段を含み、全ての段がIII族窒化物電力デバイスを用いる集積回路。  (もっと読む)

(もっと読む)

電気機器の電源回路

【課題】電気機器において、2次側の電源を遮断することで機器の消費電力を削減した電気機器を提供することを目的としている。

【解決手段】機器を運転、停止するためにマイコン1とマイコン1に電源供給するためのスイッチング電源2と、マイコン1とスイッチング電源2を電気的に接続、遮断するためのトランジスタ3を備え、トランジスタ3でマイコン1の電源を遮断して、機器の消費電力を下げることができ、マイコン1の電源を遮断した状態から通常の操作で運転動作が可能である。

(もっと読む)

レベルシフト回路および表示装置

【課題】片チャネル構成のブートストラップ方式インバータを用いて負方向レベルシフタを構成する場合に、Hiレベル、Loレベルともに振幅落ちを防ぎ、十分なレベルの出力を得る。

【解決手段】レベルシフト回路10は、同一導電型TFTを用いたブートストラップ方式の負方向レベルシフタ300の後段に、ブートストラップ方式のバッファ240aおよび240bを備え、さらにその後段にブートストラップ方式のバッファ240cを備える。レベルシフタ300は2入力2出力の形式であり、バッファ240a、240b、および240cは2入力1出力の形式である。

(もっと読む)

半導体装置

【課題】スイッチング素子のスイッチング動作時における寄生インダクタンスを低減し、小型化、低コスト化が可能な半導体装置を提供する。

【解決手段】正極電極1と負極電極2との間に、FWD12を並列接続したIGBT11と、FWD14を並列接続したIGBT13とを直列に接続し、2個のIGBT11,13の接続点から電力を出力電極3へ出力する半導体装置として、正極電極1と出力電極3とを隣接させ、負極電極2を出力電極3の上側に配置し、正極電極1、負極電極2それぞれの外部接続部を出力電極3の外部接続部と対向する位置に平行に隣接させ、IGBT11、FWD12を正極電極1上に配置し、IGBT13、FWD14を、IGBT11、FWD12と負極電極2を挟んだ位置にある出力電極3上に配置する。

(もっと読む)

インバータ

【課題】製造工程が単純であり、且つ特性が向上したD−インバータ構造を提供する。

【解決手段】本発明は、プラスチック基板に有機半導体を用いてインバータ回路を作製する際、しきい電圧を位置別に制御するため、エンハンスメントタイプ特性を示すボトムゲート有機半導体トランジスタをドライバトランジスタに使用し、空乏タイプ特性を示すトップゲート有機半導体トランジスタを負荷トランジスタに使用する構造及び製造方法を提案する。

(もっと読む)

配線基板と画像形成装置

【課題】ドライバ手段が表面実装型の場合であってもドライバ手段の出力を測定することのできる配線基板と画像形成装置とを提供することにある。

【解決手段】絶縁基板上に形成された第1,第2信号線路21,22からなる伝送線路20を備え、絶縁基板上に実装されるドライバ手段から逆位相の2相の信号を第1,第2信号線路21,22を介してレシーバ手段に伝送する配線基板であって、第1,第2信号線路21,22の途中に、前記ドライバ手段の動作を測定するための第1,第2測定パッド部23,24を形成し、この第1,第2測定パッド部23,24は、第1,第2信号線路21,22間の間隔より大きく離間され且つ第1,第2信号線路21,22の線幅より大きい線幅を有し、第1,第2測定パッド部23,24と第1,第2信号線路21,22とを第1,第2接続線路25,26で接続し、第1,第2測定パッド部23,24のインピーダンスと、第1,第2信号線路21,22のインピーダンスとをほぼ同一に設定した。

(もっと読む)

半導体集積回路及びその電力低減方法

【課題】本発明は、閾値電圧の異なるトランジスタで構成され、電源電圧及び基板バイアス電圧が供給される半導体集積回路及びその電力低減方法に関し、閾値電圧の異なるトランジスタを有し、速度性能を維持した上で消費電力を最小にすることができる半導体集積回路及びその電力低減方法を提供することを目的とする。

【解決手段】半導体集積回路1は、低閾値トランジスタ及び高閾値トランジスタで構成されたメイン回路13と、混在比x0及び特定定数α、β、a、bに基づいてリーク電流を算出するリーク電流算出モジュール9と、当該リーク電流とスイッチング電流算出回路11で算出されたスイッチング電流との比の値と、速度性能を維持した上で消費電力が最小となる規定値との比較結果に基づいて、電源電圧及び基板バイアス電圧の電圧値を制御する制御モジュール15とを有している。

(もっと読む)

スイッチングデバイスの駆動回路

【課題】本発明は、セットパルスとリセットパルスの誤発生による誤動作防止機能を向上させた、スイッチングデバイスの駆動回路の提供を目的とする。

【解決手段】トランジスタ30をターンオンさせるためのパルス状のセット電圧を出力するセット側レベルシフト回路と、トランジスタ30をターンオフさせるためのパルス状のリセット電圧を出力するリセット側レベルシフト回路と、セット電圧の入力時にセット状態となってトランジスタ30をターンオンし、リセット電圧の入力時にリセット状態となってトランジスタ30をターンオフするラッチ回路と、ラッチ回路に入力されるセット電圧とラッチ回路に入力されるリセット電圧との同論理部分を除去する同相除去フィルタ12,13とを備え、リセット側レベルシフト回路の出力特性である時定数がセット側レベルシフト回路の出力特性である時定数より大きいことを特徴とする、スイッチングデバイスの駆動回路。

(もっと読む)

電力変換装置

【課題】簡単な回路構成でレベルシフト回路に対する浮遊インダクタンス成分の影響を排除でき、レベルシフト回路の誤動作等を防止できる電力変換装置を提供する。

【解決手段】この電力変換装置は、ハーフブリッジ型パワーデバイス回路105と、第1および第2の駆動回路106,107と、第1および第2の駆動回路の入力側部分に共通に設けられるレベルシフト回路113と、第1および第2の電源と、レベルシフト回路内で逆サージ現象に起因する電流が流れるのを阻止する阻止ダイオード21を備える。阻止ダイオードは、高電位側スイッチング半導体素子102等がターンオフした時、高電位側スイッチング半導体素子の浮遊インダクタンス成分等から流れ出る電流が、レベルシフト回路内で第1駆動回路側部分から第2駆動回路側部分へ流れるのを阻止する。

(もっと読む)

半導体装置

【課題】サブスレッショルドリークを伴うCMOS回路を複数含む回路ブロックでは、CMOS回路のPチャネルMOSまたはNチャネルMOSの何れかにおいてゲート・ソース間電圧を静的に0Vとしても回路ブロック全体として有意なリーク電流がながれ、低消費電力化が困難となると共に動作電圧を低電圧化した場合の安定動作が困難になる。

【解決手段】サブスレッショルドリークを伴うCMOS回路を複数含む回路ブロックに対して動作モードを定め、動作モードに応じて回路ブロックへの動作電圧の供給と停止を制御する。また、回路ブロックは、3重に形成されたウェル内に形成される。

【効果】CMOS回路の低消費電力化が図られると共に安定動作が実現できる。この効果は、動作電源電圧が低く、きわめて集積度の高いCMOS回路における低消費電力化に顕著である。

(もっと読む)

1 - 16 / 16

[ Back to top ]