Fターム[5J056DD28]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723)

Fターム[5J056DD28]の下位に属するFターム

相補動作するもの、CMOS (940)

Fターム[5J056DD28]に分類される特許

1 - 20 / 783

信号送信回路

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

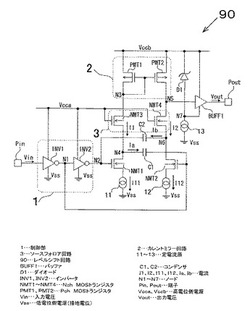

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

ラッチ回路

【課題】回路面積が小さく、かつ省電力化したラッチ回路を提供する。

【解決手段】複数の論理回路(第1の論理回路11、第2の論理回路13、第3の論理回路15、及び第4の論理回路17)によりラッチ回路1を構成し、選択信号の論理レベルに応じて差動動作とシングルエンド動作の切り替えを行う。また、これらの複数の論理回路11,13,15,17へのクロック入力信号に応じて個々の論理回路をON状態又はOFF状態にすることで、差動動作とシングルエンド動作それぞれにおいてスルー動作とホールド動作をさせる。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

半導体装置

【課題】ストローブ信号の変化によって基準電位に重畳するノイズを低減し、これにより、基準電位を用いる入力レシーバ回路の動作マージンの低下を防止する。

【解決手段】ストローブ信号IDQSTによって活性化され、入力信号DQの電位と基準電位VREFとを比較することによって出力信号IDQRを生成する入力レシーバ回路17Rと、ストローブ信号IDQSTの変化によって基準電位VREFに生じるノイズをキャンセルするノイズキャンセラ100Tとを備える。本発明によれば、ノイズキャンセラ100Tによって基準電位VREFに生じるノイズがキャンセルされることから、入力レシーバ回路17Rの動作マージンを十分に確保することができる。これにより、高速なデータ転送を行うことが可能となる。

(もっと読む)

半導体装置及びその制御方法

【課題】出力バッファ回路のインピーダンスを切り替えるためのタイミングマージンを拡大する。

【解決手段】制御期間T1においてはプルアップバッファ回路100をオン、プルダウンバッファ回路200をオフとし、制御期間T2においてはリードデータDQに基づいてプルアップバッファ回路100及びプルダウンバッファ回路200の一方をオン、他方をオフとする。制御期間T1においてはプルアップバッファ回路100のインピーダンスをインピーダンスコードODTCに基づいて設定し、制御期間T2においてはプルアップバッファ回路100及びプルダウンバッファ回路200の前記一方のインピーダンスをインピーダンスコードRONCに基づいて設定する。制御期間T3中にプルアップバッファ回路100のインピーダンスをコードODTCに基づく値からコードRONCに基づく値に変化させる。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

LVDS出力回路

【課題】 1個の基準電圧源を用いて、中間電圧(コモン電圧)及び出力振幅について温度特性がフラットになり、搭載されるICチップの面積増大を防ぐことが出来るLVDS出力回路を提供する。

【解決手段】 中間電圧(コモン電圧)作成用の基準電圧はバンドギャップリファレンス回路1の演算増幅器5の出力部から引き出し、振幅を決める定電流回路の基準電圧はバンドギャップ電圧を作る際に使用する抵抗R41、R42の節点14(中間タップ)から引き出す。そして、引き出し部分は電流検出用抵抗R6の温度特性に合わせる。検出用抵抗の温度特性と中間タップの位置での温度特性を合わせることにより、定電流回路3全体としての温度変化を無くすようにする。このようにして、1つのバンドギャップリファレンス回路1を用いて温度変化無しにLVDS出力回路を駆動できる。

(もっと読む)

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを共振により出力する電圧出力回路100と、電圧出力回路100の発振を制御する発振制御回路210とを含む。発振制御回路210は、第1の電源電圧VPが出力されるノード及び第2の電源電圧VMが出力されるノードのいずれか一方のノードである第1のノードN1に接続される駆動回路220と、駆動回路220を制御する制御回路230とを含む。発振制御回路210は、制御信号SCに基づいて、第1、第2の電源電圧VP、VMの振幅を可変に制御する発振制御を行う。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

スルーレートコントロール装置、スルーレートコントロール方法

【課題】クロック信号の出力バッファにおいて、クロック信号の周波数に応じたスルーレートの調整を行うことによりEMIノイズを抑制することが可能なスルーレートコントロール装置、およびスルーレートコントロール方法を提供すること。

【解決手段】変換ゲインGiに応じて、入力されるVCO入力電圧Viをクロック信号CKoに変換する電圧制御発振器15aを有するPLL回路24aと、VCO入力電圧Viおよび変換ゲインGiの各々に対して正の相関関係を有する制御電流Ibを出力する電圧電流変換器19aと、制御電流Ibに応じてドライブ電流を設定するバッファ制御回路21aと、ドライブ電流で、クロック信号CKoを出力する出力回路22aとを備える。よって、クロック信号CKoの周波数fに比例して出力回路22aのドライブ能力が大きくなる関係を有し、周波数fに応じて好適なスルーレートが決定することができる。

(もっと読む)

1 - 20 / 783

[ Back to top ]