Fターム[5J056DD29]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723) | 相補動作するもの、CMOS (940)

Fターム[5J056DD29]に分類される特許

1 - 20 / 940

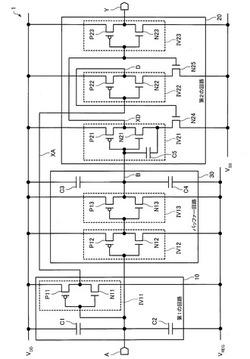

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

半導体装置及びそれを用いた電子機器

【課題】内部電源と入出力セル電源の電源投入順を考慮しなくとも、外部デバイスとの間に好ましくない貫通電流が流れない半導体装置及びそれを用いた電子機器を提供する。

【解決手段】内部回路用駆動電源に基づいて生成される第1の入出力切り替え制御信号に基づいて入出力の動作を切り替える入出力セル回路を備えた半導体装置において、前記内部回路用駆動電源とは異なる、入出力セル回路用駆動電源と、前記内部回路用駆動電源が投入されずに入出力セル回路用駆動電源が投入されている場合には、内部回路用駆動電源及び入出力セル回路用駆動電源により生成された第2の入出力切り替え制御信号が有効となり、前記入出力セル回路の出力端子をハイインピーダンス状態とするように制御する制御回路とを備える。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

集積回路、集積回路装置及び伝送システム

【課題】回路遅延の増大を抑制しながら、回路しきい値電圧のバラツキを抑制できる集積回路を提供する。

【解決手段】

集積回路1は、高位側電源VDDと出力端子OUTの間に接続されたPMOSトランジスタMP1と、低位側電源VSSと出力端子OUTの間に接続されたNMOSトランジスタMN1と、高位側電源VDDと出力端子OUTの間に直列に接続されたPMOSトランジスタMP2及びNMOSトランジスタMN3と、低位側電源VDDと出力端子OUTの間に直列に接続されたNMOSトランジスタMN2及びPMOSトランジスタMP3とを備えている。PMOSトランジスタMP1、MP2、及びNMOSトランジスタMN1、MN2のゲートが入力端子INに接続されている。また、NMOSトランジスタMN3のゲートは高位側電源に接続され、PMOSトランジスタMP3のゲートは低位側電源に接続されている。

(もっと読む)

半導体集積回路装置

【課題】構成を簡略化して消費電力を低減させることができる交流電源駆動の半導体集積回路装置を提供する。

【解決手段】入力信号に応じた論理計算を行わない任意の負荷1aと当該負荷1aに直列に接続し、入力信号に応じた論理計算を行う第1の計算部2aとを備える第1のロジック演算部10aと、同様の構成で第1の計算部2aの代わりに第1の計算部2aの計算結果と相補的な計算結果が得られるような論理計算を行う第2の計算部2bとを備え、前記第1のロジック演算部10aと並列に接続される第2のロジック演算部10bと、第1のロジック演算部10a及び第2のロジック演算部10bの間に接続され、演算された計算結果を保持する保持回路5と、第1のロジック演算部10a及び第2のロジック演算部10bに高電圧と低電圧とを相補的に変化させて印加する交流電源3とを備え、論理計算の処理と、計算結果を増幅させて出力する処理とが半周期ごとに交互に実行される。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、インバータ、第1パス制御回路、及び第2パス制御回路を備える。インバータの入力は第1ノードに接続される。ターゲット反転電位は、インバータの反転電位よりも高い。第1パス制御回路は、入力電位がターゲット反転電位より低い場合、入力端子と第1ノードとの間の電気的接続を遮断し、入力電位がターゲット反転電位より高い場合、入力端子と第1ノードとを電気的に接続する。第2パス制御回路は、入力電位がターゲット反転電位より低い第2反転電位より低い場合、グランド端子と第1ノードとを電気的に接続し、入力電位が第2反転電位より高い場合、グランド端子と第1ノードとの間の電気的接続を遮断する。

(もっと読む)

半導体装置

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファ回路を含む出力回路(101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(150)と、複数の単位バッファ回路のそれぞれのインピーダンスを調整するインピーダンス調整部(130)であって、複数の単位バッファ回路のうちの1つと実質的に同一の調整可能なインピーダンスを有するレプリカ回路(131e)と、当該レプリカ回路と並列に接続され、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数に応じて自身を流れる電流量を変化させる負荷電流生成回路(131f)とを含む、インピーダンス調整部と、を備えることを特徴とする。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な

振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路1

60を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路1

60に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場

合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能

とする。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

論理回路及びデータ処理システム

【課題】素子数が少なく、遅延が小さく、ドライバ能力を有するXORゲート回路を提供する。

【解決手段】論理回路1は、電源電位VPERIとノードn1の間に接続されたトランジスタT1と、電源電位VPERIとノードn2の間に接続されたトランジスタT2と、電源電位VSSとノードn3の間に接続されたトランジスタT3と、電源電位VSSとノードn4の間に接続されたトランジスタT4と、ノードn1とノードn3の間に直列接続されたトランジスタT5,T7と、ノードn1とノードn3の間に直列接続されたトランジスタT9,T11と、ノードn2とノードn4の間に直列接続されたトランジスタT6,T8と、ノードn2とノードn4の間に直列接続されたトランジスタT10,T12とを備える。出力信号Yは、トランジスタT5,T7の接続点及びトランジスタT6,T8の接続点から取り出される。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

半導体装置

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

低いデューティサイクル歪みを有するレベルシフタ

【課題】低いデューティサイクル歪み及び高い電源電圧マージンの高速レベルシフティング回路を提供する。

【解決手段】レベルシフタ100は、反転回路104と、クロス接続されたレベルシフティングラッチ102と、SRロジックゲートラッチ103とを含み、レベルシフティングラッチ102の第1、第2出力は、SRロジックゲートラッチ103のセット(S)入力ノード121およびリセット(R)入力ノード120に接続され、反転回路104は、レベルシフティングラッチ102の第1入力ノード112に非反転の信号を供給すると共に、第2入力ノード113に反転の信号を供給し、入力信号のロウからハイへの変化はSRロジックゲートラッチ103をリセットし、ハイからロウへの変化はSRロジックゲートラッチ103をセットするように構成されている。

(もっと読む)

1 - 20 / 940

[ Back to top ]