Fターム[5J056EE15]の内容

Fターム[5J056EE15]に分類される特許

1 - 20 / 261

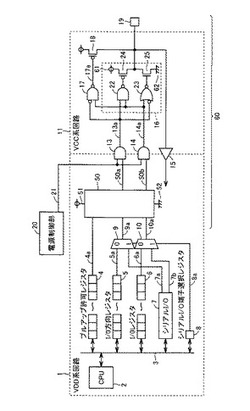

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファ回路を含む出力回路(101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(150)と、複数の単位バッファ回路のそれぞれのインピーダンスを調整するインピーダンス調整部(130)であって、複数の単位バッファ回路のうちの1つと実質的に同一の調整可能なインピーダンスを有するレプリカ回路(131e)と、当該レプリカ回路と並列に接続され、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数に応じて自身を流れる電流量を変化させる負荷電流生成回路(131f)とを含む、インピーダンス調整部と、を備えることを特徴とする。

(もっと読む)

半導体装置及びその制御方法

【課題】出力バッファ回路のインピーダンスを切り替えるためのタイミングマージンを拡大する。

【解決手段】制御期間T1においてはプルアップバッファ回路100をオン、プルダウンバッファ回路200をオフとし、制御期間T2においてはリードデータDQに基づいてプルアップバッファ回路100及びプルダウンバッファ回路200の一方をオン、他方をオフとする。制御期間T1においてはプルアップバッファ回路100のインピーダンスをインピーダンスコードODTCに基づいて設定し、制御期間T2においてはプルアップバッファ回路100及びプルダウンバッファ回路200の前記一方のインピーダンスをインピーダンスコードRONCに基づいて設定する。制御期間T3中にプルアップバッファ回路100のインピーダンスをコードODTCに基づく値からコードRONCに基づく値に変化させる。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

ロジック回路及び携帯端末装置

【課題】DVDD系ロジック回路とRVDD系ロジック回路との間のアイソレートを実施しながら、小型化及び低コスト化を実現する。

【解決手段】第一のデジタル回路と第二のデジタル回路とを含むロジック回路であって、第一のデジタル回路の動作電圧である第一の電圧値を検出する第一の検出手段と、第二のデジタル回路の動作電圧である第二の電圧値を検出する第二の検出手段と、第一の電圧値と第二の電圧値とを比較する比較手段と、比較手段により得られた比較結果に応じて、第一のデジタル回路と第二のデジタル回路との間の分離結合を行う分離結合手段と、を含む。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファを含む出力回路(出力バッファ101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(出力制御回路150)と、複数の単位バッファのそれぞれのインピーダンスを調整するインピーダンス調整部であって、当該インピーダンス調整部は、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数が変化することに応じて複数の単位バッファのそれぞれのインピーダンスを調整する、インピーダンス調整部(インピーダンス調整部30)と、を備える。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

半導体装置

【課題】出力インピーダンスを切り替えた場合の出力トランジスタに対する電源配線抵抗等の見かけ上の変動を抑制し、出力インピーダンスを切り替えた際の出力インピーダンスの誤差を低減する。

【解決手段】本発明による半導体装置は、電源端子に接続された電源配線(10)と、出力端子に接続された信号配線(20)と、前記電源配線と前記信号配線との間に並列接続された複数のトランジスタ(TP1〜TP7,TN1〜TN7)と、前記複数のトランジスタのうち、特定のトランジスタ(TP4,TN4)を基準として前記電源配線および前記信号配線の長手方向において相互に対照をなす位置関係にあるトランジスタを単位として前記複数のトランジスタを選択的に活性化させる制御回路とを備える。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

出力バッファ回路及び入出力バッファ回路

【課題】流入電流の発生を抑制することができる出力バッファ回路を提供する。

【解決手段】出力バッファ回路1は、第1の高電位電源VDD1レベル又は低電位電源VSSレベルの出力信号OUT1を出力する第1出力回路10と、第1出力回路10とワイヤードオア接続され、第1の高電位電源VDD1よりも低電位である第2の高電位電源VDD2レベル又は低電位電源VSSレベルの出力信号OUT2を出力する第2出力回路20とを有している。また、出力バッファ回路1は、第1の高電位電源VDD1及び第2の高電位電源VDD2のうち第2の高電位電源VDD2のみが投入される場合に、第1出力回路10の高電位側の第1出力トランジスタT16及び第2出力回路20の高電位側の第2出力トランジスタT26の少なくとも一方のトランジスタのゲート電圧及びバックゲート電圧を第2の高電位電源VDD2レベルに設定する制御回路50を有している。

(もっと読む)

電源回路

【課題】本発明は、電源回路を提供することを目的とする。

【解決手段】本発明の電源回路は、複数のロードに電力を供給するために用いられ、複数の制御端を有する制御回路、第一電力供給回路、第二電力供給回路及び第三電力供給回路を備え、各々の電力供給回路は、それぞれ制御回路の1つの制御端に接続され、各々の電力供給回路は、全てスイッチングユニットを備え、スイッチングユニットは、第一端、第二端、第一端と第二端との間の接続及び切断を制御するスイッチング端を備え、第一端は、電源に接続され、第二端は、1つのロードに接続され、スイッチング端は、制御端に接続され、第二電力供給回路及び第三電力供給回路は、全て遅延回路をさらに備え、遅延回路は、制御回路の制御端とスイッチングユニットのスイッチング端との間に接続され、第三電力供給回路の遅延回路の遅延時間は、第二電力供給回路の遅延回路の遅延時間より大きい。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

出力バッファー回路

【課題】出力バッファーの面積・体積・部品点数の増加を抑制するとともに、ドライブ能力を向上させることが可能な出力バッファー回路を提供する。

【解決手段】第一駆動信号LINを伝達する第一入力経路4a、第二駆動信号RINを伝達する第二入力経路4b、第一入力経路4aと対応する第一出力バッファー6a及び第二入力経路4bと対応する第二出力バッファー6bを備える出力バッファー回路1において、入力経路切り替え手段8が、ステレオモード及びモノラルモードのうち、モノラルモードでは、第一入力経路4aと第一出力バッファー6a及び第二出力バッファー6bとを電気的に接続させ、出力経路切り替え手段10が、第一出力バッファー6a及び第二出力バッファー6bと、第一入力経路4a及び第一出力バッファー6aと対応する第一負荷2aとを、電気的に接続させる。

(もっと読む)

1 - 20 / 261

[ Back to top ]