Fターム[5J056GG07]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382)

Fターム[5J056GG07]の下位に属するFターム

時間遅延を利用するもの (128)

あるノードの電位を利用するもの (888)

あるノードの電流を利用するもの (185)

Fターム[5J056GG07]に分類される特許

1 - 20 / 181

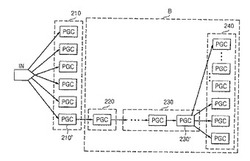

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

電子回路

【課題】高い精度で所定の検査を行うことができる電子回路を提供する。

【解決手段】本実施の形態に係る電子回路1は、図1(a)に示すように、主に、主回路2への電圧Vccの供給を切り替えるスイッチ素子としてのp型トランジスタ3と、p型トランジスタ3を駆動する第1の駆動信号を出力する駆動部4と、入力側が駆動部4に電気的に接続され、出力側がp型トランジスタ3に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて第2の駆動信号を出力する第1のインバータ部5と、入力側が駆動部4に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて検査のための検査信号を出力する第2のインバータ部6と、第2のインバータ部6の出力側に電気的に接続され、検査信号を出力する第1のパッドとしての検査パッド7と、を備えて概略構成されている。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

プリエンファシス電圧ジッターを減少させる装置および方法

【課題】データ送信における電圧ジッターを減少させる送信器回路を提供すること。

【解決手段】第一の電流源と、該第一の電流源と第一のノードとの間に結合されている第一のフィルタと、該第一の電流源と第二のノードとの間に結合されている第二のフィルタと、第二の電流源と、該第二の電流源と第三のノードとの間に結合されている第三のフィルタと、該第二の電流源と第四のノードとの間に結合されている第四のフィルタと、該第一のノード、該第二のノード、該第三のノードおよび該第四のノードに結合されているドライバースイッチ回路などを含む、送信器回路。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】7Tr3Cで構成されるインバータ回路1において、入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3と、制御素子10とを介して、入力電圧Vin2がトランジスタT2のゲートに入力される。入力電圧Vin1,Vin2がともにハイレベルの電圧Vddとなっている期間においては、入力電圧Vin3がハイレベルの電圧Vddとなっているときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

半導体装置

【課題】キャリブレーション回路に用いる基準電位生成回路を改良する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ110と、基準電位VREFを生成する基準電位生成回路200と、キャリブレーション端子ZQに現れる電位と基準電位VREFとを比較する比較回路151と、比較回路151による比較の結果に基づいてレプリカバッファ110の出力インピーダンスを変化させるコントロール回路140とを備える。基準電位生成回路200は、イネーブル信号ENに応答して活性化される電位発生部210と、イネーブル信号ENに関わらず活性化される電位発生部220とを含み、電位発生部210の出力ノードと電位発生部220の出力ノードが比較回路151に共通接続されている。これにより、イネーブル信号ENが活性化する前に正しく基準電位VREFを出力することができる。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

シフト・レジスタユニット、ゲート駆動回路及び表示装置

【課題】瞬時電流を低減し、シフト・レジスタユニットの消費電力を低減する。

【解決手段】本発明のシフト・レジスタユニットは、第1のクロック信号、第2のクロック信号、フレームスタート信号、高電圧信号および低電圧信号を入力する入力モジュールと、入力モジュールに接続され、複数の薄膜トランジスタを含み、第1のクロック信号、第2クロック信号およびフレームスタート信号に基づいてゲート駆動信号を生成し、薄膜トランジスタが形成した第1のノードのシフト・レジスタユニットの値を求める段階における電圧を電源信号のローレベルより低くなるよう制御し、薄膜トランジスタが形成した第2のノードをリセットするよう制御することを特徴とする。

(もっと読む)

TDC回路

【課題】解像度が小さく測定精度が高い時間測定を行うことができるTDC回路を提供する。

【解決手段】TDC回路1は、共通の構成を有する32個の単位セル110〜1131がリング状に接続されたリング部10等を備える。単位セル11は、第1インバータ回路111,第2インバータ回路112,スイッチSW0,スイッチSW1およびスイッチSW2を含む。第1インバータ回路111のPMOSトランジスタのゲート幅は、第2インバータ回路112のPMOSトランジスタのゲート幅のαp倍である。第2インバータ回路111のNMOSトランジスタのゲート幅は、第1インバータ回路112のNMOSトランジスタのゲート幅のαn倍である。αpおよびαnの双方が1より大きいか又は双方が1より小さい。

(もっと読む)

CMOS回路及び半導体装置

【課題】しきい電圧VTが小さくてもリーク電流が小さく、また高速にかつ小さな電圧振幅で動作するCMOS回路さらには半導体装置を提供することである。

【解決手段】ゲートとソースを等しい電圧にしたときにドレインとソース間に実質的にサブスレショルド電流が流れるようなMOST(M)を含む出力段回路において、その非活性時には、前記MOST(M)のゲートとソース間を逆バイアスするように該MOST(M)のゲートに電圧を印加する。すなわち、MOST(M)がpチャンネル型の場合にはp型のソースに比べて高い電圧をゲートに印加し、また、MOST(M)がnチャンネル型の場合にはn型のソースに比べて低い電圧をゲートに印加する。活性時には、入力電圧に応じて該逆バイアス状態を保持するかあるいは順バイアス状態に制御する。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

二段電圧レベルシフト

【課題】追加の大きなハードウェア要件なしに、ブースト電圧レベルを提供できるようにする。

【解決手段】第1の電圧レベルから第2の電圧レベルに、次に追加のブーストされた第2の電圧レベルに出力信号をシフトするための電圧レベルシフタが開示される。電圧レベルシフタは、入力信号を受信するための入力、出力信号を出力するための出力、前記第1の電圧レベルを供給する第1の電圧源に接続するための第1のパワーサプライ入力、前記第2の電圧レベルを供給する第2の電圧源に接続するための第2のパワーサプライ入力、前記ブーストされた第2の電圧レベルを供給する第3の電圧源に接続するための第3のパワーサプライ入力を含み、前記電圧レベルシフタは、前記出力から前記第1のパワーサプライ入力を隔離するため、及び前記出力に前記第2のパワーサプライ入力を接続するために前記入力信号の所定の変化に応える。

(もっと読む)

通信信号生成装置及び通信装置

【課題】集積回路の実装面積を抑えつつ通信信号の通信波形のリンギングを抑制する。

【解決手段】トランスミッタ130において、出力バッファ制御信号生成部131は、トランジスタ132a〜132d,133a〜133dをすべてオンにして第1通信線11及び第2通信線12に電流を流すことによりドミナントを表す通信信号を生成し、トランジスタ132a〜132d,133a〜133dをすべてオフにして第1通信線11及び第2通信線12に電流を流さないことによりレセッシブを表す通信信号を生成する。そして、出力バッファ制御信号生成部131は、ドミナントを表す通信信号の1ビット時間において、トランジスタ132a〜132d,133a〜133dを順にオフにして出力バッファ(第1のトランジスタ群132及び第2のトランジスタ群133)の各インピーダンスを徐々に高くする。

(もっと読む)

1 - 20 / 181

[ Back to top ]