Fターム[5J056GG09]の内容

論理回路 (30,215) | 制御対象、制御態様 (2,427) | 出力電圧を制御するもの (1,446) | 段階的に制御するもの (1,382) | あるノードの電位を利用するもの (888)

Fターム[5J056GG09]に分類される特許

1 - 20 / 888

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

レベルシフタ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、走査回路の最終段のインバータ回路の入力電圧の振幅を増大させることが可能なレベルシフタ回路を提供する。

【解決手段】第1固定電源側の2つのトランジスタ回路が第1導電型のトランジスタから成り、第2固定電源側の2つのトランジスタ回路が第2導電型のトランジスタから成るとともに、第1固定電源側の2つのトランジスタ回路及び第2固定電源側の2つのトランジスタ回路の少なくとも一方側の2つのトランジスタ回路はダブルゲートトランジスタから成るレベルシフタ回路において、一方の電源側の2つのトランジスタ回路が動作状態のとき、他方の電源側の2つのトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、インバータ、第1パス制御回路、及び第2パス制御回路を備える。インバータの入力は第1ノードに接続される。ターゲット反転電位は、インバータの反転電位よりも高い。第1パス制御回路は、入力電位がターゲット反転電位より低い場合、入力端子と第1ノードとの間の電気的接続を遮断し、入力電位がターゲット反転電位より高い場合、入力端子と第1ノードとを電気的に接続する。第2パス制御回路は、入力電位がターゲット反転電位より低い第2反転電位より低い場合、グランド端子と第1ノードとを電気的に接続し、入力電位が第2反転電位より高い場合、グランド端子と第1ノードとの間の電気的接続を遮断する。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11,12を直列に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21,22を直列に接続した第2の回路ブロック2とを備え、少なくとも1つの前記pMOSトランジスタ12のゲート及び/又は少なくとも1つの前記nMOSトランジスタ21のゲートを入力端子Vinに接続し、少なくとも1つの他のpMOSトランジスタ11のゲート及び/又は少なくとも1つの他のnMOSトランジスタ22のゲートに、オン電圧を印加する半導体回路。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

レベルコンバータ及びプロセッサ

【課題】本実施例の一側面におけるレベルコンバータは電源シーケンス制御用のトランジスタに起因する貫通電流の発生を防止することを目的とする。

【解決手段】本実施例の一側面におけるレベルコンバータは、第1電圧レベルより低い第2電圧レベルを第1論理レベルとし、基準電圧レベルを第2論理レベルとする入力信号を、第1電圧レベルを第1論理レベルとし、基準電圧レベルを第2論理レベルとする信号に変換するレベル変換回路と、第2電圧レベルを出力する第2電源がオフのとき基準電圧レベルを有し、第2電源がオンのとき第1電圧レベルを有する制御信号を出力する制御信号生成回路と、第1電圧レベルを出力する第1電源に接続された第1電源線とレベル変換回路の出力ノードの間に設けられ、制御信号に応じて、第2電源がオフのとき第1電源線と出力ノードを電気的に接続し、第2電源がオンのとき第1電源線と出力ノードを電気的に分離する接続回路を含む。

(もっと読む)

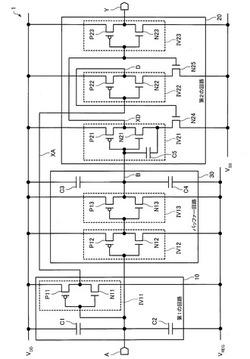

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

レベルシフト回路

【課題】レベルシフト基準電位が下がった場合にスイッチング素子を安全且つ確実に停止できるレベルシフト回路。

【解決手段】レベルシフト電源に接続された抵抗R1にドレインが接続されソースがグランドに接続されたMOSFETMN3、R1と同じ抵抗値を有しレベルシフト電源に接続された抵抗R2にドレインが接続されソースがグランドに接続されたMOSFETMN4、入力信号に基づきMN3,MN4のオン/オフを制御するパルス生成回路10、MN3がオンである場合にセット信号を生成しMN4がオンである場合にリセット信号を生成する制御部MN1,MN2,R5,R6、制御部で生成されたセット信号とリセット信号とに基づき入力信号をレベルシフトした出力信号を出力しスイッチング素子Q1を動作させるフリップフロップFF1、レベルシフト基準電位が負電位に下がったことを検出してスイッチング素子を停止させるスイッチング動作停止部INV3,FF2,AD1を備える。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体装置

【課題】消費電力を低減することができる半導体装置及びそれを用いた電子機器を提供す

ることを課題とする。

【解決手段】本発明の半導体装置は、高電位電源から第1の電位が供給され、低電位電源

から第2の電位が供給され、入力ノードに第1の信号が入力されると、出力ノードから第

2の信号を出力する。本発明の半導体装置は、第2の信号の電位差を、第1の電位と第2

の電位の電位差よりも小さくすることにより、配線の充電と放電に伴う消費電力を低減す

ることができる。

(もっと読む)

LVDS出力回路

【課題】 1個の基準電圧源を用いて、中間電圧(コモン電圧)及び出力振幅について温度特性がフラットになり、搭載されるICチップの面積増大を防ぐことが出来るLVDS出力回路を提供する。

【解決手段】 中間電圧(コモン電圧)作成用の基準電圧はバンドギャップリファレンス回路1の演算増幅器5の出力部から引き出し、振幅を決める定電流回路の基準電圧はバンドギャップ電圧を作る際に使用する抵抗R41、R42の節点14(中間タップ)から引き出す。そして、引き出し部分は電流検出用抵抗R6の温度特性に合わせる。検出用抵抗の温度特性と中間タップの位置での温度特性を合わせることにより、定電流回路3全体としての温度変化を無くすようにする。このようにして、1つのバンドギャップリファレンス回路1を用いて温度変化無しにLVDS出力回路を駆動できる。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

半導体装置

【課題】出力信号の立ち上がり時間および立下り時間が短い半導体装置を提供する。

【解決手段】このクロックドライバは、クロック信号CLKBの反転信号CLKを出力ノードN2に出力するインバータ1と、電源電圧VCCのラインと出力ノードN2との間に直列接続されたトランジスタP2,P3と、出力ノードN2と接地電圧VSSのラインとの間に直列接続されたトランジスタQ2,Q3と、クロック信号CLKを所定時間だけ遅延させてトランジスタP2,Q3のゲートに与える遅延回路3とを含む。たとえば、クロック信号CLKBが「L」レベルから「H」レベルに変化すると、所定時間だけトランジスタQ2,Q3がともにオンして、出力ノードN2から電流を引き抜く。

(もっと読む)

信号出力回路

【課題】広いダイナミックレンジと良好な周波数特性を得ることができる信号出力回路を提供する。

【解決手段】実施形態の信号出力回路は、ゲート端子へ一定の電圧Vgが印加され、ソース端子へ入力信号INが印加されるゲート接地型のNMOSトランジスタ1と、ゲート端子がNMOSトランジスタ1のドレイン端子に接続され、ソース端子から出力信号OUTが出力されるソースフォロワであるNMOSトランジスタ2とを備える。この信号出力回路は、バックゲートバイアス生成部3が、NMOSトランジスタ1およびNMOSトランジスタ2のバックゲート端子へ印加する共通のバックゲートバイアス電圧Vbを生成する。

(もっと読む)

1 - 20 / 888

[ Back to top ]