Fターム[5J056GG13]の内容

Fターム[5J056GG13]に分類される特許

1 - 20 / 280

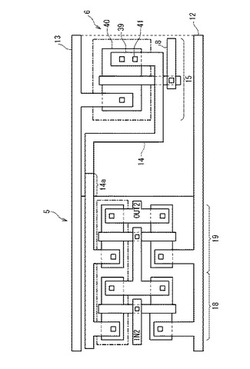

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体装置

【課題】積層され、貫通電極で相互に接続された複数の半導体チップの出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置100は、第1の被制御チップ110と、第1の被制御チップ110を制御する制御チップ120とを備える。第1の被制御チップ110は、第1の出力回路と同一の構成を持つ第1のレプリカ出力回路111と、第1のレプリカ出力回路111に接続される第1のZQ端子112と、第1のZQ端子に接続される第1の貫通電極113と、第1のレプリカ出力回路111のインピーダンスを設定する第1の制御回路114と、を含む。制御チップ120は、第1の貫通電極113に接続される第2のZQ端子121と、第2のZQ端子121の電圧と参照電圧Vrefとを比較する比較回路122と、比較回路122からの比較結果に応じて処理を行う第2の制御回路123と、を含む。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファ回路を含む出力回路(101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(150)と、複数の単位バッファ回路のそれぞれのインピーダンスを調整するインピーダンス調整部(130)であって、複数の単位バッファ回路のうちの1つと実質的に同一の調整可能なインピーダンスを有するレプリカ回路(131e)と、当該レプリカ回路と並列に接続され、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数に応じて自身を流れる電流量を変化させる負荷電流生成回路(131f)とを含む、インピーダンス調整部と、を備えることを特徴とする。

(もっと読む)

半導体集積回路

【課題】 複数のバッファに供給される信号が同時に同じレベルに変化するときに発生する電源ノイズを低減する。

【解決手段】 半導体集積回路は、動作モードに応じて信号を互いに同期してまたは非同期に出力する複数の第1バッファと、複数の第1バッファから出力される信号をそれぞれ受け、伝搬遅延時間が互いに異なる複数の第2バッファとを有している。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、シリアライザの負荷を抑制する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、n×2本の入力信号線から相補な内部データ信号DAT0/DAC0〜DAT3/DAC3を受信し、内部データ信号DT1/DC1をシリアルに出力する。プルアップバッファ回路100とプルダウンバッファ回路200は、内部データ信号DT1/DC1により制御される。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

シリアルインターフェース装置、及びシリアルインターフェース方法

【課題】外部装置に接続された所定の入出力端子の信号レベルに基づいて、外部装置に対応したシリアルインターフェースを接続する。

【解決手段】外部装置と接続された入出力端子から得られる信号に基づいて、前記外部装置に対応したシリアルインターフェースを接続するシリアルインターフェース装置であって、前記入出力端子に接続された切り離し可能なプルダウン回路と、前記プルダウン回路の接続又は切り離しを制御するプルダウン制御手段と、前記プルダウン制御手段により前記プルダウン回路が接続されているとき、前記入出力端子の信号レベルを検出する信号レベル検出手段と、前記信号レベル検出手段の検出結果に応じて、前記外部装置に対応したシリアルインターフェースに切り替える切替手段とを有することにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】適宜繰り返し行われるキャリブレーションに要する時間を短縮する。

【解決手段】半導体装置は、入力コマンドに応じ、出力ドライバーのインピーダンスを調整するキャリブレーションを、設定値を用いて行うキャリブレーション回路と、温度センサーと、前記出力ドライバーの温度特性情報を記憶する記憶回路と、前記温度センサーからの検出信号と前記記憶回路から読み出した前記温度特性情報とに基づいて前記設定値を変更する設定信号を生成し、前記キャリブレーション回路へ出力する設定回路と、を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、エンファシスの有無により消費電流が変動する問題があった。

【解決手段】本発明の半導体装置は、抵抗値を、エンファシスモードにおいて第1の抵抗値とし、非エンファシスモードにおいて第1の抵抗値よりも小さな第2の抵抗値とする可変抵抗30と、出力インピーダンスを、エンファシスモードにおいて第3の抵抗値とし、非エンファシスモードにおいて前記第3の抵抗値よりも大きな第4の抵抗値とする第1の駆動部10と、出力インピーダンスを、エンファシスモードにおいて第5の抵抗値とし、非エンファシスモードにおいて第5の抵抗値よりも大きな第6の抵抗値とする第2の駆動部11と、入力信号に応じて第1、第2の駆動部の導通状態を制御すると共に、エンファシスモードと非エンファシスモードとにおいて第1、第2の駆動部の出力インピーダンスと可変抵抗の抵抗値を切り換える制御部と、を有する。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

半導体装置

【課題】出力回路のインピーダンス調整の精度を向上する半導体装置を提供する。

【解決手段】各々が調整可能なインピーダンスを備える複数の単位バッファを含む出力回路(出力バッファ101)と、複数の単位バッファ回路のうちの1または複数個の単位バッファ回路を選択的に活性化する制御回路(出力制御回路150)と、複数の単位バッファのそれぞれのインピーダンスを調整するインピーダンス調整部であって、当該インピーダンス調整部は、制御回路によって選択的に活性化された1又は複数個の単位バッファ回路の個数が変化することに応じて複数の単位バッファのそれぞれのインピーダンスを調整する、インピーダンス調整部(インピーダンス調整部30)と、を備える。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

半導体装置

【課題】出力インピーダンスを切り替えた場合の出力トランジスタに対する電源配線抵抗等の見かけ上の変動を抑制し、出力インピーダンスを切り替えた際の出力インピーダンスの誤差を低減する。

【解決手段】本発明による半導体装置は、電源端子に接続された電源配線(10)と、出力端子に接続された信号配線(20)と、前記電源配線と前記信号配線との間に並列接続された複数のトランジスタ(TP1〜TP7,TN1〜TN7)と、前記複数のトランジスタのうち、特定のトランジスタ(TP4,TN4)を基準として前記電源配線および前記信号配線の長手方向において相互に対照をなす位置関係にあるトランジスタを単位として前記複数のトランジスタを選択的に活性化させる制御回路とを備える。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

1 - 20 / 280

[ Back to top ]