Fターム[5J067FA00]の内容

マイクロ波増幅器 (6,140) | 解決手段、解決思想 (503)

Fターム[5J067FA00]の下位に属するFターム

低電圧化、電圧の制限 (2)

定電圧化

高電圧化

小電流化、電流の制限 (4)

定電流化 (1)

大電流化 (1)

同じ特性の利用 (6)

逆特性の利用 (15)

差動信号の利用 (1)

バイアス制御 (49)

バイパスの形成 (17)

定数の変更、限定 (13)

ダミーの利用 (2)

共通利用、兼用 (10)

複数の増幅器の組み合わせ (79)

実装、半導体構造の工夫 (129)

帰還の利用 (12)

切換 (39)

位相制御 (32)

FA20△A○○の利用 (45)

Fターム[5J067FA00]に分類される特許

1 - 20 / 46

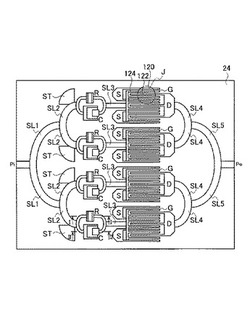

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

増幅装置、無線通信装置、及び負荷変動器

【課題】新規な負荷変動器を提供する。

【解決手段】 可変位相器を用いた負荷変動器3001であって、前記可変位相器は、信号が入力される第1ポートP1と、信号が出力される第2ポートP2と、第1可変インピーダンス3021が接続される第3ポートP3と、第2可変インピーダンス3022が接続される第4ポートP4と、を備えている。可変位相器は、第1ポートP1から入力された信号の位相が第1可変インピーダンス2021及び第2可変インピーダンス3022によって変化するものである。第1可変インピーダンス3021及び第2可変インピーダンス3022は、前記第1可変インピーダンスと第2可変インピーダンスとの間のインピーダンス差を調整可能に設けられている。インピーダンス差の調整によって、第1ポートP1及び第2ポートP2間の負荷が変動する。

(もっと読む)

回路定数調整器及びそれを用いた低雑音増幅装置

【課題】 安定した発振抑制効果が得られると共に高精度に発振が抑制できるように回路定数が調整できるようにする。

【解決手段】 回路定数を調整する回路定数調整器16であって、終端が開放端に形成されたスタブ16eと、一端17bがスタブ16eに接続されると共に、他端17aが回路定数調整対象の回路12に接続され、かつ、抵抗値が設定可能に設けられた可変抵抗器16aと、可変抵抗器16aに制御信号を出力して、当該可変抵抗器16aの抵抗値を設定する抵抗値設定器16cと、を備える。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

高調波処理回路、高周波増幅器及び高周波発振器

【課題】広帯域での2倍波整合を取れず、高効率化できる周波数範囲が狭い。

【解決手段】伝送線路2から構成されるメイン線路と、抵抗6と伝送線路5、7とが直列接続された回路から構成され、メイン線路と並列接続されたサブ線路と、一端がメイン線路とサブ線路との接続点に接続されたオープンスタブ3、4とを含んで構成される。

(もっと読む)

増幅回路

【課題】広い入力レベル範囲にわたって高い効率を実現することが可能な増幅回路を提供する。

【解決手段】増幅回路101において、入力側高調波整合回路3および出力側高調波整合回路4により、トランジスタTRの制御電極から前段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスと、トランジスタTRの導通電極から後段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスとが、それぞれ、対象信号のレベルが異なる条件下において整合されている。

(もっと読む)

分布増幅器及び分布ミキサ

【課題】異なる周波数帯の分波を可能とする分布増幅器を提供する。

【解決手段】本発明の分布増幅器は、第1,第2,第3伝送線路の一端を第1接続点で接続し、第1伝送線路の他端を第1入力端、第2伝送線路の他端を第2入力端とする入力疑似線路と、第4,第5,第6伝送線路の一端を第2接続点で接続し、第4伝送線路の他端を第1出力端、第5伝送線路の他端を第2出力端とする出力疑似線路と、入力端子が第1接続点、出力端子が第2接続点に接続された増幅部からなる単位増幅器と、第1帯域で左手系、第1帯域より高い第2帯域で右手系特性となるCRLH線路から構成され、信号入力端子を初段の第1入力端に接続し、第2入力端を次段の第1入力端に接続し、最終段の第2入力端を終端回路に接続し、第1信号出力端子が初段の第1出力端に、第2出力端がCRLH線路の第1入出力端子に、CRLH線路の第2入出力端子が次段の第1出力端に、最終段の第2出力端が第2信号出力端子にそれぞれ接続されている。

(もっと読む)

高周波回路

【課題】低周波発振と高周波発振とを共に抑制することができる高周波回路を提供する。

【解決手段】高周波回路は、複数のトランジスタ12、複数の入出力整合回路14−1,14−2、複数の抵抗体18、低周波発振抑制回路17を含む。複数のトランジスタは、半導体基板11上に並列に配列形成される。複数の入出力整合回路は、それぞれ第1の絶縁基板13−1上、第2の絶縁基板13−2上に、複数のトランジスタにそれぞれ接続されて設けられている。低周波発振抑制回路は、所望の周波数帯域を透過帯域として有し、並列に配列形成された複数のトランジスタのうち、両側のトランジスタのゲート端子に接続される。複数の抵抗体は、複数の入出力整合回路間のうち、トランジスタに最も近い位置に形成されるとともに、透過帯域の最も低い周波数の発振に対して低周波発振抑制回路を作用させることが可能な長さで、複数の入出力整合回路間に形成される。

(もっと読む)

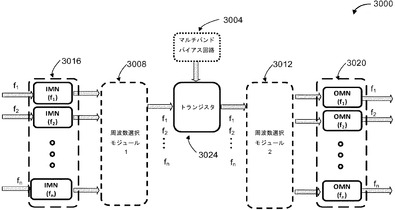

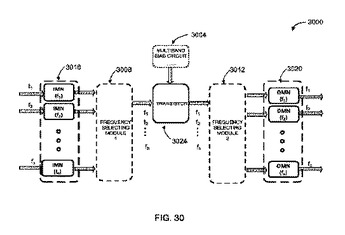

メタマテリアル電力増幅器システム

電力増幅システムならびにそのモジュールおよび構成要素が、CRLH構造に基づいて設計され、高効率および高線形性が提供される。

(もっと読む)

(もっと読む)

ドハティ合成回路及びドハティ増幅器

【課題】簡単に最適な状態へ調整することができるドハティ増幅器を提供する。

【解決手段】メインアンプから出力されるRF信号を入力するRF入力Aと、ピークアンプから出力されるRF信号を入力するRF入力Bと、ドハティ増幅器を構成する二つの高周波アンプの出力信号を90度の位相差を加えて合成するλ/4ラインと、λ/4ラインの合成部のインピーダンスを出力負荷インピーダンスへ変換するインピーダンス変換回路と、インピーダンス変換回路に接続された電源ラインと、RF入力Aからλ/4ラインとの間に挿入されたコントロール電圧VcontAで動作をOPENとSHORTに切り替え可能なDCスイッチAと、RF入力Bからλ/4とインピーダンス変換回路の合成部との間に挿入されたコントロール電圧VcontBで動作をOPENとSHORTに切り替え可能なDCスイッチBと、電源ラインに接続した歪みを抑圧する高調波制御回路とから構成されることを特徴とする。

(もっと読む)

ドハティ増幅器

【課題】出力側の線路長を短縮して、消費電力の低減や、歪や出力電力の広帯域化を図ることができるドハティ増幅器を得ることを目的とする。

【解決手段】キャリア増幅器1の出力端5が構造対称線6よりもピーク増幅器11側に配置され、ピーク増幅器11の出力端15が構造対称線16よりもキャリア増幅器1側に配置されているように構成する。これにより、出力側の線路長を短縮して、消費電力の低減や、歪や出力電力の広帯域化を図ることができる。

(もっと読む)

高周波増幅回路

【課題】高周波トランジスタの寄生容量成分も含めたトランジスタの出力インピーダンスに対して広帯域にわたって良好なインピーダンス整合を可能にする。

【解決手段】高周波トランジスタと、当該トランジスタの出力端子に対して設けられた、設計中心周波数にて前記トランジスタの寄生容量成分と並列共振する電気長のショートスタブと高周波短絡用キャパシタからなる直列回路と、終端負荷とのインピーダンス整合を行う少なくとも3段の直列接続されたインピーダンス変成線路とを備え、中間段のインピーダンス変成線路の特性インピーダンスが、トランジスタと接続するインピーダンス変成線路および終端負荷と接続するインピーダンス変成線路のいずれよりも高インピーダンスとなるように設定されるようにしたものである。

(もっと読む)

ドハティ増幅装置

【課題】ハティ増幅装置において、ET電源の給電能力が十分でないET電源を用いても高出力が得られ、低出力レベルにおいても更なる高効率化を図る。

【解決手段】入力信号を増幅するメインアンプ1とピークアンプ2とを備え、入力信号が小信号である時には前記ピークアンプ2がOFF状態となり、入力信号が大信号である時には前記ピークアンプ2がON状態となるドハティ増幅装置10において、固定電圧Vsを前記ピークアンプ2に給電する固定電源部11と、入力信号のエンベロープ振幅レベルに応じて調整される可変電圧Vdを前記メインアンプ1に給電するエンベロープトラッキング電源部9と、を備えている。

(もっと読む)

高周波電力増幅器

【課題】 従来のF級増幅器やドハティ増幅器では、出力レベルが低いと高調波の出力レベルも低くなって、高調波反射による効率向上の効果が小さくなるという問題点があり、広範囲の出力レベルにわたって、高い効率が得られる高周波電力増幅器を提供する。

【解決手段】 高調波反射回路16を備えた増幅器20の入力段に、2次高調波を発生する高調波発生器32と、発生した2次高調波の位相を調整する可変移相器33と、2次高調波の振幅を調整する可変減衰器34とを備え、基本波の入力信号に2次高調波を注入して合成器36で合成し、合成された信号を増幅器20に入力して増幅し、更に、高調波反射回路16で2次高調波をFET14へ反射することで、2次高調波反射レベルを上げて、電圧電流波形の重なりを低減し、電力効率を向上させる高周波電力増幅器である。

(もっと読む)

ドハティ増幅回路

【課題】良好な電力効率と歪み特性と、インピーダンス変換による回路損失の低減及び周波数帯域の広帯域化の両方を実現できる増幅回路を提供する。

【解決手段】本発明のドハティ増幅回路は、互いに位相が逆の1対の信号がそれぞれに入力される第1及び第2ノードと、キャリア増幅器13と、キャリア増幅器13の入力と前記第1ノードとの間に接続された伝送線路12と、前記第2ノードに入力が接続されたピーク増幅器14と、出力側伝送線路バラン16と、伝送線路12と同じ電気長を有する伝送線路15とを具備している。出力側伝送線路バラン16の2つの平衡ポート26、27の一方は、キャリア増幅器13の出力に接続され、他方は、伝送線路15を介してピーク増幅器14の出力に接続されている。

(もっと読む)

ドハティ増幅装置

【課題】ドハティ増幅装置をより高効率にする。

【解決手段】入力信号をメインアンプ1とピークアンプ2とで増幅して、前記両アンプ1,2の出力を合成して出力するドハティ増幅装置10において、前記メインアンプ1と前記ピークアンプ2とに共通の電源電圧を供給する可変電源部7と、入力信号のエンベロープ振幅レベルを検出するエンベロープ検出部6と、前記可変電源部7によって前記両アンプ1,2に供給される電源電圧の大きさを調整するために前記可変電源部7を制御する制御部8と、を備え、前記制御部8は、前記エンベロープ検出部6によって検出された入力信号のエンベロープ振幅レベルに応じて、前記両アンプ1,2に供給される電源電圧の大きさを制御するよう構成されている。

(もっと読む)

高周波増幅回路とこれを有する無線通信装置

【課題】 電源電圧が変動しても効率の低下を緩和することができ、しかも、製造時の歩留まりを向上し得るエンベロープトラッキング法に基づく高周波増幅回路を提供する。

【解決手段】 本発明の高周波増幅回路12aは、マイクロ波帯の高周波の入力信号が入力される半導体増幅素子21と、入力信号の包絡線の変動に追随する電源電圧を半導体増幅素子21に印加する電源回路22と、半導体増幅素子21の出力側に接続された出力整合回路24と、電源電圧が変動しても半導体増幅素子21の効率が最大となるように当該出力整合回路24のインピーダンスを調整するインピーダンス調整部とを備えている。

(もっと読む)

F級増幅回路

【課題】増幅素子(FET)の出力容量が無視できない高周波でも高効率のF級増幅回路。

【解決手段】入力信号基本角周波数ωo及び高調波成分を含む信号を出力するFET10と、FETの出力端子NOFと接地端子を接続する第1のリアクタンス二端子回路12と、FETの出力端子NOF側に配置される基本波整合回路16と、基本波整合回路の入力端子とFETの出力端子間に接続される第2のリアクタンス二端子回路14と、基本波整合回路の出力端子と接地端子を接続する負荷22とを備え、FETの出力インピーダンスを出力抵抗Roと出力容量Coからなる並列回路とし、第1のリアクタンス二端子回路12は、直流成分に対して開放、偶数高調波成分に対して短絡、奇数高調波成分に対してFETの出力容量Coと並列共振し、第2のリアクタンス二端子回路は直流成分に対して短絡、奇数高調波数成分に対して開放となる。

(もっと読む)

歪発生器及び歪補償増幅器

【課題】出力する歪のレベルを調整することができる歪発生器を提供する。

【解決手段】ドライバ増幅器22で増幅され且つ非線形側伝送線路34−1から取り出されたマイクロ波信号は、マイクロ波信号のキャリア周波数に整合している出力端側整合回路52を介して歪発生用トランジスタ増幅器48の出力端子48bに供給される。歪発生用トランジスタ増幅器48は、出力端子48bに供給されたマイクロ波信号を基に歪成分を発生して入力端子48a及び出力端子48bの両方から出力する。可変移相器54により歪発生用トランジスタ増幅器48の入力端子48aと開放端57との間を通過する信号の位相を調整することで、歪発生用トランジスタ増幅器48の出力端子48b側で合成される歪成分の位相差を調整することができる。

(もっと読む)

マイクロ波電力増幅器

【課題】分配偏差を低減してFETセルの均一動作を図って利得と出力を向上することができるマイクロ波電力増幅器を得る。

【解決手段】複数のFETセル1から構成されているFETチップ2と、FETチップ2の入力側に接続された入力整合回路3と、FETチップ2の出力側に接続された出力整合回路4とを設けたマイクロ波電力増幅器であって、入力整合回路3、出力整合回路4の少なくとも一方は、FETチップ2に接続され、FETチップ側に信号の伝播方向に沿って複数本のスリット11又は12が異なる間隔で設けられたマイクロストリップ線路7又は9を含む。

(もっと読む)

1 - 20 / 46

[ Back to top ]