Fターム[5J079BA21]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 起動 (147)

Fターム[5J079BA21]の下位に属するFターム

高速起動 (59)

不要モード発振防止 (21)

起動、停止制御を行うもの (21)

Fターム[5J079BA21]に分類される特許

1 - 20 / 46

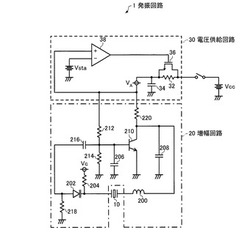

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】起動時の異常発振を抑えるとともに負荷の大きさによらず電源電圧の低電圧化が可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(水晶振動子10)と、共振子の一端から他端への帰還経路を有する増幅回路20と、電圧供給回路30と、を含む。電圧供給回路30は、電源電圧Vccが入力される時定数回路(抵抗32とコンデンサー34によるRC積分回路)を有し、電源電圧Vccが入力されてから時定数回路の時定数に応じて立ち上がるとともに増幅回路20の負荷によらず一定電圧となる駆動電圧VAを発生させ、駆動電圧VAを増幅回路20に供給する。

(もっと読む)

発振器

【課題】異常発振を抑圧する発振器を提供する。

【解決手段】発振信号を起動および増幅する増幅部120と、所望の発振周波数を決定する共振部130と、を備えた発振回路110と、発振回路110の出力端子に緩衝回路160が接続された発振器100であって、増幅部120は入出力用の2端子を有する低域濾波器140と、3段の増幅回路とを有し、増幅部120の1段目増幅器121と2段目増幅器122とが不平衡型増幅器で、3段目増幅器123がオペアンプであり、2段目増幅器122の出力端子が、低域濾波器140の入力端子と3段目増幅器(オペアンプ)123の反転入力端子に接続され、低域濾波器140の出力端子が、3段目増幅器(オペアンプ)123の非反転入力端子に接続されている。

(もっと読む)

半導体装置

【課題】消費電力の低減と、製造コストの低減とを両立する発振回路を提供する。

【解決手段】本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

(もっと読む)

発振装置

【課題】消費電力が少なく、高い周波数精度を保持することを可能にする。

【解決手段】発振装置1は、恒温槽付水晶発振器であるOCXO15と、温度補償水晶発振器であるTCXO16とを有しており、CPU11により、OCXO15で基準精度以上のクロック周波数が得られない場合にTCXO16をオンとして使用し、OCXO15をオフとする制御手段を有する。制御手段は、発振装置1起動時にTCXO16のみをオンとして使用し、OCXO15の温度が基準精度以上のクロック周波数が得られる状態に上昇した際に、TCXO16をオフとし、当該OCXO15をオンすることを特徴とする。

(もっと読む)

温度補償発振器および電子機器

【課題】温度補償動作を行いつつ、温度補償動作の周波数調整より高精度での周波数補正を行う。

【解決手段】温度補償発振器1は、圧電素子11および前記圧電素子11に並列に接続された第1可変容量素子14,15を有し、入力された温度補償電圧に応じた周波数で発振した基準信号を出力する発振回路10と、前記第1可変容量素子に並列に接続され、前記第1可変容量素子より低い容量を有する第2可変容量素子91,92と、前記第2可変容量素子の端子間電圧として、起動時からの経過時間に応じて変化し、所定値に収束する電圧を起動時補償電圧として出力する補償回路30とを有する。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路からなり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

圧電発振器

【課題】水晶発振器などの圧電発振器において、出荷時あるいは受け入れ時の調整や検査に際して発振器特性の計測に要する時間を短縮でき、かつ、電子機器への搭載後においても一時的な電源断に対応できるようにする。

【解決手段】水晶振動子12などの圧電振動子と発振回路16とを収容した容器10内に、二次電池11と、二次電池11に対する充放電を制御する充放電制御回路14と、電源端子に外部電源電圧Vccが印加されているときには電源端子を選択し、それ以外の場合に充放電制御回路14を選択して電力を発振回路16に供給する切替回路15と、を設ける。

(もっと読む)

水晶発振回路の負荷容量の決定方法およびそれを用いた電子機器

【課題】本発明の目的は、水晶振動子を用いた発振回路の発振起動時間と負荷容量CL値の関係を明確にし、所望の発振起動時間から負荷容量CL値を決定することである。

【解決手段】本発明は、水晶振動子を用いた発振回路において、発振起動時間Tsと発振余裕度Mの関係式又は関係グラフを用いて発振余裕度Mから発振起動時間Ts(Ts0)を求める手段(A)と、発振起動時間Tsと負荷容量CLの関係式、及び駆動電流値Iosから、任意の駆動電流値Iosにおける発振起動時間Tsと負荷容量CLの関係式を求める手段(B)と、前記手段(B)において求められた発振起動時間Tsおよび負荷容量CLの関係式を用いて、前記手段(A)で求められた発振起動時間Ts0に対応する負荷容量CLを決定する手段(C)と、を含むことを特徴とする。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

温度補償型圧電発振器

【課題】周波数が安定するまでの時間を短縮することができると共に、消費電力を低減出来る圧電発振器の提供。

【解決手段】温度補償を行う前の状態で、温度に対する変曲点近傍の変動が0ppm/℃又は、0ppm/℃近傍となる圧電振動素子120と、集積回路素子130には、圧電振動素子の共振周波数に基づいて発振信号を出力する第1のインバータINV1と、負荷容量になる可変容量ダイオードCV1、CV2を含む発振回路部Xと、発振信号を増幅する第2のインバータINV2を含む増幅回路部Yと、温度補償用制御データを記憶するためのメモリ部Mと、温度補償用制御データに基づき、温度補償を行なう温度補償信号制御回路部Tと、第1のインバータINV1と電源電圧端子Vddの接続間及び増幅回路部の第2のインバータINV2と電源電圧端子Vddの接続間に配置され、インヒビット端子INHからの信号により動作するスイッチSW1と、を備える。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

定電流駆動発振回路

【課題】簡単な構成でかつ、少ない消費電流で発振器の発振余裕を維持することができる。

【解決手段】VXT>Vtnの場合、コンデンサ22に充電されていた電荷が放電され、放電電流の一方がP−MOSFETを流れるドレイン電流Ibhと共にグランドに流れ、放電電流の他方が帰還抵抗34を介して水晶振動子20の他方の極に流れる。水晶振動子20の他方の極に流れた放電電流は、水晶振動子20の発振周波数に基いて発振される。発振された信号は、帰還抵抗34によって水晶振動子20の他方の極へ帰還されて発振を継続する。バック電位VDは、VD=VD2−(−VXT)となる。バック電位VDの値が大きくなるとP−MOSFET26のN型基板の空乏層が広がるため、P−MOSFET26の閾値電圧は小さくなり、ドレイン電流Ibhの量が少なくなる。

(もっと読む)

共振マイクロエレクトロメカニカルシステムをスターとするのに用いられるアンプにおけるDCオフセットを克服するためのシステム及び方法

【課題】共振マイクロエレクトロメカニカルシステム(MEMS)初期化成功を補償するシステム及び方法、特にESDによるDCオフセットを克服する方法を提供する。

【解決手段】システム20は、共振センサ24、駆動デバイス26、チャージアンプおよび電圧利得回路28を含む。スタートアップ時に、チャージアンプ及び電圧利得回路は、共振センサから信号を受信し、DCオフセットに関するこの信号を補償するために、駆動に関するクロック信号を生成し、これを用いて、安定した状態の動作モードにおける共振センサを実現する。回路は、受信された信号に関する信号にグリッチを生成するようにトグル切り替えされた複数の利得スイッチを含む。グリッチは、DCオフセットを補償する。受信された信号に関する信号が、リファレンス信号を越えている場合、比較器は、駆動デバイスに関するクロック信号を生成する。

(もっと読む)

発振回路

【課題】振動子の安定発振を早める発振回路に関する技術を提供するとともに、それを用いた超音波流量計を提供する。

【解決手段】共振周波数を有する振動子1と、前記振動子に接続されるアンプ2と、付勢パルス発生手段3と、前記付勢パルス発生手段3と前記振動子1およびアンプ2との接続・非接続とを切替える切替え手段4とを備え、前記振動子1の駆動初期は前記切替え手段4により、前記振動子1と前記付勢パルス発生手段3とを接続するようにした発振回路。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

発振検出回路

【課題】低電力化を可能とし、リーク電流による誤動作の発生を無くした発振検出回路を提供する。

【解決手段】発振検出回路は、基準電圧源に接続された第1の入力端子と発振回路出力端に接続された第2の入力端子とを有しており、複数のバイポーラトランジスタにより構成される差動回路を採用し、差動回路の出力端に接続され出力端の電位に応じて充電または放電を行う容量素子と、容量素子の電位に基づいて発振信号端の所望の発振状態を検出する検出回路を有する。

(もっと読む)

発振装置

【課題】比較的小さい回路規模で、発振停止を防ぐことのできる発振装置を提供する。

【解決手段】電流源から動作電流が加えられて発振信号を出力する発振器と、予め決められた時間の計測を開始し、前記計測が終了するとタイムアウト信号を出力する、少なくとも一つのタイマーと、前記タイマーから出力される前記タイムアウト信号を受信したときに、前記発振器から出力される前記発振信号の発振レベルと基準レベルとを比較し、前記発振レベルが前記基準レベル以上である場合、前記発振器に加えられる前記動作電流を減少させる制御を少なくとも1回行う制御部と、を備える。

(もっと読む)

1 - 20 / 46

[ Back to top ]