Fターム[5J079BA33]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 波形整形 (124)

Fターム[5J079BA33]の下位に属するFターム

Fターム[5J079BA33]に分類される特許

1 - 10 / 10

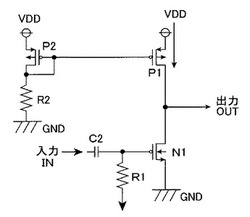

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

水晶発振回路

【課題】 ディレイ回路を設けたり、バイアス決定回路のバイアス点と波形整形回路のスレッショルドとを異ならせたりすることなく、消費電流を低減し、自励発振や異常発振を防ぐことができる水晶発振回路を提供する。

【解決手段】 水晶振動子21および水晶振動子21の出力を増幅し、電源電圧より低い定電圧源LDO1により駆動される発振増幅器22を有する水晶発振部2の出力に、電源電圧レベルにレベルシフトする結合コンデンサ3が接続され、その結合コンデンサ3の出力に、ソースがVddに、ゲートがVssに接続されたPチャネルMOSトランジスタ41およびソースがVssに、ゲートがVddに接続されたNチャネルMOSトランジスタ42のそれぞれのドレインが接続されたバイアス決定回路4が接続され、そのバイアス決定回路4の出力に振幅検知回路5、および波形整形回路6が接続されている。

(もっと読む)

発振回路

【課題】 共振子を有し、発振開始時間が早く、同時に信号の波形が潰れることのない発振回路を提供する。

【解決手段】 発振回路は、SAW共振子等の共振子と、共振子で生成された高周波などの信号を増幅して出力すると共に共振子に帰還信号を出力する差動増幅器と、電源投入時から所定時間と所定時間経過後とで差動増幅器の利得を変える手段を有している。利得を変える手段として、例えば、差動増幅器に、定電圧源に接続された第1のトランジスタ13と、定電圧源あるいは第2の電源にスイッチ15を切り替えることにより接続される第2のトランジスタ14を有する利得調整回路を配置する。スイッチ15の接離により、安定した振幅で発振を開始するまでの時間が短縮でき、安定発振後に回路の利得を抑えることにより信号の波形が潰れることの無い発振回路が実現できる。

(もっと読む)

発振回路

【課題】従来の発振回路では、インダクタを有することから、小型化が困難であった。

【解決手段】各エミッタが実質的に接地電位に接続された第1のトランジスタ及び第2の

トランジスタと、第1のトランジスタのベース及び第2のトランジスタのベース間に接続

された水晶振動子と、第1のトランジスタのコレクタ及び電源電位間に接続された第1の

抵抗器と、第2のトランジスタのコレクタ及び電源電位間に接続された第2の抵抗器と、

第1のトランジスタのコレクタ及び第2のトランジスタのベース間に接続された第1のキ

ャパシタと、第2のトランジスタのコレクタ及び第1のトランジスタのベース間に接続さ

れた第2のキャパシタと、第1のトランジスタのベース及びエミッタ間に接続された第3

のキャパシタと、第2のトランジスタのベース及びエミッタ間に接続された第4のキャパ

シタと、を含む。

(もっと読む)

発振回路

【課題】所望の周波数以外の周波数で発振するおそれがあり、また、出力される発振周波

数の波形が正弦波に近似しないことがあった。

【解決手段】第1の電位及び第2の電位間に接続されたCMOSインバータと、一端がC

MOSインバータの入力端に接続された第1の素子部と、一端がCMOSインバータの入

力端に接続され、他端がCMOSインバータの出力端に接続された第2の素子部と、一端

がCMOSインバータの出力端に接続された第3の素子部と、一端が第1の素子部の他端

及び第3の素子部の他端に接続され、他端が第1の電位及び第2の電位のうちの一方に接

続された第4の素子部とを含み、第1、第2、第3、及び第4の素子部は、水晶振動子、

抵抗器、インダクタ及びキャパシタのいずれかであり、第1、第2、及び第3の素子部に

より規定される周波数で発振する。

(もっと読む)

発振装置

【課題】発振信号の発振周波数が高いほど、当該発振信号の波形がより鈍っていた。

【解決手段】発振信号を生成する発振回路と、前記生成された発振信号を増幅する増幅回路と、相互に並列接続された複数のCMOSバッファ回路であって、当該複数のCMOSバッファ回路の入力端が一つに接続されており、当該複数のCMOSバッファ回路の出力端が一つに接続されており、各CMOSバッファ回路が前記増幅された発振信号をバッファリングする前記複数のCMOSバッファ回路と、を含む。

(もっと読む)

直列接続インバーター圧電発振器

【課題】 圧電振動子を用い微少質量を検出するQCM等のセンサー発振器、通信用の周波数基準に用いる発振器の発振回路に適用する。

【解決手段】 シミュレーションによって回路の発振条件を明確にし,その結果を元に発振回路の構成が容易で、電源変動特性に優れ、可変範囲が広く、さらに、信頼性の高い圧電発振回路を提供する。これにより、特に低周波発振においては発振を容易に行うことができ、しかも回路のリアクタンスを、インダクターを用いること無く誘導性の範囲まで大きくすることが可能となる。

(もっと読む)

水晶発振器

【課題】 用途に応じて出力波形を変更することができる水晶発振器を提供する。

【解決手段】 水晶振動子2と発振回路とを備えた水晶発振器8において、複数の異なる波形を出力する複数の波形出力回路10〜12と、発振回路8の出力回路として、複数の波形出力回路10〜12からの何れか一つを選択するスイッチSW1a、SW1a〜SW3a、SW3bと、スイッチSW1a、SW1a〜SW3a、SW3bを選択するためのデータを記憶する内部メモリ回路6とを備えるようにした。

(もっと読む)

圧電発振回路

【課題】 広い電源電圧範囲で安定した発振特性を得ると共に、発振出力の振幅を調整することができる圧電発振回路を提供すること。

【解決手段】 直流電源VDDから供給される直流電圧の電圧変動を安定化する安定化電源6と、水晶振動子X1を振動源とする発振回路部1と、この発振回路部1の出力信号を入力とし、インバータ回路を複数段直列に連結し、その最終段のインバータ回路にデプレッション型MOSトランジスタが接続されたバッファ回路部2、3、4と、バッファ回路4の出力を増幅する出力増幅回路5とを備えた圧電発振回路において、メモリ回路11に保持されたデータに基づいて複数のMOSスイッチMsw1〜Msw3により選択される抵抗素子RD1〜RD3により、出力増幅回路5を構成するNch−トランジスタM9のゲート電圧を可変して出力レベルを調整する機能を備える。

(もっと読む)

圧電発振器

【課題】CMOSインバータを用いた圧電発振器において、電源に発生するスパイクノイズを低減し、消費電流を抑えた高性能、低価格な圧電発振器を提供することを目的とする。

【解決手段】CMOSインバータと、前記CMOSインバータの入出力間に挿入された圧電振動子とを有する圧電発振器において、前記CMOSインバータの電源端子に接続する第1の抵抗と、前記CMOSインバータの接地端子に接続する第2の抵抗とを備えたことを特徴とする圧電発振器。

(もっと読む)

1 - 10 / 10

[ Back to top ]