Fターム[5J079EA11]の内容

電気機械共振器を用いた発振回路 (23,106) | 起動停止 (199) | 増幅段の制御 (40)

Fターム[5J079EA11]に分類される特許

1 - 20 / 40

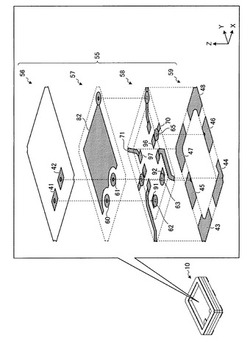

圧電発振器および電子機器

【課題】複数の出力端子からの信号の出力状態を制御した場合であっても、所望の出力特性を得ることができる圧電発振器および電子機器を提供すること。

【解決手段】実施形態の圧電発振器によれば、圧電振動素子と、回路素子と、素子搭載部材とを備える。回路素子は、圧電振動素子に接続され、圧電振動素子の振動に応じた出力信号を生成する発振回路と、複数の出力端子と、複数の出力端子からの出力信号の出力状態を制御する制御回路とを有する。素子搭載部材は、複数の外部接続用端子が形成されると共に、圧電振動素子と回路素子とを電気的に接続する第1の導電路と、出力端子と外部接続用端子とを電気的に接続する第2の導電路とを含む多層の配線領域が形成される。第1の導電路と第2の導電路とは、配線領域の積層方向において交差しない。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

水晶発振器

【課題】各々出力される信号に対して間欠動作を行い、消費電力を抑えた水晶発振器を提供する。

【解決手段】電源電圧が印加される電源電圧印加端子111と、電源電圧印加端子に接続される温度補償型水晶発振回路部110と、温度補償型水晶発振回路部及び電源電圧印加端子に接続される第一の緩衝増幅部120と、第一の緩衝部に接続され第一の緩衝部から信号が入力される第一の信号出力端子121と、第一の緩衝増幅部に接続され、第一の緩衝増幅部が動作又は停止する様に制御できる信号が入力される第一のE/D端子122と、温度補償型水晶発振回路部及び第一の緩衝増幅部に接続されている第二の緩衝増幅部130と、第二の緩衝増幅部に接続され第二の緩衝増幅部から信号が入力される第二の出力端子131と、第二の緩衝増幅部に接続され第二の緩衝増幅部が動作又は停止する様に制御できる信号が入力される第二のE/D端子132と、を備えている。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路からなり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

発振装置および該発振装置を具備したクロック発生装置、半導体装置、ならびに電子装置

【課題】過渡的な電力消費をしないピークホールド回路(あるいはボトムホールド回路)を用いることで、無駄な電力消費を抑えるとともに、ノイズの発生を抑えて発振特性の悪化を防止することが可能な発振装置技術を提供。

【解決手段】基準電圧を発生する定電圧発生回路4と、駆動電圧または駆動電流によって発振する発振回路1と、発振回路1の出力である発振信号のピークレベルを検出して出力するピークホールド回路2と、定電圧発生回路4で発生された基準電圧VREFとピークホールド回路2で出力されたピークレベルPHに応じて駆動電圧または駆動電流を増減させて発振回路1の電源端子VRに入力するレギュレータ3からなる。ピークホールド回路2は定電流で動作し過渡的な電力を消費しない構成となっている。なお、ピークホールド回路2の代わりにボトムホールド回路を用いても良い。

(もっと読む)

温度補償型圧電発振器

【課題】周波数が安定するまでの時間を短縮することができると共に、消費電力を低減出来る圧電発振器の提供。

【解決手段】温度補償を行う前の状態で、温度に対する変曲点近傍の変動が0ppm/℃又は、0ppm/℃近傍となる圧電振動素子120と、集積回路素子130には、圧電振動素子の共振周波数に基づいて発振信号を出力する第1のインバータINV1と、負荷容量になる可変容量ダイオードCV1、CV2を含む発振回路部Xと、発振信号を増幅する第2のインバータINV2を含む増幅回路部Yと、温度補償用制御データを記憶するためのメモリ部Mと、温度補償用制御データに基づき、温度補償を行なう温度補償信号制御回路部Tと、第1のインバータINV1と電源電圧端子Vddの接続間及び増幅回路部の第2のインバータINV2と電源電圧端子Vddの接続間に配置され、インヒビット端子INHからの信号により動作するスイッチSW1と、を備える。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

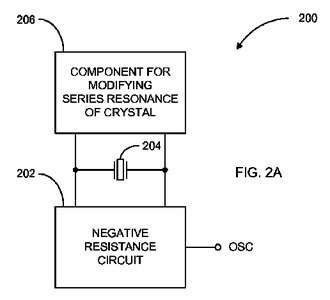

発振器の電力消費を低減させるためのシステムおよび方法

負性抵抗回路と、クリスタルと、発振信号を生成することにおいて、負性抵抗回路の電力消費を減らすために、クリスタルの直列共振を修正するように適合されるコンポーネントとを含む発振信号を生成するための装置。このコンポーネントは、正のリアクタンス回路、1つまたは複数の誘導性素子、またはクリスタルに結合された一対の誘導性素子を含む。この装置は、クリスタルに結合された可変キャパシタのような、発振信号の周波数を調整するための周波数同調コンポーネントを更に含む。負性抵抗回路は、デジタルインバータ回路、反転アナログ増幅器、または自己調整回路を含みうる。この装置は、負性抵抗回路に定常電流を供給するための静止電流ソースと、発振信号が、定義された定常状態に達するのを促進するために、スタートアップ中にのみ、負性抵抗回路にブースト電流を供給するためのスタートアップ電流ソースとを具備する。  (もっと読む)

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

共振マイクロエレクトロメカニカルシステムをスターとするのに用いられるアンプにおけるDCオフセットを克服するためのシステム及び方法

【課題】共振マイクロエレクトロメカニカルシステム(MEMS)初期化成功を補償するシステム及び方法、特にESDによるDCオフセットを克服する方法を提供する。

【解決手段】システム20は、共振センサ24、駆動デバイス26、チャージアンプおよび電圧利得回路28を含む。スタートアップ時に、チャージアンプ及び電圧利得回路は、共振センサから信号を受信し、DCオフセットに関するこの信号を補償するために、駆動に関するクロック信号を生成し、これを用いて、安定した状態の動作モードにおける共振センサを実現する。回路は、受信された信号に関する信号にグリッチを生成するようにトグル切り替えされた複数の利得スイッチを含む。グリッチは、DCオフセットを補償する。受信された信号に関する信号が、リファレンス信号を越えている場合、比較器は、駆動デバイスに関するクロック信号を生成する。

(もっと読む)

発振回路およびその制御方法

【課題】発振に係る電流消費を抑える。

【解決手段】圧電振動子12と帰還抵抗素子13を並列形態で入出力間に接続すると共にCMOS論理反転型回路で構成される増幅器11と、発振起動前において増幅器11の入出力レベルを固定化して発振を停止させておき、発振起動開始時において入出力レベルの固定化を解除し、発振起動開始の所定時間後に増幅器11の出力端にパルス信号を供給するCMOS論理回路で構成される制御回路14と、を備える。

(もっと読む)

発振回路

【課題】不要な周波数での発振を防ぐと共に、期待周波数での安定した発振を実現する。

【解決手段】発振回路100は、発振素子110と、反転増幅器120と、状態保持回路130を備える。発振素子110と反転増幅器120の入出力が互いに接続されて発振ループを構成する。状態保持回路130は、反転増幅器120の出力に同期して、反転増幅器120の出力論理を所定期間固定し、この期間内に反転増幅器120の出力状態を保持する。この所定期間は、期待発振周波数に対応する周期の半分より短く設定されている。

(もっと読む)

発振器

【課題】初期状態では発振余裕度を最大にして発振停止が発生しないようにし、安定状態へ遷移するに従い発振余裕度も小さくし、高調波も減少させてシステムとしての受信感度を向上させる発振器を提供する。

【解決手段】振動子を備え、発振余裕度の異なる複数の発振回路を備えた発振部と、発振部の出力電圧のピークを検出するピーク検出部と、ピーク検出部の検出したピーク電圧をアナログ信号からディジタル信号に変換するアナログ/ディジタル変換部と、ディジタル信号に基づいて所定の時間を計測する計測部と、ディジタル信号と計測部の出力に基づいて発振部の出力の切り替えを制御する切替信号と、計測部を制御する制御部と、を備える発振器である。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発

振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位

を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路から

なり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が

接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電

流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御

し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

発振回路及び発振器

【課題】定常時の負性抵抗と比較して起動時の負性抵抗が十分に大きな発振回路及び発振器を提供すること。

【解決手段】振動子を発振させる発振回路は、1つのトランジスタを有するインバータと、インバータと並列に接続された帰還抵抗と、インバータの入力側及び出力側のそれぞれに設けられた容量素子と、レベルが異なる2種類の電流のいずれかをインバータに供給する可変電流源と、発振回路の電源の起動から所定時間をカウントするタイマ回路と、可変電流源が供給し得る2種類の電流の内、タイマ回路によるカウント時間が所定時間を経過するまでの間はレベルが大きい方の電流を、所定時間を経過した後はレベルが小さい方の電流をインバータに供給するよう可変電流源を制御する電流制御部とを備える。

(もっと読む)

温度補償型圧電発振器

【課題】圧電振動素子を搭載した温度補償型圧電発振器の小型化が進んでも、温度補償型圧電発振器に設ける外部接続用の電極端子数を増やすことなく、増幅回路部のみを停止させるインヒビット機能を持たせた温度補償型圧電発振器を提供する。

【解決手段】集積回路素子には、発振回路部と、増幅回路部と、増幅回路部の第2のインバータと電源電圧端子の接続間に配置される第1のスイッチと、第1のスイッチと機能端子と可変容量ダイオードのカソードとの接続間に配置される第2のスイッチと、温度補償用制御データと切替用制御データとを記憶するためのメモリ部と、メモリ部内の温度補償用制御データに基づき、温度補償を行なう温度補償信号制御回路部と、メモリ部内の切替用制御データに基づき、第2のスイッチを切り替える切替信号を発生するための切替信号制御回路部とを備えている。

(もっと読む)

水晶発振回路

【課題】電源変動に起因して生じる高調波ノイズのない水晶発振回路を提供する。

【解決手段】水晶発振回路100は、電流モードロジック(CML:Current Mode Logic)で構成されたインバータ102と、インバータ102に対して並列に接続された帰還抵抗R2と、インバータ102に対して出力用抵抗R1を通して並列に接続された共振回路101とを備え、共振回路101は、インバータ102に対して出力用抵抗R1を通して並列に接続された水晶振動子103と、水晶振動子103の両端とグランド間にそれぞれ接続されたキャパシタC1及びC2とを備える。

(もっと読む)

発振回路、発振器

【課題】発振に必要な負性抵抗を小さくすると同時に回路の低消費電力を図ることのできる発振回路及び発振器を提供する。

【解決手段】発振回路10は、トランジスタM1とトランジスタM2とが差動接続されるクロスカップル型回路からなり、振動子SAWの共振点帯域で発振する。トランジスタM1は第1ソース負荷回路としての抵抗器RL1に接続され、トランジスタM2は第2ソース負荷回路としての抵抗器RL2に接続されている。また、トランジスタM1は第1ドレイン負荷回路としての抵抗器Rs1に接続され、トランジスタM2は第2ドレイン負荷回路としての抵抗器Rs2に接続されている。第1ソース負荷回路のインピーダンスの大きさが第1ドレイン負荷回路のインピーダンスの大きさ以上であり、且つ、第2ソース負荷回路のインピーダンスの大きさが第2ドレイン負荷回路のインピーダンスの大きさ以上とする。

(もっと読む)

発振回路

【課題】自励発振が起こらず、出力対称性を確保できるようにした発振回路を提供する。

【解決手段】コルピッツ型の水晶発振回路において、CMOSインバータINV1の出力側(ノードN1)と電源VDDとの間に、CMOSインバータINV1の帰還バイアス電圧を高くするためのトランジスタMP1と発振出力が無いときONするトランジスタMP2とを直列接続して、電源投入初期時にそのノードN1をVDD/2より高い電圧にプルアップし、正常発振が開始してノードN3の電圧が所定値に達すると、トランジスタMP2をOFFしてノードN1のプルアップを解除する。また、CMOSインバータINV1の出力を反転するCMOSインバータINV2を接続し、その出力側のノードN2にアンド回路AND1を接続し、正常発振が開始してノードN3の電圧が所定値に達したとき、それから遅延回路DL1の遅延の後に、アンド回路AND1のゲートを開いて、ノードN2の発振信号を出力端子OUTに出力する。

(もっと読む)

水晶発振器

【課題】回路構成を簡易にして、起動特性及びデューティー比を良好に維持した水晶発振器を提供する。

【解決手段】発振段におけるCMOSからなる発振インバータ1の出力に同じくCMOSからなる伝達インバータ2を接続した水晶発振器において、伝達インバータ2には、発振インバータ1の起動時よりも伝達インバータ2が遅れて起動する、スイッチング素子5とスイッチング素子の導通を発振インバータの起動時よりも遅らせるタイマー回路6とからなるスイッチングタイマー回路4が設けられる。このような構成であれば、発振段の起動直後(電源投入直後)、伝達インバータが起動しないので、発振段の発振成長の初期過程にある微少振幅信号は、伝達インバータの次段回路に送出されない。したがって、発振インバータでの水晶発振は後段回路の影響を受けることなく安定して増加することができる。

(もっと読む)

1 - 20 / 40

[ Back to top ]