Fターム[5J079FB09]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | カレントミラー (53)

Fターム[5J079FB09]に分類される特許

1 - 20 / 53

水晶発振回路

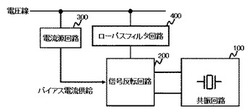

【課題】差動回路を使用することで、貫通電流に起因した高調波ノイズの影響を排除した水晶発振回路を構成することができる。しかし、他の回路が動作することによって生じた高調波ノイズが、水晶発振回路の発振出力に影響を与える場合がある。そのため、電源電圧が変動したことによる影響を軽減し、発振出力のジッタを抑制した水晶発振回路が、望まれる。

【解決手段】水晶発振回路は、水晶振動子を含む共振回路と、共振回路と接続され、差動対を含む信号反転回路と、差動対にバイアス電流を供給する電流源回路と、信号反転回路及び電流源回路に電源を供給する電圧線と信号反転回路の間に接続され、水晶振動子の固有の発振周波数より低い遮断周波数を持つローパスフィルタ回路と、を備えている。

(もっと読む)

発振装置

【課題】低消費電流を実現できる定電圧回路及びそれを用いた水晶発振回路を提供する。

【解決手段】定電圧回路10に温度特性調整素子を備えることにより、定電圧の温度変化に対して負となる傾きと、水晶発振回路20における発振可能な最低動作電圧の温度変化に対して負となる傾きとの差を極小にできるので、水晶発振回路20の消費電流を小さくでき、さらに定電圧回路10で生成する定電流を小さくすることにより、定電圧回路10の消費電流を小さくでき、発振装置100全体の消費電流を小さくできる。

(もっと読む)

振動子ユニット、発振回路及び受信回路

【課題】共振子を接続して発振回路を完成するように設計された集積回路に、温度補償を得るためにTCXOを接続すると消費電力が大きくなる。

【解決手段】振動子ユニット20は水晶振動子Xtalを含んで一体に構成され、Xtalの両端子を外部回路に接続するための外部接続端子N1,N2を備える。振動子ユニット20は、Xtalに接続された可変容量キャパシタCVと、CVの容量を制御する温度補償部28とを有する。温度補償部28はXtalの近傍における温度を検知する温度センサ回路30を備え、振動子ユニット20の外部からのトリガ信号の入力に応じて、温度センサ回路30の検知出力に基づいてCVの容量を調節する。

(もっと読む)

発振回路

【課題】コンパレータの消費電力を抑えつつ、高周波の発振出力の振幅を検出できる、発振回路を提供すること。

【解決手段】水晶振動子1を共振器として使用して発振出力Vxを生成する発振出力生成回路11と、発振出力Vxの振幅を検出する振幅検出回路15と、振幅検出回路15の出力Vsに応じて発振出力Vxをブーストするブースト回路16とを有する発振回路であって、振幅検出回路15は、発振出力Vxが入力される絶対値回路12と、絶対値回路12の出力を入力とするローパスフィルタ13と、ローパスフィルタ13の出力を入力とするコンパレータ14とを備えることを特徴とする、発振回路。

(もっと読む)

発振装置、半導体装置、電子機器および時計

【課題】水晶発振回路を含む発振装置、半導体装置、電子機器等の消費電力を全体として抑制する。

【解決手段】発振装置は、第1の定電流を生成する第1の定電流源と、第1の定電流が通電され、定電圧を生成する定電圧制御トランジスターとを含む定電圧生成回路と、定電圧発生回路から供給される定電圧により発振駆動される水晶発振回路とを備える。定電圧は、動作保証温度範囲において第1の定電流に応じて変動する第1の傾きを有する。水晶発振回路において、動作保証温度範囲における発振停止電圧は第2の傾きを有する。第1の傾きは、第1の傾きと第2の傾きとの差と相関を有する水晶発振回路の消費電流と、第1の定電流の大きさと相関を有する定電圧生成回路の消費電流との和を極小とするように定められており、第1の定電流は、定電圧制御トランジスターをサブスレッショルド領域で動作させる値に設定されている。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路からなり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

発振回路

【課題】出力信号の周波数のふらつきを抑制した発振回路を提供すること。

【解決手段】空隙を隔てて配置された第1電極11及び第2電極12を有するMEMS振動子10と、第1入力端子221及び第1出力端子222を有し、利得が1よりも大きい利得部22と、第2入力端子241及び第2出力端子242を有し、利得が1よりも小さい利得制限部24と、を含む増幅部20と、第1出力端子222と接続される出力端子30と、を含み、第1電極11と第1入力端子221とが接続され、第1出力端子222と第2入力端子241とが接続され、第2出力端子242と第2電極12とが接続される。

(もっと読む)

電圧制御発振回路及び水晶発振器

【課題】水晶振動子などの共振素子が接続される差動増幅回路を有する電圧制御発振回路において、周波数可変範囲が広くし、位相雑音を小さくし、かつさまざまな振動周波数の共振素子に適合できるようにする。

【解決手段】差動増幅回路(Q1,Q2)の第1及び第2の入力に共振素子21を接続し、この第1及び第2の入力のそれぞれに電圧制御型容量素子VC1,VC2を接続する。差動増幅回路の差動出力にそれぞれエミッタフォロワー回路(Q3,I3;Q4,I4)を接続し、容量C3と電圧制御型容量素子VC3を介して一方のエミッタフォロワー回路の出力を第2の入力に帰還させ、容量C4と電圧制御型容量素子VC4を介して他方のエミッタフォロワー回路の出力を第1の入力に帰還させる。電圧制御型容量素子VC1〜VC4に制御電圧を印加する。

(もっと読む)

水晶発振回路

【課題】反転電圧VTH、負性抵抗−RL、発振周波数f0が電源VDDの影響を受けることがなく、定電圧回路を追加する必要がなく、しかも、動作電圧も低くなり、水晶振動子に流れる電流も小さくすることができる発振回路を提供する。

【解決手段】NMOSインバータIVnと、帰還抵抗Rfと、水晶振動子Qzと、が互いに並列接続され、NMOSインバータIVnの入力と電源VSSとの間にキャパシタCGが接続され、NMOSインバータIVnの出力と電源VSSとの間にキャパシタCDが接続された水晶発振回路1において、NMOSインバータIVnが、電源VDDに接続された定電流回路Inと、定電流回路Inと電源VSSとの間に接続されたn型のMOSトランジスタTnと、から構成されている。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

発振装置および該発振装置を具備したクロック発生装置、半導体装置、ならびに電子装置

【課題】過渡的な電力消費をしないピークホールド回路(あるいはボトムホールド回路)を用いることで、無駄な電力消費を抑えるとともに、ノイズの発生を抑えて発振特性の悪化を防止することが可能な発振装置技術を提供。

【解決手段】基準電圧を発生する定電圧発生回路4と、駆動電圧または駆動電流によって発振する発振回路1と、発振回路1の出力である発振信号のピークレベルを検出して出力するピークホールド回路2と、定電圧発生回路4で発生された基準電圧VREFとピークホールド回路2で出力されたピークレベルPHに応じて駆動電圧または駆動電流を増減させて発振回路1の電源端子VRに入力するレギュレータ3からなる。ピークホールド回路2は定電流で動作し過渡的な電力を消費しない構成となっている。なお、ピークホールド回路2の代わりにボトムホールド回路を用いても良い。

(もっと読む)

発振装置

【課題】水晶発振回路の消費電力の低減を図りつつ後段回路を作動させることができる発振装置を提供する。

【解決手段】第1電源V1が、振幅検出回路3に対して第1電源電圧(3V)を供給する。第2電源V2が、水晶振動回路2に対して第1電源電圧(3V)よりも小さい第2電源電圧(1V)を供給する。振幅検出回路3は、CMOSインバータIV1の出力端子から出力される発振信号と、第2電源電圧(1V)を分圧して得た基準電圧Vrefと、それぞれのベースに接続される一対のトランジスタが設けられたコンパレータ31を備えている。

(もっと読む)

圧電発振器用オフセット回路、圧電発振器、及び圧電発振器の温度補償方法

【課題】圧電発振器用オフセット回路、圧電発振器、圧電発振器の温度補償方法を提供する。

【解決手段】圧電振動子12の発振周波数の温度特性に対応した温度補償電圧64により発振信号66の発振周波数の温度補償を行う発振回路14と、圧電振動子12の温度に対応した検出電圧62を出力する温度センサー16と、温度補償電圧発生回路18との間に介装され、発振周波数の温度の上昇時及び下降時の温度特性にそれぞれ対応して、検出電圧62をオフセットすることにより温度補償電圧64を温度方向にオフセットする第1のオフセット回路46と、温度補償電圧発生回路18と発振回路14との間に介装され、発振周波数の温度の上昇時及び下降時の温度特性にそれぞれ対応して、温度補償電圧64を電圧方向にオフセットする第2のオフセット回路54とを有する。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

温度補償圧電発振器及びその周波数調整方法

【課題】温度上昇や温度下降の際の温度変化に対する周波数のヒステリシスが少なく安定した周波数温度特性が得られる温度補償圧電発振器及びその周波数調整方法を提供すること。

【解決手段】第1のメモリー30と第2のメモリー40には、それぞれ、圧電振動子80の温度上昇時、温度下降時における周波数温度特性を特定するための第1、第2の温度補償データ32、42が記憶される。温度変化検出回路10は、温度センサー50が取得した温度情報に基づいて温度上昇と温度下降のいずれかが生じたかを検出する。セレクター20は、温度変化検出回路の検出結果に基づいて、温度上昇時、温度下降時にそれぞれ第1、第2の温度補償データを選択する。温度補償電圧発生回路60は、セレクターにより選択された第1又は第2の温度補償データに基づいて、温度補償電圧62を発生させる。電圧制御発振回路70は、温度補償電圧に基づいて圧電振動子の周波数を制御する。

(もっと読む)

D/A変換回路及び圧電発振器

【課題】安定性と高速動作を維持し、デジタル入力信号のビット数が多くなっても比較的小さい面積で集積化可能なD/A変換回路及び圧電発振器を提供すること。

【解決手段】D/A変換回路1Aは、n個のクランプ電圧生成手段(クランプ回路12a〜12h)と、n個のクランプ電圧生成手段が生成するnビットのデジタル信号の電圧を加算する電圧加算手段(加算器20)と、を含む。n個のクランプ電圧生成手段の各々は、デジタル入力信号2の対応するビットの電圧に応じて、ハイレベル又はローレベルを出力するCMOSインバーター(PMOS15aとNMOS17aによるインバーター等)と、電源電位とグランド電位をそれぞれクリップして第1の電位と第2の電位を生成し、第1の電位と第2の電位をCMOSインバーターの出力のハイレベル及びローレベルとして供給する電圧クリップ手段(PMOS14a、NMOS18a等)と、を備える。

(もっと読む)

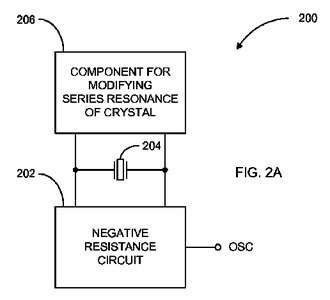

発振器の電力消費を低減させるためのシステムおよび方法

負性抵抗回路と、クリスタルと、発振信号を生成することにおいて、負性抵抗回路の電力消費を減らすために、クリスタルの直列共振を修正するように適合されるコンポーネントとを含む発振信号を生成するための装置。このコンポーネントは、正のリアクタンス回路、1つまたは複数の誘導性素子、またはクリスタルに結合された一対の誘導性素子を含む。この装置は、クリスタルに結合された可変キャパシタのような、発振信号の周波数を調整するための周波数同調コンポーネントを更に含む。負性抵抗回路は、デジタルインバータ回路、反転アナログ増幅器、または自己調整回路を含みうる。この装置は、負性抵抗回路に定常電流を供給するための静止電流ソースと、発振信号が、定義された定常状態に達するのを促進するために、スタートアップ中にのみ、負性抵抗回路にブースト電流を供給するためのスタートアップ電流ソースとを具備する。  (もっと読む)

(もっと読む)

発振回路

【課題】デューティの設計値に対して、発振信号の振幅や周波数の変化に依存したズレが生じない、デューティ調整部を有する発振回路を提供することを目的とする。

【解決手段】発振回路は、発振部からの第1の発振信号が入力され、この第1の発振信号の振幅及び周波数に依存しない立ち上がり及び立下り時間を持つ第2の発振信号を生成する第1の差動回路と、第2の発振信号が入力され、バイアス電圧源から与えられる電圧に依存したデューティを持つ第3の発振信号を生成する第2の差動回路とを有する。

(もっと読む)

温度センサ及びこの温度センサを有する発振回路

【課題】電源電圧を低電圧とした場合でも、雑音を低減させることが可能な温度センサ及びこの温度センサを有する発振回路を提供することを目的とする。

【解決手段】電源電圧が供給される定電流源とアノードが接続されており、接地にカソードが接続された温度検出素子と、前記温度検出素子のアノードの電圧のレベルをシフトする温度特性を有したレベルシフト回路と、前記レベルシフト回路の出力が非反転入力端子と接続された非反転増幅回路と、を有する構成により実現する。

(もっと読む)

1 - 20 / 53

[ Back to top ]