Fターム[5J081CC22]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 調整・制御 (181) | 周波数の可変・調整 (135)

Fターム[5J081CC22]に分類される特許

1 - 20 / 135

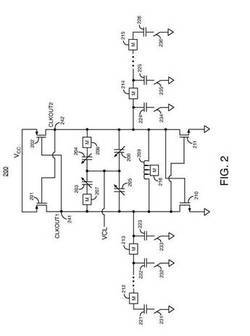

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

電圧制御発振器

【課題】コルピッツ型発振回路を用いた電圧制御発振器において、可変容量素子の非線形歪みによる位相雑音特性の劣化を抑制することができる技術を提供すること。

【解決手段】2つのバリキャップダイオード12、13が設けられたコルピッツ型発振回路で構成したVCO回路において、共振部1と帰還部2の間にバリキャップダイオード12をそのカソード側で帰還部2と接続するように設けると共に、バリキャップダイオード12のカソードと帰還部2との間に逆電圧印加部3を接続して、バリキャップダイオード12のカソードに制御電圧を印加している。またバリキャップダイオード12のカソードと帰還部2との間にバイパス部4を接続して、インダクタ40のインピーダンスを適切に調整することにより、バリキャップダイオード12のカソードに印加される発振段トランジスタ20のベース交流電圧の振幅を低減し、可変容量素子の非線形歪みを低減することができる。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

発振回路

【課題】簡易な方法で、特性の劣化を抑制し発振周波数を調整することが可能な発振回路を提供すること。

【解決手段】一対の負性抵抗回路と、前記一対の負性抵抗回路にそれぞれ接続された一対の伝送線路14a、14bと、前記一対の伝送線路にそれぞれ対称に設けられ、前記一対の伝送線路の間をボンディングワイヤによって互いに接続可能な一対のパッド40a、40bと、前記一対の負性抵抗回路の出力信号を合成する合成回路と、を有する発振回路。

(もっと読む)

周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路

【課題】自励発振回路周辺の状態変化による発振周波数の変化を抑えることができる周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路を提供する。

【解決手段】周波数自動調整機能付自励発振回路は、基準信号を生成する基準信号生成回路101bと、基準信号の周波数を調整する発振周波数調整回路101aとを有する自励発振回路101と、互いに特性の異なる1組の抵抗素子を含み、1組の抵抗素子の抵抗値の変化の違いにより自励発振回路101の周辺状態を検出し、検出された周辺状態を示す信号を出力する特性変動検出回路102_1と、特性変動検出回路102_1の出力信号に基づいて発振周波数調整回路101aによる周波数調整を制御する制御部103とを備える。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

帰還型発振装置

【課題】設計および製造が容易で、装置のサイズが小さい帰還型発振装置を提供すること。

【解決手段】帰還型発振装置1において、入力端子から入力された信号を増幅して出力端子から出力するバイポーラトランジスタ10と、マイクロストリップラインによって構成され、バイポーラトランジスタの出力端子と入力端子とを結合して出力端子から入力端子に所定の周波数の信号を帰還してバイポーラトランジスタを発振させる結合回路15と、を有する。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

補償機能付き電圧制御発振器およびこれを用いた電子鍵盤楽器

【課題】簡素な構成でVCOそのものを利用して個々のVCOの温度補償を含む直線性補償を行うこと。

【解決手段】制御部20は、2種類の電圧「V1、V2」をVCO10に供給し、その2種類の電圧「V1、V2」に対するVCO10の出力信号の2種類の周波数「f1、f2」を検出して、横軸を電圧(V)とし縦軸を周波数(f)とした場合の直線である「f=a・V+b(aは傾き、bは切片)」の係数(a、b)を求める。次いで、制御部20は、VCO10からの出力信号の周波数が「Fo」となる電圧「Vo」を「Vo=(Fo−b)/a」なる演算式によって求め、求めた電圧「Vo」をVCO10に供給する。

(もっと読む)

高周波発振器

【課題】 位相雑音を劣化させずに2倍波の出力電力を増加できる高周波発振器を得る。

【解決手段】 第1から第3の端子を有する能動素子と、前記第1と第2の端子にそれぞれ接続され、所要の周波数において誘導性となる第1と第2のリアクタンス回路と、前記第3の端子に接続され、前記所要の周波数において容量性となる第3のリアクタンス回路と、前記能動素子の前記第3の端子と前記第3のリアクタンス回路の間に並列に接続され、前記所要の周波数の2倍の周波数においてインピーダンスがショートとなる第4のリアクタンス回路と、前記能動素子の前記第3の端子と前記第3のリアクタンス回路の間に並列に接続され、前記所要の周波数におけるリアクタンスが、前記所要の周波数における前記第4のリアクタンス回路のリアクタンスと絶対値が等しく符号が逆となる第5のリアクタンス回路と、を備える。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

電圧電流変換回路及び電圧制御発振器

【課題】入力電圧に対する出力電流の動作範囲の拡大できる電圧電流変換回路を提供する。

【解決手段】入力電圧INがトランジスターM4の閾値電圧以下の場合には、トランジスターM4はオフである。一方、トランジスターM9によって入力電圧INがレベルシフトされる。そのレベルシフト後の印加電圧VAによってトランジスターM10がオンし、M10に流れるI10が、トランジスターM1に流れるI1となる。また、入力電圧INがM4の閾値電圧を超える場合には、M4がオンし、M4に流れるI4と、M10に流れるI10との和が、M1に流れるI1となる。そして、M1,M2,M3によって形成されるカレントミラー回路によって、M1に流れるI1に応じた電流が、負荷回路10,12に供給される。

(もっと読む)

発振回路

【課題】

発振周波数を切り替えたときの発振停止を抑制した発振回路を提供する。

【解決手段】

発振回路は,第1の基準電圧側に設けられた第1,第2のインダクタL,Lxと,第2の基準電圧と第1,第2のインダクタとの間にそれぞれ設けられゲートとドレインが交差接続された第1,第2のトランジスタP1,Px1と,第1,第2のインダクタンスそれぞれに接続され複数の周波数制御用キャパシタC0〜Cn,Cx0〜Cxnを並列に有する第1,第2のキャパシタ群と,第1,第2のキャパシタ群の対応する周波数制御用キャパシタ間に設けられ発振周波数制御信号に基づいて導通または非導通に制御される複数の第1のスイッチSW0〜SWnと,第1のスイッチの両端子と所定電圧との間にそれぞれ設けられた複数の第2のスイッチSWp,SWxpとを有し,発振周波数制御信号の切り替わり時に,導通から非導通に切り替えられる第1のスイッチの両端子に設けられた第2のスイッチが一時的に導通する。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

1 - 20 / 135

[ Back to top ]