Fターム[5J081EE01]の内容

LC分布定数、CR発振器 (9,854) | 周波数決定素子 (1,325) | 集中定数 (802)

Fターム[5J081EE01]の下位に属するFターム

Fターム[5J081EE01]に分類される特許

1 - 2 / 2

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

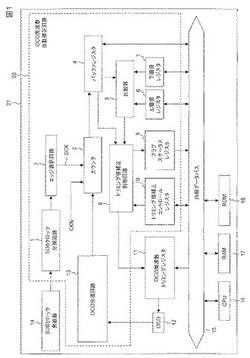

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路

【課題】従来の発振回路は、発振信号を増幅させる電流等の影響で発振周波数の高速化が制限されるという問題があった。

【解決手段】本発明にかかる差動発振回路は、帰還ループ回路を備えた差動型の発振回路であって、帰還ループ回路上に縦続接続され、入力された一対の差動入力信号を遅延させて一対の差動出力信号として出力する遅延回路2〜5と、発振回路が発振起動状態か安定状態のいずれかにあるかを検出し、検出結果を示す検出信号VSTPを出力する発振起動検出回路7と、を備える。さらに遅延回路2〜5は、発振起動検出回路7から出力された検出信号VSTPに基づいて、差動出力信号の出力電流値を制御する。このような回路構成により、発振周波数の高速化が可能である。

(もっと読む)

1 - 2 / 2

[ Back to top ]