Fターム[5J081FF02]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路構成 (543) | フィルタ (84)

Fターム[5J081FF02]に分類される特許

1 - 20 / 84

発振器

【課題】基本波を逓倍した高次高調波を用いる発振器において、出力レベルと雑音特性を向上させることを目的としている。

【解決手段】基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、基本波の通過を阻止し、基本波の高次高調波を通過させる周波数選択回路と、を備え、周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、並列経路の共振周波数が、基本波の周波数に設定されている。

(もっと読む)

発振回路

【課題】コンパレータの消費電力を抑えつつ、高周波の発振出力の振幅を検出できる、発振回路を提供すること。

【解決手段】水晶振動子1を共振器として使用して発振出力Vxを生成する発振出力生成回路11と、発振出力Vxの振幅を検出する振幅検出回路15と、振幅検出回路15の出力Vsに応じて発振出力Vxをブーストするブースト回路16とを有する発振回路であって、振幅検出回路15は、発振出力Vxが入力される絶対値回路12と、絶対値回路12の出力を入力とするローパスフィルタ13と、ローパスフィルタ13の出力を入力とするコンパレータ14とを備えることを特徴とする、発振回路。

(もっと読む)

発振回路

【課題】 位相雑音を軽減すると共に、起動時の発振の成長を妨げず、温度や経時変化の影響を受けにくくして安定した出力を得ることができる発振回路を提供する。

【解決手段】 水晶振動子X1の一端が発振用トランジスタTr1のベースに接続されると共に他端が接地され、直列接続のコンデンサCb1,Cb2が水晶振動子X1に並列に接続されたコルピッツ発振回路において、発振用トランジスタTr1のベースの前段に、水晶振動子X1の発振周波数を狭帯域化するフィルタXfを挿入した発振回路であり、また、フィルタXfの前段にバッファ用トランジスタTr2を備えた発振回路である。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

発振器

【課題】簡単な構成で高速立ち上げが可能であり、さらに従来のリング型電圧制御発振器に比べて安定な周波数の信号を生成することができる発振器を提供する。

【解決手段】制御電圧入力端子に印加された制御電圧に従って発振周波数が変化するリング型電圧制御発振器10と、リング型電圧制御発振器10の出力信号を一定時間幅のパルス信号に変換して出力するパルス整形回路20と、参照電圧からパルス整形回路20が出力する周波数が変化するパルス信号の平均電圧を差し引いた電圧を積分してリング型電圧制御発振器10の制御電圧入力端子に出力する積分回路30とを備える。

(もっと読む)

プッシュプッシュ発振器及び位相ずれ監視方法

【課題】位相ずれを確認する技術を提供する。

【解決手段】プッシュ・プッシュ発振回路100は、相互に逆位相で動作する、2つの発振器1、2と、2つの発振器1、2から出力された第1出力信号を合成する合成器101と、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を監視するための基本波監視回路102と、を備えている。即ち、基本波監視回路102を用いることで、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を確認することができる。第1出力信号の基本波を確認することで、合成器101に入力された2つの第1出力信号が逆位相であったか確認することができる。

(もっと読む)

自動列車停止装置の車上用装置

【課題】通常の運行動作に影響を与えずに、地上子との結合で変化する車上子のインピーダンス変化を検知して車上子と地上子の結合を検知して地上子から信号現示情報を得る信号現示情報取得の健全性を監視して安全性を確保することができる自動列車停止装置の車上用装置を得る。

【解決手段】車上子2と検知部301とにより構成されるインピーダンス変化検知回路を有し、検知部301が、インピーダンス変化検知回路のインピーダンスを変更するインピーダンス変更部51と、インピーダンス変更部51によりインピーダンス変化検知回路のインピーダンスを変更したことにより生じる複数の周波数の信号の特性の予め設定された変化を検出してインピーダンスの変化を検出した場合に、信号現示情報の取得動作が健全であると判断するインピーダンス変化検出部52と、を備える。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

可変容量素子

【課題】従来の可変容量素子は、容量値の精度が低い問題があった。

【解決手段】本発明の可変容量素子は、第1の電源端子と出力端子CTOPとの間に接続される第1の容量素子C1と、容量切替信号CSELに応じて導通状態が切り替えられる容量選択スイッチN1と、第1の容量素子C1と並列に接続され、かつ、容量選択スイッチN1と直列に接続される第2の容量素子C2と、容量選択スイッチN1が遮断状態とされる状態において、出力端子CTOPをリセット電圧にリセットする電荷リセット信号INITBに応じて、第2の容量素子C2と容量選択スイッチN1とを接続する容量切替ノードNDaの電圧と出力端子CTOPの電圧とを実質的に同じ電圧に設定する誤差補正回路10と、を有する。

(もっと読む)

発振器

【課題】後段にフィルタを挿入しなくても、低歪みの発振波形を得ることが可能な発振器を提供する。

【解決手段】発振器100は、MOSFETである第1トランジスタM1および第2トランジスタM2を有するクロスカップルドインバータ10を備える。この発振器100は、発振動作中に、第1トランジスタM1、第2トランジスタM2それぞれのゲートソース間電圧Vgs1、Vgs2、ドレインソース間電圧Vds1、Vds2、ゲートソース間しきい値電圧Vth1、Vth2の間に、

Vds1≧Vgs1−Vth1

Vds2≧Vgs2−Vth2

なる関係が成り立つよう構成される。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

電圧制御発振回路及びPLL回路

【課題】制御電圧に対する周波数の変化量を自由に調整できる電圧制御発振回路及びPLL回路を提供する。

【解決手段】制御電圧に応じて容量成分が制御される可変容量素子Cv1、Cv2と、可変容量素子に直列に接続された直列容量素子Cs1、Cs2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子Cp1,Cp2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子Lとを有する電圧制御発振回路100において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されている。

(もっと読む)

周波数逓倍器装置及びその操作方法

【課題】本発明は、従来の周波数逓倍器による悪い高調波抑圧比を改善し、又、周波数逓倍器からの発振周波数は、他の高調波に妨害されにくいため、周波数逓倍器装置及びその操作方法を提供することを目的とする。

【解決手段】本発明の周波数逓倍器装置は、高調波発生器、高調波抑制器及び特定高調波応用装置を含んでいる。前記高調波発生器は、基本周波数を有する入力信号を受信して、第一高調波信号成分及び第二高調波信号成分を含む高調波信号を発生させる。前記高調波抑制器は、前記高調波信号を受信して、前記第一高調波信号成分を抑制し、前記第二高調波信号成分を高める。前記周波数逓倍器装置は、高められた前記第二高調波信号成分を受信する。

(もっと読む)

広帯域発振回路

【課題】LC型VCOの出力する発振信号の周波数帯域が比較的狭くても、連続した周波数の発振信号(分周信号)の出力が可能な広帯域発振回路の実現。

【解決手段】発振信号を出力する発振器11と、発振器の出力する発振信号を受け、フィルタリングして注入同期信号NINJを出力するフィルタ14と、自己発振動作を行い、注入同期信号により発振動作が規制されて発振信号の分周信号を出力し、制御信号VbDに応じて分周比が変化する注入同期型周波数分周器12と、を備え、フィルタ14は、分周信号に同期したフィルタ制御信号に応じて、発振信号を通過させる通過特性を時間的に制御して注入同期信号NINJを発生する。

(もっと読む)

温度安定化された電圧制御発振器

【課題】温度安定化された電圧制御発振器を提供する。

【解決手段】セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a、310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370、380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b、320a、320bを含んでいる。

(もっと読む)

低雑音電圧制御発振回路

【課題】 電源雑音を除去し、低周波雑音の特性を良好にできる低雑音電圧制御発振回路を提供する。

【解決手段】 駆動用トランジスタQ1 のベースとGNDの間にコンデンサC11を設けることで、そのベースに入力される低周波ノイズを除去でき、駆動用トランジスタQ1 をhFEの低いトランジスタとすることで、電源から入力される低周波ノイズを除去することができ、発振用トランジスタQ2 のエミッタ側に、コイルL3 を設けることで、周波数特性を広域化して位相雑音の周波数特性を良好にでき、発振用トランジスタQ2 のエミッタ側に、コンデンサC7 とコイルL3 で構成される共振回路における共振周波数をVCOの発振周波数帯域の中心辺りに設定することで、ノイズの影響を受けにくい発振周波数にすることができる低雑音電圧制御発振回路である。

(もっと読む)

電圧制御発振器

【課題】電源電圧に重畳されたノイズにより発生する発振器の位相雑音を低減することができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ることのできる電圧制御発振器を提供すること。

【解決手段】この電圧制御発振器1は、直流電源端子16にコレクタが接続された発振用トランジスタ11と、発振用トランジスタ11のエミッタ・接地間に接続された第1の抵抗21と、発振用トランジスタ11のベース・接地間に接続された共振回路27と、発振用トランジスタ11のエミッタと第1の抵抗21との接続点と直流電源端子16とを接続する結合ラインL1上に設けられた第1のキャパシタ22とを具備することを特徴とする。

(もっと読む)

電圧制御発振器

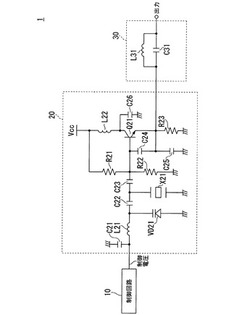

【課題】電源ラインなどから入力する外来ノイズの影響を低減できる電圧制御発振器を提供すること。

【解決手段】

発振トランジスタ11のベース・エミッタ間に第1の帰還コンデンサ12を接続し、発振トランジスタ11のエミッタ・コレクタ間に第2の帰還コンデンサ13を接続し、発振トランジスタ11のベース・コレクタ間にインダクタ14を接続してコルピッツ発振回路を構成する。発振トランジスタ11のコレクタと直流電源端子18との間にコレクタバイアス抵抗30を接続し、コンデンサ19を介してコレクタバイアス抵抗30の一端を接地する。発振トランジス11のコレクタとベースとの間にチョークインダクタ31とコンデンサ32とが直列に接続されたフィルタ回路を接続する。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

1 - 20 / 84

[ Back to top ]