Fターム[5J081KK06]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 一次要因 (534)

Fターム[5J081KK06]の下位に属するFターム

容量 (335)

インダクタンス (39)

抵抗(光電効果を含む) (35)

可変リアクタンス (9)

可変遅延(移相) (14)

可変分周

利得 (27)

分布定数(共振器との結合を含む) (59)

Fターム[5J081KK06]に分類される特許

1 - 16 / 16

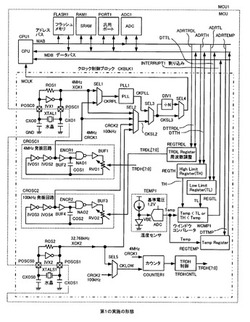

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

電圧電流変換回路及び電圧制御発振器

【課題】入力電圧に対する出力電流の動作範囲の拡大できる電圧電流変換回路を提供する。

【解決手段】入力電圧INがトランジスターM4の閾値電圧以下の場合には、トランジスターM4はオフである。一方、トランジスターM9によって入力電圧INがレベルシフトされる。そのレベルシフト後の印加電圧VAによってトランジスターM10がオンし、M10に流れるI10が、トランジスターM1に流れるI1となる。また、入力電圧INがM4の閾値電圧を超える場合には、M4がオンし、M4に流れるI4と、M10に流れるI10との和が、M1に流れるI1となる。そして、M1,M2,M3によって形成されるカレントミラー回路によって、M1に流れるI1に応じた電流が、負荷回路10,12に供給される。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

周波数逓倍器装置及びその操作方法

【課題】本発明は、従来の周波数逓倍器による悪い高調波抑圧比を改善し、又、周波数逓倍器からの発振周波数は、他の高調波に妨害されにくいため、周波数逓倍器装置及びその操作方法を提供することを目的とする。

【解決手段】本発明の周波数逓倍器装置は、高調波発生器、高調波抑制器及び特定高調波応用装置を含んでいる。前記高調波発生器は、基本周波数を有する入力信号を受信して、第一高調波信号成分及び第二高調波信号成分を含む高調波信号を発生させる。前記高調波抑制器は、前記高調波信号を受信して、前記第一高調波信号成分を抑制し、前記第二高調波信号成分を高める。前記周波数逓倍器装置は、高められた前記第二高調波信号成分を受信する。

(もっと読む)

低位相ノイズ電圧制御発振器

本発明の形態は、消費電力を低減し位相ノイズ性能を向上させるために、電流再使用技術を用いた低位相ノイズ発振器回路を含み、発振器回路は、第2のVCOに結合されている第1のVCOを備え、第1及び第2のVCOの出力は、コンデンサ等の受動素子に結合されている。第1及び第2のVCO両方の全体の消費電力は、単一のVCOの消費電力と略同じである。また、位相ノイズは、約3dBほど低減される。このため、発振器回路の消費電力を増加させることなしに、位相ノイズ性能が向上される。 (もっと読む)

CR発振回路

【課題】 MOSトランジスタ(以下、トランジスタを省略して、単にMOSと表記)のスレッシュホールド電圧が変動しても、正確な発振周波数のCR発振回路を提供する。

【解決手段】 電源端子Vccとアース間に抵抗1とキャパシタ2とが接続され、その接続点にゲートが並列接続されたPMOS3、4と、NMOS6、7のドレインおよびソースが電源端子Vccとアース間に直列に接続され、さらに、PMOS5のソースが、PMOS3、4のドレイン・ソースの接続点に、ゲートがPMOS4とNMOS6のドレインの接続点に、ドレインがNMOS8のゲートにそれぞれ接続され、NMOS8のドレインは電源端子Vccに、ソースはNMOS6、7のソース・ドレインの接続点にそれぞれ接続されている。その出力がインバータ10を介して、キャパシタ2の両端にドレイン・ソースが接続されたNMOS9のゲートに接続されている。

(もっと読む)

発振回路

【課題】発振周波数精度が高い発振回路を提供する。

【解決手段】発振回路1は、基準電流を発生する基準抵抗RE1と、基準抵抗RE1と別個に設けられ、基準抵抗RE1に電流を供給するオペアンプAMP1と、基準抵抗RE1に印加する基準電圧VREFを決定する基準電圧発生回路24と、定電圧VREGを発生する定電圧回路21とを有し、基準電流と定電圧VREGとに基づいて発振周波数を定める集積回路2と、基準抵抗RE1の温度依存性と同じ温度依存性となるように、基準電圧発生回路24の出力する基準電圧VREFの温度依存性を設定する設定レジスタ25と、を有する。

(もっと読む)

静磁波発振装置

【課題】静磁波素子が出力する発振信号の発振周波数が高いときでも小型化することのできる静磁波発振装置を提供することを目的とする。

【解決手段】静磁波素子に印加する磁界の強さを変えることで発振信号の周波数を調整する1つ以上の電磁コイルを、永久磁石の外側で且つ筐体の内部に配置することにより、永久磁石の幅寸法を電磁コイルの幅寸法より小さくすると共に、発振周波数が高いことで永久磁石が大きくなることで永久磁石の高さ寸法が大きくなっても、永久磁石が固定される筐体上面部材の凹部の深さ寸法を永久磁石の高さ寸法に合わせて大きくすることにより、静磁波発振装置の小型化を実現する。

(もっと読む)

発振器およびそれを用いた情報機器、ならびに電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

電圧制御発振器

【課題】 本発明の課題は、電圧制御発振器の位相雑音を抑制することである。

【解決手段】複数のMOSトランジスタTR12、TR13・・・のドレインは、複数のスイッチSW1、SW2・・・を介してMOSトランジスタTR11のドレインと接続されている。発振周波数を設定するための周波数設定用デジタルデータから得られるgm設定用デジタルデータによりスイッチSW1,SW2・・・をオンまたはオフにすることでMOSトランジスタTR11に並列に選択的に複数のMOSトランジスタTR12,TR13・・・を接続する。これにより、共振回路10に供給する電流を変化させる。

(もっと読む)

発振回路

【課題】 発振周波数帯の切替に連動して各周波数帯に最適なバイアス電圧を発振トランジスタに印加する。

【解決手段】 発振トランジスタ1と、互いに異なる発振周波数帯にそれぞれ対応して設けられた共振回路9、11と、1つの共振回路を選択して発振トランジスタ1のベースとコレクタとの間に結合する切替手段12とを備え、選択された共振回路に対応したバイアス電圧を切換手段12によって発振トランジスタ1のベースに印加した。

(もっと読む)

発振回路

【課題】 発振トランジスタ側の負性抵抗を周波数が離れた2つの周波数帯でも十分に得られるようにして、何れの周波数帯でも安定して発振させる

【解決手段】 発振トランジスタ20のベース−コレクタ間に介挿される共振回路26は周波数が異なる2つの周波数帯に対応して共振周波数が切り替えられるように構成され、ベース−エミッタ間に介挿される第1の帰還手段24又はエミッタ−コレクタ間に介挿される第2の帰還手段25の少なくとも一方を3個のリアクタンス素子を直並列に接続して2つの周波数帯で共に誘導性又は容量性を呈するように構成すると共に、帰還手段の他方を2つの周波数帯で一方の帰還手段と同じく誘導性又は容量性とし、2つの周波数帯で発振させた。

(もっと読む)

発振回路

【課題】 小型化かつ位相雑音を低減することができる発振回路を提供することを課題とする。

【解決手段】 差動対を構成する第1及び第2のトランジスタ(101,102)と、第1及び第2のトランジスタの第1の端子側に接続される出力合成回路(103)と、第1及び第2のトランジスタの第2の端子側に接続される電流源(106)とを有する発振回路が提供される。

(もっと読む)

電圧制御発振器

【課題】発振振幅拡大時に、発振トランジスタのMOSFETが線形領域で動作するのを防ぐことによって、低位相雑音の電圧制御発振器を提供すること。

【解決手段】レベルシフト用トランジスタ10a、10b、抵抗素子12a、12b、および定電流源トランジスタ11a、11bからなるソースフォロワ回路を、発振トランジスタのドレイン端子から他方の発振トランジスタのゲート端子への帰還経路の途中に挿入する。このことによって、発振振幅拡大時に、発振トランジスタ1a、1bが線形領域で動作するのを防ぐことができるので、低位相雑音の電圧制御発振器を実現できる。

(もっと読む)

伝送線路型共振器を用いた高周波発振器

【目的】本発明は基本波に対して4倍以上の発振周波数を得て、小型化を促進する高周波発振器を提供する。

【構成】伝送線路型共振器の互いに逆相関係にある両側の2つの共振波動点に発振用能動素子を接続して逆相発振させ、前記共振器に出力線を接続して偶数倍となる倍調波の定在波に対応する出力を得た高周波出力を得た高周波発振器であって、前記定在波は前記基本波の偶数倍となる倍調波のうちの前記基本波f0の2n(但し、nは2以上の整数)倍となる定在波を対象とし、前記出力線は前記伝送線路型共振器の中点を基準として両側の対称点に接続し、前記対称点は前記倍調波2nf0における前記中点での最大変位分布点とは逆相の最大変位分布点であるとともに、前記出力線は共通接続された構成とする。

(もっと読む)

1 - 16 / 16

[ Back to top ]