Fターム[5J081KK11]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 一次要因 (534) | インダクタンス (39)

Fターム[5J081KK11]に分類される特許

1 - 20 / 39

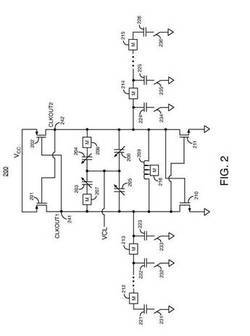

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

電圧制御発振器

【課題】コルピッツ型発振回路を用いた電圧制御発振器において、可変容量素子の非線形歪みによる位相雑音特性の劣化を抑制することができる技術を提供すること。

【解決手段】2つのバリキャップダイオード12、13が設けられたコルピッツ型発振回路で構成したVCO回路において、共振部1と帰還部2の間にバリキャップダイオード12をそのカソード側で帰還部2と接続するように設けると共に、バリキャップダイオード12のカソードと帰還部2との間に逆電圧印加部3を接続して、バリキャップダイオード12のカソードに制御電圧を印加している。またバリキャップダイオード12のカソードと帰還部2との間にバイパス部4を接続して、インダクタ40のインピーダンスを適切に調整することにより、バリキャップダイオード12のカソードに印加される発振段トランジスタ20のベース交流電圧の振幅を低減し、可変容量素子の非線形歪みを低減することができる。

(もっと読む)

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

発振器

【課題】後段にフィルタを挿入しなくても、低歪みの発振波形を得ることが可能な発振器を提供する。

【解決手段】発振器100は、MOSFETである第1トランジスタM1および第2トランジスタM2を有するクロスカップルドインバータ10を備える。この発振器100は、発振動作中に、第1トランジスタM1、第2トランジスタM2それぞれのゲートソース間電圧Vgs1、Vgs2、ドレインソース間電圧Vds1、Vds2、ゲートソース間しきい値電圧Vth1、Vth2の間に、

Vds1≧Vgs1−Vth1

Vds2≧Vgs2−Vth2

なる関係が成り立つよう構成される。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

通信ネットワークにおける使用のための発振器、周波数シンセサイザ及びネットワークノード

本開示は、周波数シンセサイザ内での周波数の生成における使用のための発振器であって、少なくとも1つの巻きを伴って金属線ループを形成する第1の誘導素子と、前記第1の誘導素子との間で第1の共振回路を形成するように構成され、少なくとも1つの第1の接続端子を通じて前記第1の誘導素子と接続される第1の容量回路と、を備え、前記第1の容量回路は、少なくとも1つの容量素子、並びに、発振を確立し及び維持するように構成される電子コンポーネント配置を含む、発振器に関する。当該発振器は、少なくとも1つの容量素子と電子コンポーネントの配置とを含む第2の容量回路が、前記第1の誘導素子との間で第2の共振回路を形成するように構成され、前記第1の容量回路の前記第1の接続端子に対して前記第1の誘導素子の反対側に位置する少なくとも1つの第2の接続端子を通じて前記第1の誘導素子と接続されることと、前記第1及び第2の共振回路が実質的に同等の周波数にチューニングされることと、を特徴とする。本発明は、周波数シンセサイザ及び通信ネットワーク内での使用のためのネットワークノードにも関する。 (もっと読む)

半導体集積回路

【課題】良好な高周波特性を維持しつつ、増幅器の使用周波数帯域切換えが可能な半導体集積回路を提供する。

【解決手段】結合係数k1を有し、互いに並列に接続されるコイルL11及びコイルL12と、コイルL11及びコイルL12に直列に接続されるコイルL13と、コイルL11に並列に接続されるコンデンサC11と、コイルL12に並列に接続されるコンデンサC12と、コイルL11の一端と、コンデンサC11の一端とに接続される入力端子p1と、コイルL12の一端と、コンデンサC12の一端とに接続される入力端子n1と、入力端子p1と、入力端子n1とにそれぞれ逆位相の入力信号を供給する入力信号供給部200とから構成されることを特徴とする半導体集積回路。

(もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

電圧制御発振器

【課題】残留位相雑音特性を劣化させずに発振周波数の広帯域化を実現する電圧制御発振器を提供することを目的とする。

【解決手段】制御電圧印加端子Vc1からの制御電圧に応じて所望の周波数で発振する能動回路を備えた電圧制御発振器であって、前記能動回路は、トランスTSの一次側コイルL5に印加される前記制御電圧によってインダクタンス値が変化する二次側コイルL3を発振維持用のチョークコイルとして用いる。コイルL3のインダクタンス値が変化することで、コイルL3とコンデンサC5との共振周波数を変化させられる。その結果、制御電圧により、共振回路のバリキャップダイオードD1によるリアクタンス特性の変化だけでなく、能動回路のリアクタンス特性を変化させられる。

(もっと読む)

周波数発生のための装置及び方法

広帯域周波数発生器は、フリップチップパッケージ内の同一のダイに配置された異なる周波数帯域のための2つ以上の発振器を有する。2つの発振器の誘導子間の結合は、一方の誘導子がダイに配置され、他方の誘導子がパッケージに配置され、これら誘導子がハンダバンプの直径によって離されることで、減少させられる。弱結合されたこれら誘導子では、一方の発振器の帯域を増加させるために他方の発振器のLCタンク回路の操作をしたり、その逆を行ったりできる。一方の発振器の振動の好ましくないモードを防ぐことは、他方の発振器の粗同調バンクの全容量といった大容量を他方の発振器のLCタンク回路に与えることによって達成され得る。好ましくないモードを防ぐことは、他方の発振器のLCタンクのQファクタを減少させ、タンク回路内の損失を増加させることによっても達成され得る。 (もっと読む)

多重補間LC電圧制御発振器

【課題】周波数が、中心周波数近辺の同調範囲内の周波数で制御される発振信号を形成するLC電圧制御発振器の提供。

【解決手段】位相補間電圧制御発振器は、複数のn個の位相シフトセルA及びn−1レベルの加算セルSを内含する。位相シフトセルAは、共通の入力信号を受理し、各々は、その他の位相シフトセルAとは異なる量だけ入力信号を位相シフトさせる。第1レベルの加算セルSは、少なくとも2つの位相シフトセルAの出力を受信し加算し、残りの加算セルレベルの各々は、加算セルSの先行レベルの出力を受理する。最後のレベルは、位相シフトセルAの共通の入力信号としてフィードバックされる出力信号を生成する単一の加算セルSを含む。

(もっと読む)

高周波発振器

【課題】高価な誘電体共振器やバラクタダイオードを使用することなく、廉価に制作することができ、また回路面積が小さく小型化が可能となるようにする。

【解決手段】誘電体基板1上に形成されたマイクロストリップ線路2において、増幅素子3の入力端のゲートが入力端側線路2aに接続され、出力端のドレインが出力端側線路2bに接続され、ソースが接地電極5に接続される。そして、上記誘電体基板1の裏面の接地面7の中に、空地領域7Eを介して線状の金属パターン8を形成し、この金属パターン8をマイクロストリップ線路2の伝送線路方向に配置することで、この金属パターン8の一方端を入力端側線路2a、他方端を出力側線路2bに容量性結合する。この金属パターン8の結合は、一端のみでもよい。これによれば、増幅素子3からの出力が、容量C1、インダクタンスL、容量C2を通って入力端へ帰還し、発振が行われる。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、円弧ABCと、円弧ABCの端子Aに接続された線路AD’及びAE’と、円弧ABCの端子Cに接続された線路CD’’及びCE’’とを備える。端子CとAはY−Y’に関して線対称、線路CD’’及びCE’’はそれぞれ線路AD’及びAE’と線対称である。円弧ABC、線路AD’および線路CD’’はインダクタ部Ind1を、円弧ABC、線路AE’および線路CE’’はインダクタ部Ind2を構成する。円弧ABCはY−Y’上の点Zを中心点し、線路AD’およびCD’’は、それぞれY−Y’上の点ZDと中心点とした円弧であり、線路AE’およびCE’’は、それぞれY−Y’上の点ZEと中心点とした円弧である。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、可変インダクタ100が備える複数の円弧が共有する中心点Zが1つ存在する。可変インダクタ100は、点Zを中心点とした第1の円周上の円弧で構成された、Y−Y’に関して線対称な第1のインダクタ部Ind1と、点Zを中心点とした第2の円周上の円弧で構成された、Y−Y’に関して線対称な第2のインダクタ部Ind2とを備える。Ind1は、端子D’から端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、端子E’から第端子E’とY−Y’に関して線対称な端子E’’まで延在する。第1の円周の半径r1は、第2の円周の半径r2よりも短い。

(もっと読む)

LC発振器

【課題】発振信号の対称性などの制約が要求される場合においても、その制約を制御する自由度を向上させることができるLC発振器を提供する。

【解決手段】LC発振器は、並列に接続された第1のインダクタおよびキャパシタからなるLCタンク、ならびに、寄生抵抗の影響を打ち消す第1の負性抵抗回路を含む1次側のLC発振器と、相互インダクタンスを発生する相互誘導作用によって第1のインダクタと結合された第2のインダクタおよび第2の負性抵抗回路を含む2次側のLC発振器とを備える。ここで、第1および第2の負性抵抗回路の抵抗値の合計は、寄生抵抗の抵抗値以上であり、逆極性である。

(もっと読む)

発振回路及びテレビジョン信号受信用チューナ

【課題】特別の部品を追加することなく、平衡型の発振回路のC/N特性を改善すること。

【解決手段】VHFローバンド及びVHFハイバンドのテレビジョン信号を受信するための局部発振器を不平衡型の発振回路11,12で構成し、UHFのテレビジョン信号を受信するための局部発振器を平衡型の発振回路13で構成し、VHFバンド用発振回路11,12のC/N特性改善のために設けている抵抗R2の接続点を、UHF用発振回路13に接続した共振回路23のインダクタンス素子23aの一端に接続し、平衡型のUHF用発振回路13に対してラインフィルタ31,32を両側に配置する。

(もっと読む)

デュアルバンド結合VCO

2つの電圧制御発信部VCO1、VCO2を備えるデュアルバンド可能電圧制御発振VCO回路において、電圧制御発振部VCO1、VCO2は、少なくとも2つの結合伝送線TL1、TL2を介して同調および接続され、伝送線[TL1、TL2)は、2つの形態のうち1つにしたがって動作して、同調された発振部(VCO1、VCO2)の組み合わせたインダクタンスと電圧制御発振回路(VCO)の発振周波数とを変動させる。 (もっと読む)

発振器及びそれを用いた通信システム

【課題】テ−ル電流源が無いLCクロスカップル型発振器において、Q値を劣化させずに、良好な位相雑音特性を得る。

【解決手段】発振周波数において、差動増幅器の出力であるQ1,Q2のドレイン端子が接続される共振器3の入力端子102dから差動増幅器の入力であるQ1,Q2のゲート端子が接続される共振器3の出力端子102gへの伝達インピーダンスを、差動増幅器の出力であるQ1,Q2のドレイン端子が接続される共振器3の入力端子102dの駆動点インピーダンスより大きくなるように構成した。上記構成により、発振動作中においてQ1,Q2のゲート端子の発振電圧振幅は、ドレイン端子の発振電圧振幅より大きくなる。これにより、発振動作中のトランジスタが抵抗領域動作になるのを防止し、Q値の劣化を抑えることができる。

(もっと読む)

2バンド発振器

【課題】1つの接地用コンデンサを用いて2つの発振回路の発振トランジスタの接地を行なうとともに各発振周波数帯でインピーダンスを低くすることのできる2バンド発振器を提供すること。

【解決手段】第1の周波数帯で発振する第1の発振トランジスタと、前記第1の周波数帯よりも高い第2の周波数帯で発振する第2の発振トランジスタと、一端が前記第2の発振トランジスタの高周波的接地端子に接続され、他端が接地電極に接続される接地用コンデンサと、一端が前記第1の発振トランジスタの高周波的接地端子に接続され、他端が前記接地用コンデンサの一端に接続されるインダクタとを備えていることを特徴とする。

(もっと読む)

LC発振回路

【課題】位相雑音が小さく低電源電圧動作と高周波信号の発振が可能な、LSI化LC発振回路またはLSI化電圧制御LC発振回路を提供する。

【解決手段】トランジスタ素子の出力端子に負荷としてトランスの1次側インダクタ素子(1次コイル)と固定容量素子または可変容量素子とを並列に接続したものを接続し、該出力端子の信号を反転してトランジスタ素子の入力端子に信号電圧を帰還する形のLC発振回路または電圧制御LC発振回路において、トランジスタ素子の出力端子の電圧波形と同相の電流波形を発生せしめるために、入力端子の電圧を増加させると出力端子に流れる電流が増加するような第2のトランジスタ素子、あるいは複数のトランジスタ素子を用いた可変利得の差動増幅回路を用意し、同相の電流をトランスの1次側インダクタ素子(1次コイル)に結合した2次側インダクタ素子(2次コイル)に流す。

(もっと読む)

1 - 20 / 39

[ Back to top ]