Fターム[5J081LL07]の内容

LC分布定数、CR発振器 (9,854) | 改善手段(発明内容) (679) | 接続の変更 (102)

Fターム[5J081LL07]の下位に属するFターム

切換え (84)

Fターム[5J081LL07]に分類される特許

1 - 18 / 18

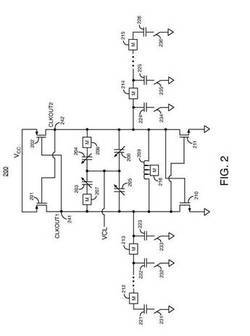

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

発振回路

【課題】簡易な方法で、特性の劣化を抑制し発振周波数を調整することが可能な発振回路を提供すること。

【解決手段】一対の負性抵抗回路と、前記一対の負性抵抗回路にそれぞれ接続された一対の伝送線路14a、14bと、前記一対の伝送線路にそれぞれ対称に設けられ、前記一対の伝送線路の間をボンディングワイヤによって互いに接続可能な一対のパッド40a、40bと、前記一対の負性抵抗回路の出力信号を合成する合成回路と、を有する発振回路。

(もっと読む)

電圧制御発振器

【課題】コルピッツ回路を用いた電圧制御発振器において、帰還部の2つのコンデンサ間とトランジスタのエミッタとを接続する導電線路におけるインダクタンス成分の影響による出力周波数の可変幅(調整幅)の劣化(低下)を抑えることのできる電圧制御発振器を提供すること。

【解決手段】コルピッツ回路を用いたVCOにおいて、帰還部2のコンデンサ22、23について、トランジスタ21のベースから伸びる端子部8(T1)及び前記トランジスタ21のエミッタから伸びる端子部8(T2)が夫々装着されるベース基板5上のベース用端子(接続部7)とエミッタ用端子とを直結するように第1の帰還容量素子(コンデンサ)22を配置すると共に、上記エミッタ用端子とアース用端子(接地電極51)とを直結するように第2の帰還容量素子(コンデンサ)23を配置する。

(もっと読む)

高周波帯電圧制御発振器

【課題】共振回路における発振周波数の公差を低減し、PLL回路に用いられる論理回路の低電圧化傾向の下でも、発振周波数の高周波化を図る。

【解決手段】発振周波数を可変制御するLC同調型の電圧制御発振器において、発振用トランジスタ1のエミッタ側で、接地電位となる一対のスルーホールH1 ,H2 の間に、同一線路長のマイクロストリップ線路からなる2つのショートスタブP1 ,P2 を形成し、これらショートスタブP1 とP2 との間に上記トランジスタ1のエミッタを接続する。即ち、ショートスタブP1 とP2 は、エミッタ接続点を中心に対称となる位置で並列に接続される。また、コンデンサC1 ,C2 でDCカットされたバラクタCvのカソードに、0〜5Vの制御用電圧Vtを印加すると共に、アノードに、基準電圧源6から例えば−5Vの基準電圧を印加する。

(もっと読む)

電圧制御発振回路およびクロック信号生成回路

【課題】制御電圧に対する可変容量の容量値の変化の線形性を向上して位相ノイズを低減した電圧制御発振回路の実現。

【解決手段】制御電圧に応じて発振周波数が変化する発振信号OUT,OUTXを出力する電圧制御発振回路において、印加電圧に応じて容量値が変化する複数の可変容量VAC1-VAC4と、制御電圧を分圧して複数の可変容量に印加する分圧電圧VT,VT1-VT3を生成する分圧電圧生成部R1-R4と、を備える。

(もっと読む)

集積回路

【課題】CR発振回路を構成するコンデンサの充放電切換りタイミングと、論理回路を構成するCMOSインバータに貫通電流が流れるタイミングとをずらすことで、周波数が安定した発振信号を発生する集積回路を提供する。

【解決手段】複数のCMOS素子によって構成された論理回路と、論理回路に、容量素子と抵抗素子の時定数に依存する周波数の発振信号を出力するCR発振回路と、論理回路に入力される発振信号を遅延する遅延回路と、を備え、CR発振回路と電源とを接続する電源配線が、論理回路と電源とを接続する電源配線と接続されている。

(もっと読む)

電圧電流変換回路、及び電圧制御発振回路

【課題】入力電圧に対する出力精度の高い電圧電流変換回路、及び電圧制御発振回路を提供する。

【解決手段】電圧電流変換回路は、入力端子1に入力された入力電圧を電流に変換して、出力する電圧電流変換回路であって、入力端子1に接続されたゲートを有するNMOS4を含み、NMOS4に流れる電流に応じた出力電流を発生する第一電流発生回路11と、ソース、及びドレインと異なる電位となるゲートを有するNMOS8を含み、NMOS8に流れる電流に応じた重畳電流を発生して、NMOS4に供給する第二電流発生回路と、を備えたものである。

(もっと読む)

静磁波発振装置

【課題】静磁波素子発振装置において、発振回路基板12から発生される不要電磁波が、コイル8、9の引き出し線14、15に影響し、発振周波数が不安定となるのを防止した静磁波発振装置を提供する。

【解決手段】発振周波数を調整する電磁コイルの引き出し線を、強磁性体で形成された筐体に設けた空洞17を通して筐体外部へ引き出す構造とする。

(もっと読む)

2出力型水晶発振器

【課題】簡単な回路構成で正弦波信号と矩形波信号を出力可能な2出力型水晶発振器を提供する。

【解決手段】CMOSインバータIC1により構成されるインバータ回路10と、CMOSインバータIC1の入出力間に対して並列に接続される自己バイアス用の第1の帰還抵抗R1と、インバータ回路10の入出力間に対して並列に接続され、少なくとも水晶振動素子20と第2の帰還抵抗R2とを直列接続した直列回路からなる正帰還回路11と、を有し、インバータ回路10の入力側から正弦波信号を出力し、インバータ回路10の出力側から矩形波信号を出力するようにした。

(もっと読む)

共振器の結合回路

【課題】 従来の共振器では、共振周波数の微調整が困難であるという問題点があり、製造工程を煩雑にすることなく、共振器1とカップリングコンデンサ2との間の伝送路Lの長さを可変として共振器のQ値及び発振周波数を微調節することができる共振器の結合回路を提供する。

【解決手段】 共振器1とカップリングコンデンサ2とを接続する伝送線路の伝達方向に沿った長さを可変とした結合回路であり、例えば、共振器1と発振器とを接続する伝送線路3を、複数の隙間によって離散的に形成された複数の伝送路パターン31a〜31dで形成し、当該複数の隙間の内、所望の周波数特性及びQ値となる位置に対応する隙間にカップリングコンデンサ2が搭載され、他の隙間には伝送路パターンを電気的に接続する導通素子4が搭載される共振器の結合回路としている。

(もっと読む)

電圧制御発振器

電圧制御発振器は、それぞれI直交成分およびQ直交成分を生成するための第1の電圧制御発振器コアおよび第2の電圧制御発振器コアを有する。前記電圧制御発振器コアのそれぞれはインダクタを有する。前記インダクタのそれぞれに接続部材が電気的に接続されており、これにより、VCOのIおよびQコアにおいて同じコモンモードレベルに設定される。本発明は、クロスカップリングされたVCOのIコアとQコアで、同じコモンモードレベルが確実に使用されるようにする簡便な方法を提供するという利点を有し、特に高い動作周波数において有利である。また、本発明は、スタートアップの潜在的な問題を解決する利点を有し、デバイスを微細化した結果、不整合が大きくなることが多いため、130nmCMOSなどの小さな形状のプロセスで設計する場合により顕著となるデバイスの不整合効果に対する感受性を低減させる。

【代表図】図3  (もっと読む)

(もっと読む)

カップリングキャパシタを備える4位相電圧制御発振器

【課題】カップリングキャパシタを備える4位相電圧制御発振器を提供する。

【解決手段】4位相電圧制御発振器は、位相の互いに異なる第1、第2位相信号を出力する第1遅延セル610、及びそれぞれ前記第1及び第2位相信号に直交し、互いに異なる位相を有する第3、第4位相信号を出力する第2遅延セル630を備える。第1、第2遅延セルは、第1、第2差動電圧制御発振器615、635と、これにそれぞれ接続された第1及び第2カップリングトランジスタと前記第1、第2及び第3、第4カップリングトランジスタにそれぞれ並列に接続されて接地された第1、第2カップリングキャパシタが備えられて、前記出力される位相信号をカップリングさせる第1、第2カップリング部620、640とを備える。

(もっと読む)

水晶発振器

【課題】1つのICで効率良く、搭載されるセットの仕様や周波数に対応できる水晶発振器を提供する。

【解決手段】発振器1の出力側を、出力側が第1の抵抗7に接続されたインバータ2の入力側と第2の抵抗8の一端とに接続し、第1の抵抗7の他端を第1の容量9の一端と第1のトランジスタ3の入力側とに接続し、第1の容量9の他端を第1のスイッチ11の一端に接続し、第1のスイッチ11の他端を接地し、前記第2の抵抗8の他端を第2の容量10の一端と第2のトランジスタ4の入力側とに接続し、第2の容量10の他端を第2のスイッチ12の一端に接続し、第2のスイッチ12の他端を接地し、第1のトランジスタ3の出力側と第2のトランジスタ4の出力側とを発振出力端子5に接続し、第1のスイッチ11と第2のスイッチ12とを記憶装置13にて制御する。

(もっと読む)

高周波モジュール

【課題】基板の誘電体層と電極層の僅かな焼成縮率の差により基板焼成後、基板に反りが発生する。この反りが大きくなると、印刷性が悪くなり、かつ印刷するパターンかすれや、にじみが発生し、場合によっては印刷時にスクリーンが破れたりする。

【解決手段】少なくとも、ストリップライン導体7と、複数のGND電極と、複数のコンデンサを内蔵すると共に、前記ストリップライン導体7に対し、積層方向の両側に、GND電極3、4を配置してトリプレート型ストリップライン導体共振器を構成した高周波モジュールにおいて、前記トリプレート型ストリップライン導体共振器に対し、積層方向の上側(部品搭載面側)と下側(底面側)の双方に、それぞれGND電極3、4からなるコンデンサを配置した。

(もっと読む)

通信用半導体集積回路装置および無線通信システム

【課題】通信用半導体集積回路装置および無線通信システムにおけるノイズ耐性を向上させる。

【解決手段】例えば、変調/復調等を行う半導体チップ上に、交差結合型のトランジスタ対を含む差動型発振回路部DF_VCOと、トランジスタ対の共通ノード側に接続される内部パッドP1,P4と、トランジスタ対の差動出力ノード側に接続される内部パッドP2,P3とを設ける。P1〜P4は、それぞれボンディングワイヤBWを介して外部リード端子LD1〜LD4に接続する。LD2,LD3には、それぞれチップ外付け部品となる外部負荷素子LOAD1,LOAD2を接続し、LD1,LD4には、固定電圧を印加する。このような構成において、外部リード端子では、LD2とLD3を隣接して配置し、LD2とLD3を挟むようにLD1とLD4を配置する。

(もっと読む)

半導体集積回路装置

【課題】制御電圧の狭い変化範囲で安定に動作する電圧制御発振器を提供する。

【解決手段】電圧制御可能な可変容量回路12と、インダクタを有するインダクタ回路11と、負性抵抗回路13と、補正電圧を出力する容量制御回路14と、を備える。可変容量回路12とインダクタ回路11と負性抵抗回路13とを並列接続して発振回路を構成する。容量制御回路14は、発振回路における温度変動および/または電源電圧変動に対応して出力される補正電圧によって可変容量回路12におけるキャパシタンスを補正するように制御する。

(もっと読む)

発振回路

【課題】 広帯域発振周波数を得る。

【解決手段】 バイポーラトランジスタQ1のベースをバイポーラトランジスタQ2のコレクタに接続する。バイポーラトランジスタQ2のベースをバイポーラトランジスタQ1のコレクタに接続する。Q1と電源間に抵抗R1、Q2と電源間に抵抗R2を接続する。バイポーラトランジスタQ1、Q2のエミッタ間にキャパシタC1、C2,インダクタL1を直列に接続する。C1,C2のキャパシタ値を変えることで広帯域発振周波数範囲を得る。発振周波数範囲は抵抗R1,R2を調節することで、変えることができる。Cv1,Cv2は可変キャパシタで、VCP電圧によりキャパシタ値を変える。

(もっと読む)

発振回路モジュール

【課題】 信号出力部のトランジスタのコレクタ−ベース間のアイソレーションを確保して、出力レベルおよび周波数負荷安定度を高めた発振回路モジュールを構成する。

【解決手段】 第1の電圧制御発振回路VCO1のバッファ用トランジスタQ12のベースに接続したベースバイアス回路(R11,R12,R13)がスイッチSW1を介して接続される外部電源端子VB2と、トランジスタQ12のコレクタが接続される外部電源端子VB1とを異ならせる。

(もっと読む)

1 - 18 / 18

[ Back to top ]