Fターム[5J098AA03]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 半導体素子 (443) | FET (224)

Fターム[5J098AA03]に分類される特許

1 - 20 / 224

信号等化器

スプリッタ回路およびチューナーシステム

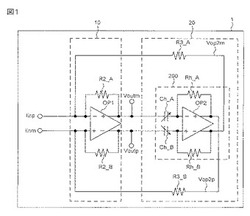

フィルタ回路及び受信装置

【課題】低雑音かつ低カットオフ周波数のフィルタ回路をより小面積で実現する。

【解決手段】フィルタ回路(1〜5)は、入力端子(Iinp、Iinm、(Vinp、Vinm))に供給された入力信号を受け、信号を増幅して出力端子(Voutm、Voutp)に出力する第1回路(10、11)と、第1容量素子(Ch_A、Ch_B)を介して前記第1回路の出力信号を入力する第1差動増幅回路(OP2)と、前記第1差動増幅回路(OP2)の入出力間に負帰還経路を形成する第1抵抗素子(Rh_A、Ch_B)と、前記第1差動増幅回路の出力と前記第1回路の入力との間に負帰還経路を形成する第2抵抗素子(R3_A、R3_B)とを有する。

(もっと読む)

アクティブインダクタ

【課題】アクティブインダクタを提供する。

【解決手段】ソース、ドレイン、及びゲートを含むpMOSトランジスタであって、前記pMOSトランジスタの前記ソースが電源Vddと接続し、抵抗Rの一端が前記pMOSトランジスタの前記ゲートに接続し、前記抵抗Rの他端が前記pMOSトランジスタの前記ドレインに接続している回路において、電源からの直流バイアスの略フルレンジに対して、インダクテイブインピーダンスを生成し、インダクタの特性を有する。

(もっと読む)

ローパスフィルタ回路

【課題】能動素子に発生するオフセット電圧の影響を少なくすることのできるローパスフィルタ回路を提供する。

【解決手段】実施形態のローパスフィルタ回路1は、抵抗Rと、一端が接地端子に接続されたキャパシタCと、Gmアンプ11と、Gmアンプ12とを備える。Gmアンプ11は、非反転入力端子にキャパシタCの他端が接続され反転入力端子に自身の出力端子OT1が接続された入力差動対DP1を有し、出力端子OT1に抵抗Rが接続される。Gmアンプ12は、非反転入力端子にGmアンプ11の出力端子OT1が接続され反転入力端子に自身の出力端子OT2が接続された入力差動対DP2を有し、出力端子OT2にキャパシタCの他端が接続される。

(もっと読む)

バンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路

【課題】センター周波数を実質的に変化させずに帯域幅を可変することが可能なバンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路を提供すること

【解決手段】本発明にかかる集積回路106は、楕円関数型のバンドパスフィルタ回路100及び制御部105を備える。バンドパスフィルタ回路100は、センター周波数f1を設定する第1LCフィルタ回路部101及び第4LCフィルタ回路部104、共振周波数f2、f3をそれぞれ設定する第2LCフィルタ回路部102、第3LCフィルタ回路部103を備える。前記制御部105は、第2LCフィルタ回路部102が設定するインダクタンス値L2、容量値C2及び第3LCフィルタ回路部103が設定するインダクタンス値L3、容量値C3を可変させて、共振周波数f2及びf3を、互いに増減が逆になるように変化させる。

(もっと読む)

半導体装置

【課題】省面積化されたローパスフィルタを備える半導体装置を提供する。

【解決手段】第1のノードと第2のノードとの間に接続され、印加される電圧に応じて内部容量が変化する可変容量素子と、第1のノードと第2のノードとの間に可変容量素子と並列に接続される電圧増幅部とを備え、電圧増幅部は、第1のノードと電気的に接続される増幅器と、増幅器の出力の電圧をシフトさせるレベルシフト回路とを含み、レベルシフト回路の出力は第2のノードと電気的に接続される。

(もっと読む)

分配回路、送信用フェーズドアレイアンテナ回路、合成回路及び受信用フェーズドアレイアンテナ回路

【課題】入力信号を複数の信号に低損失で分配することができる分配回路を提供することを課題とする。

【解決手段】分配回路は、信号入力ノードに直列接続される複数のインダクタ(401〜40n+1)と、入力容量を有する入力端子及び出力端子を有し、前記複数のインダクタのそれぞれの間に前記入力端子が接続され、前記入力端子に入力される信号を増幅して前記出力端子から出力する複数の増幅素子(421〜42n)と、前記複数の増幅素子の出力端子と複数の信号出力ノードとの間にそれぞれ接続される複数の整合回路(431〜43n)とを有する。

(もっと読む)

可変容量回路

【課題】キャパシタが破壊されずAC信号が歪まないようにした可変容量回路を提供する。

【解決手段】可変容量回路は,基準電位を中心とする交流信号が印加される所定ノードと,所定ノードに接続される第1のキャパシタと,第1のキャパシタと基準電位との間に接続された第2のキャパシタと,第2のキャパシタと第1のキャパシタとの間の第1のノードと基準電位との間に設けられた第3のキャパシタ及び容量制御用のトランジスタと,第3のキャパシタとトランジスタとの間の第2のノードに第1のバイアス電圧を印加するバイアス回路とを有する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

差動単相変換回路

【課題】温度やプロセス条件のばらつきの影響を受けず,高いCMRR特性を有する差動単相変換回路を提供する。

【解決手段】差動単相変換回路は,逆相関係にある一対の差動信号のうちの第一の差動信号を増幅するとともに,第一の差動信号を同相で出力する第一の増幅回路と,差動信号のうちの第二の差動信号を増幅するとともに,第二の差動信号の位相を反転させて出力する第二の増幅回路と,第一の増幅回路からの出力信号と第二の増幅回路からの出力信号を合成して出力する出力端子とを備え,第二の増幅回路は,複数のトランジスタをカスコード接続したカスコード回路である。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の遮断周波数精度を悪化させること無く、回路規模を低減することができるフィルタ回路を提供する。

【解決手段】駆動電流生成回路303は、容量C1に第1の基準電流を一定期間充電することにより生成される充電電圧を用いて、容量C1と第1の基準電流の比に比例した第1の駆動電流を生成する。OTA301は、正入力端子と負入力端子間の電位差に応じて、第1の駆動電流から、容量C1と第1の基準電流の比に逆比例した第2の駆動電流を生成して電圧に変換し、この電圧に応じて第2の基準電流を分配する。OTA301は、第2の基準電流を分配した電流と同量の電流を折り返して供給するカレントミラー回路を有し、正入力端子と負入力端子間の電位差に応じた電流をカレントミラー回路により折り返して負荷容量302に供給する。

(もっと読む)

可変減衰器

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

アクティブフィルタ

【課題】フィルタのQ値が変動することがないアクティブフィルタを提供する。

【解決手段】位相容量素子を含む演算増幅器、フィルタ用抵抗素子、フィルタ用容量素子、バイアス回路を含むアクティブフィルタにおいて、バイアス回路を、ゲート同士が接続されるMOSTr41、42、MOSTr41とドレイン同士が接続されるMOSTr43、MOSTr44とゲート同士が接続され、MOSTr42とドレイン同士が接続されるMOSTr44、MOSTr41またはMOSTr42のうちのいずれか1つのソースに接続される抵抗素子45、MOSTr41のドレインに接続される出力端子46またはMOSTr44のドレインに接続される出力端子47によって構成し、抵抗素子45を、フィルタ用抵抗素子と同じプロセス条件で製造し、位相補償容量素子をフィルタ用容量素子と同じプロセス条件で製造する。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

ロードスイッチ

【課題】小さい入力−出力差分電圧を維持し、既定の応答を提供する半導体装置、回路、そしてAC及びDCロードスイッチを提供する。

【解決手段】ロードスイッチは、入力端子及び出力端子へ結合された通過素子を含み得る。通過素子は制御端子を含み、制御端子は通過素子の応答を制御し得る。ロードスイッチは第1のループを含み得る。第1のループは制御端子へ結合され、通過素子との高インピーダンスを維持しながら入力端子及び出力端子間の電圧降下を制御するように構成される。ロードスイッチは第2のループを含み得る。第2のループは制御端子へ結合され、既定のフィルタ応答を入力端子から提供するように構成される。既定の応答は、低域通過応答、高域通過応答、又は帯域通過応答であり得る。応答の通過帯域及び/又は阻止帯域は、プログラムされ得る。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

1 - 20 / 224

[ Back to top ]