Fターム[5J098AC14]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変要素 (423) | バイポーラトランジスタ、FET (46)

Fターム[5J098AC14]に分類される特許

1 - 20 / 46

ポジショナ

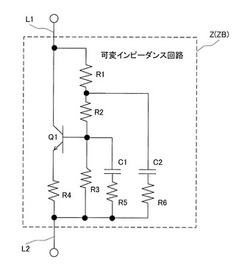

【課題】低周波のノイズの影響に強いポジショナを提供する。

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

可変容量回路

【課題】キャパシタが破壊されずAC信号が歪まないようにした可変容量回路を提供する。

【解決手段】可変容量回路は,基準電位を中心とする交流信号が印加される所定ノードと,所定ノードに接続される第1のキャパシタと,第1のキャパシタと基準電位との間に接続された第2のキャパシタと,第2のキャパシタと第1のキャパシタとの間の第1のノードと基準電位との間に設けられた第3のキャパシタ及び容量制御用のトランジスタと,第3のキャパシタとトランジスタとの間の第2のノードに第1のバイアス電圧を印加するバイアス回路とを有する。

(もっと読む)

可変減衰器

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

可変利得減衰器

【課題】特性劣化を引き起こす容量結合をしないで次段増幅器と接続でき、非常に広い周波数範囲に渡って同様の特性で、入力される高周波信号の利得を適切に減衰させて次段増幅器に伝達できる可変利得減衰器を提供すること。

【解決手段】高周波信号を入力するための入力ポート18と、高周波信号を出力するための出力ポート19と、外部からバイアス電圧を印加するためのバイアスポート20と、入力ポートと出力ポートとの間に直列に接続され、それぞれ同等の制御電圧により利得が制御されるMOSトランジスタ10,11と、MOSトランジスタ10,11の直列接続端とグランドとの間に接続され、MOSトランジスタ10,11に適用する制御電圧とは逆特性の制御電圧によって利得が制御されるMOSトランジスタ12とを備え、3つのMOSトランジスタの各バックゲート端子は共通にバイアスポートに接続されている。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

可変抵抗制御回路及び可変抵抗器

【課題】抵抗を広い範囲で変化させることができる可変抵抗制御回路及び可変抵抗器を提供すること

【解決手段】本発明にかかる可変抵抗制御回路は、電源10と、電源10よりも低い電位を有する電源11との間に設けられ、電源10と接続される抵抗21と、電源10と、電源11との間に設けられ、前記抵抗21と直列に接続されるMOSトランジスタ31と、電源10と、電源11との間に設けられ、前記MOSトランジスタ31と直列に接続されるMOSトランジスタ32と、抵抗21とMOSトランジスタ31との節点における電圧と、制御電圧とに基づいて、MOSトランジスタ32にゲート電圧を出力するオペアンプ41とを備え、オペアンプ41は、ゲート電圧に基づいて抵抗値が制御される外部の可変抵抗に対してゲート電圧を出力するものである。

(もっと読む)

増幅回路、ジャイレータ回路、信号を増幅するためのフィルタ・デバイス及び方法

【課題】周波数に依存しない伝達特性が改善された増幅器、及びジャイレータ回路の提供。

【解決手段】位相シフタ部2に接続されたトランスコンダクタ・デバイス1を備えた増幅回路A1。位相シフタ部2は、位相シフトが調整可能で、入力信号の周波数に少なくとも部分的に依存するインピーダンスを有している。使用時に、調整可能な位相シフトは、トランスコンダクタ・デバイス1の位相シフトと実質的に反対の値となる様に調整され、実施形態として、位相シフタ部2は、キャパシタ・デバイスCと可調抵抗デバイスRとを含み、可調抵抗デバイスRは、抵抗値制御信号を受信する入力接点Rin、キャパシタ・デバイスに接続された第1の出力接点Rout1、及びトランスコンダクタ・デバイスに接続された第2の出力接点Rout2を有する増幅デバイスRを含み、増幅回路A1は更に、抵抗値制御信号を増幅デバイスの入力接点に供給する制御デバイスを備えている。

(もっと読む)

移相回路

【課題】低損失化を図ることができるとともに、小形化を図ることができる移相回路を得る。

【解決手段】第1の入出力端子1aと、第2の入出力端子1bと、第1の入出力端子1aと第2の入出力端子1bの間に接続された第1のスイッチング素子2aと、第1の入出力端子1aに一端が接続された第1のキャパシタ3aと、第2の入出力端子1bに一端が接続された第2のキャパシタ3bと、第1及び第2のキャパシタ3a、3bの他端とグランド4の間に接続された第2のスイッチング素子2bとを設けた。

(もっと読む)

フィルタ回路及びその制御方法

【課題】CMCの正極側巻線と負極側巻線に流れる電流を等しくし、所望の特性を得るようにしたフィルタ回路の提供。

【解決手段】コモンモードノイズフィルタの正極側巻線と、負極側巻線に流れる電流を監視する手段(2、3)と、監視結果に基づき、正極側巻線と負極側巻線が互いに等しくなるように調整する手段(4、5、6)を備える。

(もっと読む)

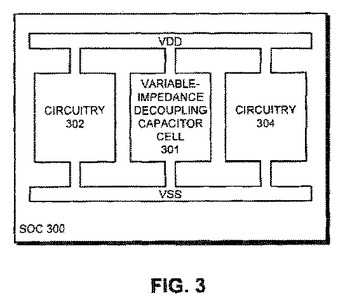

可変インピーダンスゲートデカップリングセル

本発明の実施形態は、電力レールと、接地レールとを含む、電力システム内のノイズを制御するシステムを提供する。システムは、電力レールと接地レールとの間でデカップリングコンデンサと直列に連結される、MOSトランジスタと、MOSトランジスタおよびデカップリングコンデンサと並列に電力レールに連結される、誘導パッケージング接続とを含む。MOSトランジスタ、デカップリングコンデンサ、および誘導パッケージング接続の組み合わせは、共振回路を形成する。動作中、システムは、電力レール上のVdd信号中にノイズが存在するかを判定する。Vdd信号中に存在するノイズに基づき、システムは、他の周波数でのスイッチングノイズの不必要な増加を引き起こすことなく、共振回路の関心周波数(ωinterest)付近の周波数範囲内のノイズを低減するように、MOSトランジスタのインピーダンスを調整する。  (もっと読む)

(もっと読む)

アッテネータ

【課題】アッテネータの減衰特性を電圧の値によって調整していたため、降圧回路などの電圧供給用回路が新たに必要となるアッテネータの回路規模が増大するとともに、熱雑音やショットノイズがアッテネータの出力信号に混入する。

【解決手段】直列接続された第1および第2回路と、これら第1および第2回路との間にシャント状に接続された第3回とを含むT型の二端子対網回路と、からなるアッテネータに対し、第1および第2回路の間に第3回路とは別にシャント容量を接続する。

(もっと読む)

可変減衰器及び無線通信装置

【課題】高周波で使用する1段当たりの可変減衰量が大きい可変減衰器を提供する。

【解決手段】可変減衰器は、ゲート、ドレイン、ソース、ボディを有するMOSFET12と、減衰量制御回路14と、温度補償回路21とを備える。減衰量制御回路14は、ゲート、及びドレイン、ソースに制御電圧を与える。温度補償回路21は、ボディに温度補償電圧を与える。入力端子、出力端子は、それぞれMOSFET12のドレイン、ソースに接続する構成をとる。温度補償回路21は、MOSFET12の動作温度に応じて、ボディに供給する電圧を制御して、ホディ電圧とゲート電圧との関係で入力端子及び出力端子間に流れる電流の抵抗値を調整する。

(もっと読む)

温度補償バイアス回路、高周波増幅器及び高周波減衰器

【課題】負電圧で動作可能であり、かつ出力電圧の温度変化が大きな特性が得られる温度補償バイアス回路を提供する。

【解決手段】プラス側電圧印加端子3にドレイン端子が接続し、温度が高くなるにつれてドレイン電流が増加する傾向を示す閾値電圧Vth付近の電圧範囲のゲート−ソース間電圧Vgsが印加されるトランジスタ4と、一端がトランジスタ4のソース端子に接続し、他端が抵抗6の一端に接続するダイオード5と、一端が抵抗6の他端に接続すると共に、他端がマイナス側電圧印加端子1に接続し、トランジスタ4のゲート端子が抵抗6との接続部に接続する抵抗7と、ダイオード5と抵抗6との接続部に接続して出力電圧が取り出される出力電圧端子2とを備えた。

(もっと読む)

インピーダンス調整回路

【課題】 DIMMに実装されているSDRAMのOCDインピーダンス測定・調整が短時間で実行でき、設計が容易なインピーダンス調整回路を提供する。

【解決手段】 調整コードに対応してインピーダンスが可変の出力ドライバを有する、複数のメモリチップD0〜D7をランク選択信号とデータマスク信号の組合せにより選択して、インピーダンスの測定及び調整を行うインピーダンス調整回路において、異なるランクのメモリチップD0〜D7にランク選択信号をそれぞれ出力する複数のランク選択回路31,32と、ランクごとにメモリチップを選択するデータマスク信号をそれぞれ出力する複数のデータマスク選択回路41〜48とを備えたことを特徴とする。

(もっと読む)

マルチバイブレータ型発振回路

【課題】2次以降の高調波を低減させた低歪の正弦波出力が得られ、また発振周波数を変えた場合でも、基本波を減衰させることなく、低歪の正弦波出力が得られるようにする。

【解決手段】マルチバイブレータ回路10を有するマルチバイブレータ型発振回路で、マルチバイブレータ回路10の出力側に、その出力電圧波形の高調波を低減する第1及び第2の電流可変(n次)フィルタ回路20,22を接続し、このフィルタ回路20,22により、高調波を減衰させた低歪の正弦波出力を得る。また、マルチバイブレータ回路10の発振周波数設定用のバイアス電流Ix2,Ix3と連動する連動電流をトランジスタQ17,Q18にて抽出し、この連動電流によって、上記フィルタ回路20,22のカットオフ周波数を変化させ、基本波の減衰をなくす。

(もっと読む)

可変インピーダンス回路、それを用いた可変インピーダンスシステム、フィルタ回路、増幅器、通信システム

【課題】可変インピーダンス回路の歪を低減したい。

【解決手段】第1トランジスタM1は、差動入力信号の一方を受ける第1端子と、インピーダンスを変化させるための制御信号を受ける第2端子と、第2トランジスタと接続された第3端子と、基板に電位を供給するための第4端子とを含む。第2トランジスタM2は、差動入力信号の他方を受ける第5端子と、制御信号を受ける第6端子と、第1トランジスタと接続された第7端子と、基板に電位を供給するための第8端子とを含む。第3端子、第4端子、第7端子および第8端子が接続される。

(もっと読む)

インピーダンス調整回路およびインピーダンス調整方法

【課題】半導体装置と外部抵抗の間の線路に存在する寄生抵抗分を特別の回路を設けることなく補正することのできるインピーダンス調整回路およびインピーダンス調整方法を得ること。

【解決手段】LSIケース201の外部には、ケースピンを介してインピーダンス設定用のクランプ抵抗208と、これと電位を比較するための第1および第2の参照電圧生成抵抗221、222が接続されている。第1および第2の参照電圧生成抵抗221、222の間には、LSI202内の折り返し線225を経由する形で他の線路と同一幅の2本ずつの線路の寄生抵抗分からなる抵抗回路224が設けられており、調整に悪影響となる他の線路の寄生抵抗分をキャンセルする。このため、コンパレータ211の比較結果を使用して制御回路205はインピーダンス調整用出力バッファ203を高精度に調整可能である。

(もっと読む)

1 - 20 / 46

[ Back to top ]