Fターム[5J098AC19]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変要素 (423) | スイッチ (137)

Fターム[5J098AC19]の下位に属するFターム

電子的スイッチ (97)

Fターム[5J098AC19]に分類される特許

1 - 20 / 40

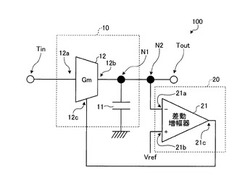

フィルタ装置

【課題】フィルタ回路の通過帯域特性を一定にするための回路の規模を低減できるフィルタ装置を得ること。

【解決手段】フィルタ装置は、半導体集積回路で形成されたフィルタ装置であって、フィルタ回路と、前記フィルタ回路の出力電圧と、目標の周波数通過帯域に対応した参照電圧との差に基づき、前記フィルタ回路の周波数通過帯域が前記目標の周波数通過帯域になるように調整する調整回路とを備えている。

(もっと読む)

適応ノッチフィルタ、及びノッチフィルタのパラメタ調整方法

【課題】制御帯域を広げたときに生じる振動周波数成分を抑制するよう自動的にノッチフィルタを調整する。

【解決手段】適応ノッチフィルタは、共振が生じ得る制御対象への制御入力を生成するための信号に含まれる当該制御対象の固有振動数成分を抑制するためのノッチフィルタと、ノッチフィルタの中心周波数及びノッチ幅を含むパラメタを調整するためのパラメタ調整部と、を備える。パラメタ調整部は、制御対象の制御帯域を広げたときに生じた振動周波数成分とノッチフィルタの中心周波数との関係に応じて、調整されるべきノッチフィルタのパラメタを選択する。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルター10は、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプをOP1と、第1の入力キャパシターC1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、前記ハイパスフィルター10の入力信号VINが供給され、第2の入力端に、出力端から帰還された帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルター10の出力信号VOUTが出力される。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルターは、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプOP1と、第1の入力キャパシターC1と、出力端から帰還される帰還信号に対してハイパスフィルターのゲイン調整を行うゲイン調整回路GA1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、ハイパスフィルターの入力信号VINが供給され、第2の入力端に、帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルターの出力信号VOUTが出力される。

(もっと読む)

gm−Cフィルタの周波数補正方法と該方法を使うことができる装置

【課題】gm−Cフィルタの周波数補正方法を提供する。

【解決手段】周波数補正方法は、周波数補正回路が、gm−Cオシレータから出力され、工程変化を表わすオシレーション信号の周波数と基準コードとによって、gm−Cフィルタのカットオフ周波数を調節することができる補正コードを生成する段階と、周波数補正回路が生成された補正コードが、基準コードの範囲内に属するか否かを判断する段階と、周波数補正回路が、判断結果によって生成された補正コードをgm−Cフィルタに出力するか、またはgm−Cオシレータのトランスコンダクタンスとgm−Cフィルタのトランスコンダクタンスとを調節するための可変電流を生成する段階と、を含む。

(もっと読む)

フィルタ自動調整回路及び方法並びに無線通信装置

【課題】調整機能を有する複数のフィルタにおいて、高い調整精度を有し、かつ低消費電流化が容易なフィルタのバラツキ調整を可能にする。

【解決手段】位相差検出器104により、複数のモードの切り替えを有する基準フィルタ103における前後の位相差をカウンタ105にてカウントし、基準フィルタ103のバラツキを検出する。その際、主フィルタ109を調整する時には基準フィルタ103を第1のモードに設定し、主フィルタ111を調整する時には基準フィルタ103を第2のモードに設定することで、複数の主フィルタ109,111に対して、より精度の高いフィルタ調整を行う。検出結果から得られる主フィルタ109の調整結果はレジスタ108に、主フィルタ111の調整結果はレジスタ110に保持し、調整後はフィルタ調整に関する部材をすべて動作停止し、低消費電力化を図る。

(もっと読む)

イコライザ回路及び受信装置

【課題】回路を構成する素子の特性バラツキの影響を受けることなく、信号伝送で減衰した成分が補償された良好な信号が得られるイコライザ回路を提供する。

【解決手段】入力される電圧信号をトランスコンダクタンスにより電流に変換して、その出力に応じて各容量負荷の充放電を行い、容量負荷毎に期間を異ならせて、電圧信号に応じた電流による容量負荷からの電荷の引き抜きと電圧信号に応じた電流による容量負荷への電荷の注入とを行うようにして、デジタルフィルタにおけるハイパスフィルタの機能を実現し、素子の特性バラツキの影響を受けることなくイコライズ機能を実現できるようにする。

(もっと読む)

回路公差を調節するための回路と方法

【課題】周波数に敏感な回路のための周波数応答調節器、及び回路の周波数応答を調節する方法を提供する。

【解決手段】周波数に敏感な回路の充電状態を第1の電圧として測定し出力する時定数センサと、第1の電圧をサンプルし、第1の電圧を変換して得られる結果である第2の電圧を出力する変換器と、トリミング要素アレイと、トリミング要素アレイから少なくとも1つのトリミング要素を選択するために第2の電圧を利用するセレクタとを含んでいる。この方法は、回路の時定数を感知することと、この感知を第1の電圧として出力することと、第1の電圧を、固定された間隔にわたってサンプルすることと、サンプルした第1の電圧を、第2の電圧に変換することと、第2の電圧を使ってトリミング要素アレイから、少なくとも1つのトリミング要素を選択する。

(もっと読む)

アクティブフィルタ回路

【課題】アナログ式のアクティブフィルタ回路において、起動時に出力が安定するまでの時間の短縮を実現する。

【解決手段】アクティブフィルタ回路は、第1抵抗R1と、演算増幅器3と、第2抵抗Rfと、キャパシタCfと、スイッチSW1とを具備する。演算増幅器3は、+入力端子に基準電圧Vrefを供給され、−入力端子に第1抵抗R1を介して入力電圧Vinを供給される。第2抵抗Rfは、一端を演算増幅器3の出力端子に、他端を−入力端子にそれぞれ接続されている。キャパシタCfは、一端を出力端子に接続されている。スイッチSW1は、起動時にキャパシタCfの他端を+入力端子に接続し、所定時間経過後にキャパシタCfの他端を−入力端子に接続するように切り替わる。

(もっと読む)

フィルタ回路及び通信装置

【課題】電荷の移動に伴う過渡現象が出力に与える影響を抑止すること。

【解決手段】入力端に入力された電圧信号を電流信号に変換するトランスコンダクタンスアンプ102と、複数のキャパシタから構成され、トランスコンダクタンスアンプ102から出力された電流信号が周期毎に各キャパシタへ順次に入力されるキャパシタ集合体と、電流信号が入力された1群のキャパシタを互いに接続し、当該1群のキャパシタに蓄積された電荷を加算するシェアスイッチS1aS〜S4aS,S1bS〜S4bSと、シェアスイッチS1aS〜S4aS,S1bS〜S4bSにより電荷が加算された後、1群のキャパシタのうちの少なくとも1つのキャパシタを出力端に接続するダンプスイッチS1aD〜S4aDと、を備える。

(もっと読む)

フィルタ回路および通信装置

【課題】フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能なフィルタ回路を提供すること。

【解決手段】フライングキャパシタと、フライングキャパシタの入力端と出力端との間に、フライングキャパシタと並列に設けられるキャパシタと、を備えるフィルタ回路は提供される。フライングキャパシタの入力端と出力端との間に所定の容量を有するキャパシタを設けることで、フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能となる。

(もっと読む)

位相同期回路におけるループフィルタ

【課題】C/Nを改善することができる位相同期回路におけるループフィルタを提供する。

【解決手段】本発明の位相同期回路におけるループフィルタ1は、増幅回路2、第1のローパスフィルタ3、第2のローパスフィルタ4、電圧供給回路17、スイッチング素子5を備える。第2のローパスフィルタ4は、増幅回路2の出力端子2aと第1のローパスフィルタ3との間に接続され、バイアス電圧を供給する電圧供給回路17にも接続される。スイッチング素子5は、第2のローパスフィルタ4の接続状態を制御し、増幅回路2から出力された制御電圧が所定の電圧以下に降下したときに自動的にオンとなるように形成される。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

フィルタ回路および無線機器

【課題】中心周波数を調整する周波数チューニングが容易に行えるフィルタ回路を提供する。

【解決手段】

本発明に係るフィルタ回路10は、チューニング時、スイッチ回路4を導通状態として、トランスコンダクタンス回路6を含むフィードバックループを有する発振回路8を構成する。発振回路8は、スイッチ回路4によりLCRタンク回路2をバイパスして、LCRタンク回路1とインダクタ3とを負荷回路としている。上記フィードバックループは、発振回路8の出力をトランスコンダクタンス回路6に入力する。スイッチ回路4を用いて以上のように発振回路8を構成することで、フィルタ回路10の中心周波数と発振回路8の発振周波数とが同一となる。それゆえ、特許文献1に開示されている自動チューニング技術を用いて容易に周波数チューニングを行うことができる。

(もっと読む)

フィルタ装置および受信装置

【課題】回路素子数を低減し、回路面積の低減,回路電流の減少を実現する。

【解決手段】スイッチSW10は、増幅器51の反転出力端から増幅器50の反転入力端に至る経路に挿入され、スイッチSW11は、増幅器51の非反転出力端から増幅器50の非反転入力端に至る経路に挿入され、スイッチSW12は、増幅器50の非反転出力端から増幅器51の反転入力端に至る経路に挿入され、スイッチSW13は、増幅器50の反転出力端から増幅器51の非反転入力端に至る経路に挿入され、制御信号S14に応答してスイッチ(SW10,SW11,SW12,SW13)のON/OFFを制御し、当該経路を導通/遮断制御することにより、帯域制限すべき帯域をLow-IF方式の帯域またはZero-IF方式の帯域に切替える。

(もっと読む)

半導体装置

【課題】半導体装置の受信部に小占有面積と消費電力が小さく且つ良好な受信品質とを得る。

【解決手段】受信して周波数変換された信号のDCオフセットを除去するハイパスフィルタ(10,15)は、CRフィルタを有し、CRフィルタの抵抗素子に流れる電流を選択的に増やすことによってハイパスフィルタの入力インピーダンスを大きくするブートストラップ回路(36)を備える。WCDMA又はHSDPA方式に応じてハイパスフィルタの遮断周波数を切換える。WCDMAによる受信のときはブートストラップ回路を非活性として遮断周波数を高くする。HSDPAによる受信のときはブートストラップ回路を活性として遮断周波数を低くする。CRフィルタ回路の抵抗素子に電流を流すブートストラップ回路を採用することによりCRフィルタ回路のチップ占有面積の増大を抑えて低いカットオフ周波数を実現することができる。

(もっと読む)

フィルタ回路及びこれを用いた通信用半導体装置

【課題】本発明は、所定の近傍妨害波除去比を確保しつつ、回路構成の規模を抑え占有面積を削減できるフィルタ回路及びこれを用いた通信用半導体装置を提供することを目的とする。

【解決手段】本発明は、アナログ信号をフィルタリングするフィルタ回路4である。そして、当該フィルタ回路4は、アナログ信号を電圧から電流に変換する電圧電流変換回路41と、電圧電流変換回路41で変換された電流を複数のキャパシタにチャージ又はディスチャージすることで信号処理を行うキャパシタアレイ43とを備えている。さらに、キャパシタアレイ43は、複数のキャパシタを複数段に分け、前段のキャパシタにおいて平均化した信号を次段のキャパシタに順次蓄積させる処理を行う。

(もっと読む)

信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法

【課題】信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法を提供すること。

【解決手段】信号レベルが第1のレベルと第2のレベルの間で遷移し、各々が同一の周波数および所定の位相の差分を有する複数の基礎信号であって、任意の基礎信号の信号レベルが第1のレベルである期間、および該任意の基礎信号に対して前記所定の位相遅れを有する次の基礎信号の信号レベルが第1のレベルである期間が重複する複数の基礎信号を生成する多相発振部と、前記各基礎信号の第1のレベルから第2のレベルへの遷移時点を、前記各基礎信号の前記次の基礎信号の第2のレベルから第1のレベルへの遷移時点以前に変化させてパルス信号を生成する遷移時点可変部300と、を備える信号生成装置。

(もっと読む)

フィルタ回路および半導体装置

【課題】 フィルタの周波数特性の校正を簡易に精度よく実施する。

【解決手段】 フィルタ回路は、ローパスフィルタと、ローパスフィルタの周波数特性を校正する校正回路とを備えて構成される。校正回路は、負帰還回路と、制御回路とを備えて構成される。負帰還回路は、フィルタ回路の校正モード時に、ローパスフィルタに負帰還を与えてループ回路を形成するとともにループ回路の利得を1より大きくすることによりループ回路を発振させる。制御回路は、フィルタ回路の校正モード時に、ループ回路の発振周波数が所定範囲内に収まるようにローパスフィルタの周波数特性を制御する。

(もっと読む)

フィルタ回路

【課題】本発明は、ゼロIF方式と低IF方式を共用するフィルタ回路において、回路構成を簡素化することによりチップ面積が消費電力を低減する。

【解決手段】受信信号から分離されたI成分(Iin,Iinx)及びQ成分(Qin,Qinx)に対して、それぞれ設けられたゼロIF方式の第1及び第2の実フィルタ(7,8)と、該ゼロIF方式から低IF方式への切替信号を受けたとき該第1及び第2の実フィルタ(7,8)間を相互素子(R21a〜R64b)で接続して複素フィルタにするスイッチ部(SW)とを備える。

(もっと読む)

1 - 20 / 40

[ Back to top ]