Fターム[5J098AC20]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変要素 (423) | スイッチ (137) | 電子的スイッチ (97)

Fターム[5J098AC20]に分類される特許

1 - 20 / 97

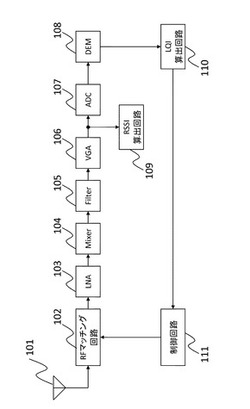

無線通信装置、マッチング制御回路、マッチング制御方法

【課題】RSSI(受信信号強度)を用いたパワーマッチングではノイズが反映されておらず最適な受信感度を実現することができなかった。

【解決手段】本発明の無線通信装置は、アンテナで受信した受信信号に対してインピーダンスマッチングを行うマッチング手段と、前記インピーダンスマッチングが行われた受信信号のノイズが反映された品質指標を算出する品質指標算出手段と、前記ノイズが反映された品質指標に基づいて前記マッチング手段が行うインピーダンスマッチングのマッチング定数を制御する制御手段と、を具備する。当該構成によれば、ノイズを考慮した上でのマッチング制御を行うことができるため、受信感度の最良化を図ることができる。

(もっと読む)

バンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路

【課題】センター周波数を実質的に変化させずに帯域幅を可変することが可能なバンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路を提供すること

【解決手段】本発明にかかる集積回路106は、楕円関数型のバンドパスフィルタ回路100及び制御部105を備える。バンドパスフィルタ回路100は、センター周波数f1を設定する第1LCフィルタ回路部101及び第4LCフィルタ回路部104、共振周波数f2、f3をそれぞれ設定する第2LCフィルタ回路部102、第3LCフィルタ回路部103を備える。前記制御部105は、第2LCフィルタ回路部102が設定するインダクタンス値L2、容量値C2及び第3LCフィルタ回路部103が設定するインダクタンス値L3、容量値C3を可変させて、共振周波数f2及びf3を、互いに増減が逆になるように変化させる。

(もっと読む)

半導体集積回路、受信モジュール及び受信装置、並びに半導体集積回路の調整方法

【課題】CR積で変化する回路ブロック(例えば、IFローパスフィルタ)の特性を調整する工程を製品検査から削減できる、半導体集積回路、受信モジュール及び受信装置、並びに半導体集積回路の調整方法の提供。

【解決手段】可変抵抗33と、スイッチトキャパシタ32と、可変抵抗33とスイッチトキャパシタ32とのCR積の偏差を検出するRCキャリブレーション回路22と、可変抵抗33及びスイッチトキャパシタ32と同一チップに設けられた可変抵抗33と同じ構成の可変抵抗を持つIFローパスフィルタ18とを備える、半導体集積回路。

(もっと読む)

オーディオ機器

【課題】入力端子に接続されたソース機器に合わせて入力インピーダンスやゲインを設定可能なオーディオ機器を提供する。

【解決手段】ホット端子およびコールド端子を有しソース機器が接続される入力端子と、インピーダンス素子と、キャパシタと、テスト信号発生部と、リターン信号解析部と、通常動作時にインピーダンス素子を入力端子に並列に接続し、ソース機器のインピーダンス検出時にコールド端子にテスト信号発生部を接続するとともにホット端子にキャパシタおよびリターン信号解説部を接続する切替スイッチとを備え、ソース機器のインピーダンス検出時に、テスト信号発生部はテスト信号を発生し、リターン信号解析部はホット端子に戻ってきたテスト信号であるリターン信号に基づいてソース機器のインピーダンスを検出する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

可変容量回路

【課題】キャパシタが破壊されずAC信号が歪まないようにした可変容量回路を提供する。

【解決手段】可変容量回路は,基準電位を中心とする交流信号が印加される所定ノードと,所定ノードに接続される第1のキャパシタと,第1のキャパシタと基準電位との間に接続された第2のキャパシタと,第2のキャパシタと第1のキャパシタとの間の第1のノードと基準電位との間に設けられた第3のキャパシタ及び容量制御用のトランジスタと,第3のキャパシタとトランジスタとの間の第2のノードに第1のバイアス電圧を印加するバイアス回路とを有する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の遮断周波数精度を悪化させること無く、回路規模を低減することができるフィルタ回路を提供する。

【解決手段】駆動電流生成回路303は、容量C1に第1の基準電流を一定期間充電することにより生成される充電電圧を用いて、容量C1と第1の基準電流の比に比例した第1の駆動電流を生成する。OTA301は、正入力端子と負入力端子間の電位差に応じて、第1の駆動電流から、容量C1と第1の基準電流の比に逆比例した第2の駆動電流を生成して電圧に変換し、この電圧に応じて第2の基準電流を分配する。OTA301は、第2の基準電流を分配した電流と同量の電流を折り返して供給するカレントミラー回路を有し、正入力端子と負入力端子間の電位差に応じた電流をカレントミラー回路により折り返して負荷容量302に供給する。

(もっと読む)

インピーダンス整合回路、インピーダンス整合方法及び双方向伝送回路

【課題】オープンドレイン出力バッファ間で双方向の伝送を行う際のインピーダンスを整合させて、誤動作することなく高速通信すること。

【解決手段】インピーダンス整合回路は、第1の端子にオープンドレイン出力バッファ、第2の端子に双方向伝送線路が接続され、オープンドレイン出力バッファからの第1の出力信号及び双方向伝送線路からの第2の出力信号を検出する検出回路と、第1の出力信号の電圧の変化が第1の方向であると検出された場合、当該第1の出力信号に負荷抵抗を接続して双方向伝送線路へ出力し、第1の出力信号の電圧の変化が第1の方向とは逆の第2の方向であると検出された場合、当該第1の出力信号にダンピング抵抗を接続して双方向伝送線路へ出力し、第2の出力信号の電圧の変化が検出された場合、当該第2の出力信号に負荷抵抗及びダンピング抵抗のいずれも接続せずにオープンドレイン出力バッファへ出力する抵抗接続回路とを有する。

(もっと読む)

可変減衰器

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

フィルタ装置および通過帯域特性調整方法

【課題】従来よりも少ない回路規模で、半導体で構成される受動素子により形成される通過帯域特性の調整機能を実現できるフィルタ装置および通過帯域特性調整方法を得ること。

【解決手段】通信装置の受信系で用いられるフィルタ装置8であって、半導体で構成される受動素子の組み合わせにより、入力される受信信号に対し通過帯域の制限を行うフィルタ回路4と、毎回の受信動作開始時に、当該受信系において前記フィルタ回路の後段に設けられている信号強度検出回路が検出した信号強度を利用して、前記フィルタ回路の周波数通過特性を、前記入力される受信信号を最大に出力できるように調整する制御回路9とを備えた。

(もっと読む)

積分回路および電圧検出装置

【課題】カットオフ周波数が入力抵抗と帰還コンデンサとで規定される目標とする積分特性を確保しつつ、積分信号の振動を防止する。

【解決手段】非反転入力端子がグランド電位Vgに規定された演算増幅器34aと、演算増幅器34aの反転入力端子に接続された入力抵抗34bと、演算増幅器34aの反転入力端子に一端が接続されると共に演算増幅器34aの出力端子に他端が接続された帰還コンデンサ34cと、演算増幅器34aの反転入力端子に一端が接続されると共に演算増幅器34aの出力端子に他端が接続され、かつ接続点Bが交流的にグランド電位Vgに短絡可能に構成された帰還抵抗34d,34eとを備え、接続点Bとグランド電位Vgとの間に接続されて、接続点Bのグランド電位Vgへの交流的な短絡をオン・オフさせる短絡用スイッチ34gを備えている。

(もっと読む)

カットオフ周波数自動調整回路及び携帯情報端末

【課題】フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能にする。

【解決手段】電圧電流変換回路(30)、充電回路(50)、放電回路(40)、複数の静電容量を有するデジタル容量(70)、上記デジタル容量に入力される電圧と基準電圧との対比を行う比較器(80)及び上記デジタル容量を制御する容量制御回路(600)を含んでカットオフ周波数自動調整回路(412)を構成する。上記リセット信号が所定の論理レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間を計測し、その計測結果と、上記デジタル容量の目標値と、上記デジタル容量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理を、所定の条件下で繰り返すことによって上記デジタル容量を制御する。上記目標値は、調整範囲内の任意の設定値とすることができる。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

スイッチトキャパシタフィルタ及びスイッチトキャパシタフィルタの制御方法

【課題】簡易な構成により雑音を低減することができるスイッチトキャパシタフィルタ及びその制御方法を提供すること。

【解決手段】本発明では、演算増幅器AMPの反転入力は積分キャパシタC0の一端と、出力は積分キャパシタC0他端と接続される。スイッチトキャパシタは第1〜3の順に接続状態が移行する。第1の接続状態では、第1の端子は入力信号と、第2の端子は固定電圧と接続される。第2の接続状態では、第1の端子は固定電圧と、第2の端子は演算増幅器AMPの反転入力と接続される。第3の接続状態では、第1の端子は演算増幅器AMPの出力と、第2の端子は演算増幅器AMPの反転入力と接続される。第2及び第3の接続状態のスイッチトキャパシタが各1個以上存在する場合の第2の接続状態のスイッチトキャパシタの個数は常に同じであり、第3の接続状態のスイッチトキャパシタの個数も常に同じである。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

信号生成装置

【課題】位相に不連続を生じさせずに信号を生成する。

【解決手段】処理部6は、一の通過帯域の周波数の第1信号S1を第1DDS32で生成し、フィルタ35を介して出力信号Soとして出力させている状態において、出力信号Soの周波数を一の通過帯域に隣接する他の通過帯域(フィルタ36の通過帯域)の他の周波数に変更する際に、第1切替部34に対する切替制御を実行して第2DDS33をフィルタ36に接続すると共に、周波数設定制御を実行することによって各DDS32,33から出力される各信号S1,S2の周波数を一の通過帯域と他の通過帯域との重複する帯域の共通周波数に設定し、次いで、第2DDS33に対する位相設定制御を実行して第2信号S2の位相をフィルタ35から出力されている第1信号S1の位相に一致させた後に、第2切替部39に対する切替制御を実行して、出力信号Soを第1信号S1から第2信号S2に切り替える 。

(もっと読む)

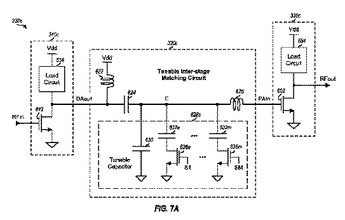

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】受信系チャンネル選択フィルタの高次フィルタおよび送信系ローパスフィルタの低次フィルタの周波数特性の不所望な変動を軽減する。

【解決手段】送受信機能をサポートする半導体集積回路は、所定の次数の受信系チャンネル選択フィルタと小さな次数の送信ローパスフィルタとキャリブレーション回路200を具備する。チャンネル選択フィルタの第1キャリブレーション動作の間に、抵抗スイッチ回路20が使用され電圧・電流変換器30は基準電圧を第1変換電流に変換して、時間積分器40、50は内蔵容量70の時間積分を実行して、電圧比較の結果がラッチ90に格納され、チャンネル選択フィルタの特性が決定される。ローパスフィルタの第2キャリブレーション動作の間に抵抗回路161が使用されて電圧・電流変換器30は基準電圧を第2変換電流に変換して、電圧比較の結果がラッチ90に格納され、ローパスフィルタの特性が決定される。

(もっと読む)

1 - 20 / 97

[ Back to top ]