Fターム[5J098AD21]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 性能向上 (128)

Fターム[5J098AD21]の下位に属するFターム

Fターム[5J098AD21]に分類される特許

1 - 20 / 31

信号等化器

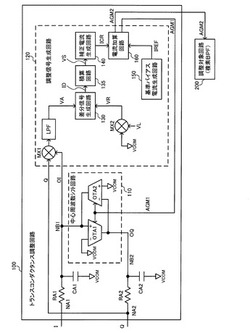

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

磁気アイソレータ

【課題】 一様な外乱磁界の影響を除去しつつ、磁気アイソレータの小型化を図る。

【解決手段】 設置基板1上に設けられた第1の絶縁層2及び第2の絶縁層4と、第1の絶縁層2上に配置された第1の磁気抵抗効果素子3a、第2の磁気抵抗効果素子3b、第3の磁気抵抗効果素子3c及び第4の磁気抵抗効果素子3dと、第2の絶縁層2上に配置され、各磁気抵抗効果素子に対向して設けられた信号入力導体5aと、信号入力折返し導体5bとを信号入力接続線5cを介してミアンダライン状に接続されるよう構成された信号入力線5とを備え、信号入力線5に信号電流が通電されることにより第1の磁気抵抗効果素子3a及び第2の磁気抵抗効果素子3bに印加される磁界の方向と、第3の磁気抵抗効果素子3c及び第4の磁気抵抗効果素子3dに印加される磁界の方向とが、互いに逆方向となるように信号入力線5が構成されたことを特徴とする。

(もっと読む)

可変抵抗制御回路及び可変抵抗器

【課題】抵抗を広い範囲で変化させることができる可変抵抗制御回路及び可変抵抗器を提供すること

【解決手段】本発明にかかる可変抵抗制御回路は、電源10と、電源10よりも低い電位を有する電源11との間に設けられ、電源10と接続される抵抗21と、電源10と、電源11との間に設けられ、前記抵抗21と直列に接続されるMOSトランジスタ31と、電源10と、電源11との間に設けられ、前記MOSトランジスタ31と直列に接続されるMOSトランジスタ32と、抵抗21とMOSトランジスタ31との節点における電圧と、制御電圧とに基づいて、MOSトランジスタ32にゲート電圧を出力するオペアンプ41とを備え、オペアンプ41は、ゲート電圧に基づいて抵抗値が制御される外部の可変抵抗に対してゲート電圧を出力するものである。

(もっと読む)

抵抗値補正回路

【課題】外付けの基準抵抗と半導体集積回路に形成した抵抗の遅延量を比較して、半導体集積回路に形成した抵抗の抵抗値を補正する抵抗値補正回路を提供する。

【解決手段】半導体集積回路に形成した抵抗29と半導体集積回路の外部に設けられた基準抵抗33に予め設定された周期のクロック信号を入力し、抵抗29から出力された第1の信号A1と基準抵抗33から出力された第2の信号A2との遅延差を検出する遅延判定回路3と、直列接続される複数のフリップフロップにより構成されるフリップフロップ部に、遅延判定回路3で遅延差を計測開始と同時にクロック信号を入力し、フリップフロップごとに順次クロック信号を遅延させ、フリップフロップごとに遅延信号を出力し、遅延差が発生している期間に出力された遅延信号を選択して出力するばらつき検出回路と、を備える抵抗値補正回路1である。

(もっと読む)

増幅回路、ジャイレータ回路、信号を増幅するためのフィルタ・デバイス及び方法

【課題】周波数に依存しない伝達特性が改善された増幅器、及びジャイレータ回路の提供。

【解決手段】位相シフタ部2に接続されたトランスコンダクタ・デバイス1を備えた増幅回路A1。位相シフタ部2は、位相シフトが調整可能で、入力信号の周波数に少なくとも部分的に依存するインピーダンスを有している。使用時に、調整可能な位相シフトは、トランスコンダクタ・デバイス1の位相シフトと実質的に反対の値となる様に調整され、実施形態として、位相シフタ部2は、キャパシタ・デバイスCと可調抵抗デバイスRとを含み、可調抵抗デバイスRは、抵抗値制御信号を受信する入力接点Rin、キャパシタ・デバイスに接続された第1の出力接点Rout1、及びトランスコンダクタ・デバイスに接続された第2の出力接点Rout2を有する増幅デバイスRを含み、増幅回路A1は更に、抵抗値制御信号を増幅デバイスの入力接点に供給する制御デバイスを備えている。

(もっと読む)

アクティブフィルタの設計

【課題】LCフィルタをシミュレートすることで低素子感度フィルタの実現を可能にするアクティブ低域フィルタ回路を提供する。

【解決手段】信号入力端子から直列に複数個の抵抗Rを接続し、信号入力端子側からの各抵抗の接続点に順次演算増幅器A1、・・・・An−1の非反転入力端、出力端、反転入力端の順に接続し、各演算増幅器の非反転入力端と接地間に従来のLCフィルタの設計法を用いて求めた値のコンデンサC1、・・・・Cn、および演算増幅器の非反転入力端間にC1,3、・・・・Cn−1,nを接続し、前記の直列に接続された複数個の抵抗Rの最終端から出力信号を取り出す。

(もっと読む)

フィルタ

【課題】タップ係数として任意の値を設定することができるフィルタを得ることを目的とする。

【解決手段】キャパシタ11,31により充電された電荷とキャパシタ13,33により充電された電荷の総和を出力端子Pに出力し、キャパシタ12,32により充電された電荷とキャパシタ14,34により充電された電荷の総和を出力端子Nに出力する。これにより、キャパシタ11〜14,31〜34の容量値Cpp,Cpn,Cnp,Cnnを適宜変更することで、タップ係数として任意の値を設定することができる。

(もっと読む)

映像信号多重伝送装置および映像信号多重伝送装置を用いた撮像装置。

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの伝送路を時分割により、双方向にデジタル化した映像信号を送受する多重伝送装置において、送信側と受信側とにそれぞれ複数の増幅器を有し、受信側に波形等化器を有し、伝送路が長い場合は、送信側では抵抗で帰還回路を構成した電流帰還演算増幅器で高増幅度とし、受信側では、負入力の接地抵抗と、基本波周波数インピーダンスが負入力抵抗の約半分で3次高調波周波数インピーダンスが負入力抵抗の約3倍のフェライトビーズを電流帰還演算増幅器の出力と負入力間に設けた電流帰還演算増幅器とで基本波周波数以下の低周波数成分を減衰させ、3次高調波成分を増強する。伝送路が短い場合は、送信側も受信側も抵抗で帰還回路を構成した電流帰還演算増幅器で0dB(特性整合損失を除けば+6dB)の増幅度とする。

(もっと読む)

フィルタ回路

【課題】 可変する回路定数を減らし、かつ、回路定数の可変範囲を同じにしても、Qの変動が大きくならないようにする。

【解決手段】 VCVS型の2次HPF20B、30Bを縦続接続し、HPF20Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが大から小へ変化する抵抗R22と、HPF30Bの内、抵抗値を大から小へ可変したときカットオフ周波数が低から高へ変化し、Qが小から大へ変化する抵抗R32を互いに連動して抵抗値が可変するようにする。可変抵抗R22とR32を連動して可変したとき、各HPF20B、30BのQが相補的に変動するようにしたので、Qの変動を小さく抑えることができる。各HPF20B、30Bはカットオフ周波数の可変範囲、Qに対する設計自由度が高く、R22とR32の可変範囲を同じにしながらQがほぼ一定にすることができる。

(もっと読む)

半導体集積回路

【課題】複数のノイズパルスが連続して印加される場合においてもノイズを除去する能力を高めたノイズ除去回路を含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、入力信号を遅延する直列接続された複数の遅延回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理積を求めることによってセット信号を生成する第1の論理回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理和を求めることによってリセット信号を生成する第2の論理回路と、第1の論理回路によって生成されるセット信号によってセットされ、第2の論理回路によって生成されるリセット信号によってリセットされることにより、正論理の入力信号からパルス状のノイズが除去された出力信号を生成するRSラッチ回路とを具備する。

(もっと読む)

遅延回路

【課題】映像信号処理回路に用いられる遅延回路の回路規模の抑制化を適切に実現する。

【解決手段】スイッチドキャパシタ技術に基づくサンプルホールド回路として構成される遅延回路において、メモリ単位111の個数を省略した場合に、第2のキャパシタC5と、オン時に第2のキャパシタC5に入力信号INの電圧値を保持させる第3のスイッチング素子T1と、差動増幅器150の非反転入力端子に接続される信号ラインL10と接続されオン時に第2のキャパシタC5に保持された入力信号INの電圧値を出力する第4のスイッチング素子T2と、を備え、シフトレジスタ120の最終段のフリップフロップFF5よりトリガービットTXがシフト出力されてから、シフトレジスタ120の初段のフリップフロップFF1よりトリガービットTXがシフト出力されるまでの間、第3及び第4のスイッチング素子T1、T2をクロック信号CLKと同周期でオンオフさせて信号ラインL10にスイッチングノイズを重畳させる。

(もっと読む)

広帯域分配器

【課題】出力端子に高電圧が入力された場合でもその影響をより少なくするとともに、広帯域なアイソレーション特性を持つ広帯域分配器を提供する。

【解決手段】入力端子1に一端が接続された第1の容量5と、前記第1の容量の他端にゲート端子が接続された第1のFET6と、前記第1のFETのドレイン端子と第1の容量の一端の間に接続された第1のフィードバック回路4と、第1のFETのソース端子6Sとグランド間に接続された第1のソース回路7と、第1のFETのドレイン端子と第1の出力端子2間に接続された第2の容量8とからなる第1の増幅器と、前記入力端子と第2の出力端子3間に接続され、第3の容量10、第2のFET11、第2のフィードバック回路9、第2のソース回路12及び第4の容量13からなる第2の増幅器と、第1のFETのソース6Sと第2のFETのソース11S間に接続されたアイソレーション回路14により構成される。

(もっと読む)

浮動アクティブインダクタ

【課題】回路構成を複雑にすることなしに、そのインダクタンス値及びその内部抵抗値を個別に設定することが可能な浮動アクティブインダクタを提供する。

【解決手段】第1及び第2入力端子1、2間に直列接続された浮動インダクタ回路A及び浮動負性抵抗回路Bと、それらの回路A、Bの直列接続点3を備え、第1及び第2入力端子1、2間に浮動アクティブインダクタが形成されるもので、浮動インダクタ回路Aは、第1入力端子1と直列接続点3間に直列接続された第1キャパシタ4、第1抵抗5、第2キャパシタ6と、第1キャパシタ4の両端に第1低抵抗8を介して接続された第1電圧フォロワ8と、第2キャパシタ6の両端に第2低抵抗を介して接続された第2電圧フォロワ8からなり、浮動負性抵抗回路Bは、直列接続点3と第2入力端子2間に直列接続された第2乃至第6抵抗11〜15と、第2及び第3抵抗11、12に接続された第1オペアンプ16と、第5及び第6抵抗14、15に接続された第2オペアンプ17からなる。

(もっと読む)

遅延回路

【課題】電荷蓄積用キャパシタに蓄積された情報を破壊することなく読み出すことのできるスイッチト・キャパシタ型の遅延回路を提供する。

【解決手段】遅延セル11〜13は、書き込み信号Wが入力されたときに入力端子INへ入力される電流を取り込み、その取り込んだ電流の大きさに応じた電荷をキャパシタC1に蓄積し、そのキャパシタC1の出力電圧で電流源のNMOSトランジスタM1の出力電流の大きさを制御し、読み出し信号Rが入力されたときにその出力電流を出力する。書き込み制御用のシフトレジスタ2は、遅延セル11〜13へ入力する書き込み信号W1〜W3を制御し、遅延セル11〜13への電流の取り込みタイミングを1個ずつ遅延させる。読み出し制御用のシフトレジスタ3は、遅延セル11〜13へ入力する読み出し信号R1〜R3を制御し、電流の取り込み終了後の遅延セル11〜13からの電流の出力タイミングを制御する。

(もっと読む)

差動単相変換回路

【課題】チップ面積を縮小させ、電力効率を向上させた差動単相変換回路を提供すること。

【解決手段】差動単相変換回路1は、ソースフォロア増幅器10とソース接地増幅器20から構成される。ソースフォロア増幅器10は、差動信号の非反転信号INを同相のまま出力する。ソース接地増幅器20は、差動信号の反転信号INXを反転させて、非反転信号INと同位相にする。点Aにおいて、共に同相の2つの差動信号IN、INXが加算されて単相信号OUTとして出力される。

(もっと読む)

減衰回路とスイッチ回路の回路トポロジー

【課題】ダイナミックレンジを制限する寄生キャパシタンスを持ち込まず、挿入損失の低い無線周波数信号の減衰回路を提供する。

【解決手段】無線周波数のためのスイッチ(600)は、可変分路要素と直列伝達要素とを含む。可変分路要素及び直列伝送要素のインピーダンスは、入力端子(IN)における減衰回路のインピーダンスがすべての減衰レベルについて公称値となるように選定されており、これにより、高周波数における低損失が実現される。

(もっと読む)

ラジオ受信機

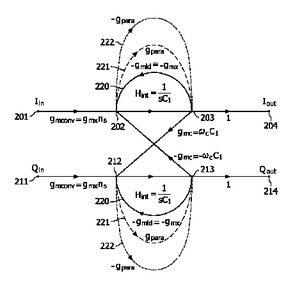

信号有向グラフを用いてフィルタ内の寄生信号伝達を識別するステップと、補償経路をフィルタに追加して寄生信号伝達の影響を低減または解消するステップとを具えた方法を提供する。これに対応するフィルタを提供し、このフィルタは、1つ以上のフィルタ極を生成する複数の増幅段と、これらの増幅段の少なくとも1つに結合された少なくとも1つの構成部品であって、フィルタ内に寄生効果を生じさせる構成部品と、上記少なくとも1つの増幅段に補償電流を加えて、この寄生効果を低減または解消する手段とを具えている。さらにラジオ受信機を提供し、このラジオ受信機は、同相及び直交信号を受信してフィルタ処理するフィルタと、フィルタ処理した同相及び直交信号の一方を受信して増幅する増幅器と、フィルタ処理して増幅した同相または直交信号をこの増幅器から受信し、上記同相または直交信号の他方を、上記フィルタ処理して増幅した信号から再生する手段とを具えている。  (もっと読む)

(もっと読む)

1 - 20 / 31

[ Back to top ]