Fターム[5J098EA08]の内容

能動素子を用いた回路網 (5,588) | 減衰回路網の機能と構成 (73) | 1端子対回路 (30)

Fターム[5J098EA08]に分類される特許

1 - 20 / 30

ポジショナ

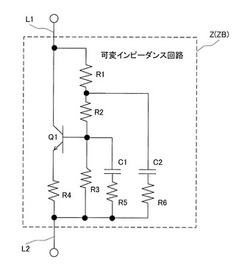

【課題】低周波のノイズの影響に強いポジショナを提供する。

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

可変減衰器

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

減衰器

【課題】減衰量の周波数依存性を改善することができる減衰器を提供すること。

【解決手段】減衰器10は、FET11〜13、インダクタ14及び15、抵抗16、入力端子17、出力端子18を備え、入力端子17には、FET11のドレイン電極と、FET12のドレイン電極と、インダクタ14の一方端とが接続され、出力端子18には、FET11のソース電極と、FET13のドレイン電極と、インダクタ15の一方端とが接続され、FET11のドレイン電極とソース電極との間にインダクタ14と、抵抗16と、インダクタ15とが直列に接続された構成を有する。

(もっと読む)

高インピーダンス回路、フィルタ回路及び増幅回路

【課題】従来技術の高インピーダンス回路は、温度変化等の影響を受けて、高いインピーダンスを維持することができないという問題があった。

【解決手段】本発明にかかる高インピーダンス回路は、ダイオード接続されたトランジスタ21,22を備え、トランジスタ21のバックゲートとトランジスタ22のソースとが接続され、トランジスタ22のバックゲートとトランジスタ21のソースとが接続される。このような回路構成により、温度変化等の影響を抑え、高いインピーダンスを維持することができる。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

可変抵抗制御回路及び可変抵抗器

【課題】抵抗を広い範囲で変化させることができる可変抵抗制御回路及び可変抵抗器を提供すること

【解決手段】本発明にかかる可変抵抗制御回路は、電源10と、電源10よりも低い電位を有する電源11との間に設けられ、電源10と接続される抵抗21と、電源10と、電源11との間に設けられ、前記抵抗21と直列に接続されるMOSトランジスタ31と、電源10と、電源11との間に設けられ、前記MOSトランジスタ31と直列に接続されるMOSトランジスタ32と、抵抗21とMOSトランジスタ31との節点における電圧と、制御電圧とに基づいて、MOSトランジスタ32にゲート電圧を出力するオペアンプ41とを備え、オペアンプ41は、ゲート電圧に基づいて抵抗値が制御される外部の可変抵抗に対してゲート電圧を出力するものである。

(もっと読む)

フィルタ回路およびバイアス回路

【課題】回路面積の縮小を図りつつ、出力信号に含まれるオフセットを減少させることが可能なフィルタ回路を提供する。

【解決手段】フィルタ回路は、入力端子と出力端子との間に接続された第1のキャパシタと、前記出力端子と設定電位との間に接続されたバイアス回路と、を備え、前記バイアス回路は、前記出力端子と設定電位との間に接続された第1のMOSトランジスタと、前記第1のMOSトランジスタのゲートと前記出力端子との間に接続された第2のキャパシタと、前記第1のMOSトランジスタのゲートに一端が接続され、第1のバイアス電位が他端に印加された抵抗素子と、を有する。

(もっと読む)

抵抗増倍回路

【課題】チップ面積の増大を招くことなく、半導体材料に起因するhfeのばらつきなどに影響されることのない安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に抵抗器3の一端が接続され、抵抗器3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、抵抗器3の他端に接続されて、信号入力端子8から見た抵抗器3の見かけ上の抵抗値が1/(1+N)倍に見えるものとなっている。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

半導体集積回路および装置

【課題】外部抵抗を備える半導体集積回路において、外部抵抗の抵抗値を容易に変更可能にする技術を提供する。

【解決手段】外部抵抗を備える半導体集積回路であって、半導体集積回路の入出力インピーダンスは、外部抵抗の抵抗値に基づいて調整され、外部抵抗は、その抵抗値として、複数の抵抗値の中から所望の抵抗値を選択できるように形成されていることを特徴とする半導体集積回路。

(もっと読む)

可変減衰器及び無線通信装置

【課題】高周波で使用する1段当たりの可変減衰量が大きい可変減衰器を提供する。

【解決手段】可変減衰器は、ゲート、ドレイン、ソース、ボディを有するMOSFET12と、減衰量制御回路14と、温度補償回路21とを備える。減衰量制御回路14は、ゲート、及びドレイン、ソースに制御電圧を与える。温度補償回路21は、ボディに温度補償電圧を与える。入力端子、出力端子は、それぞれMOSFET12のドレイン、ソースに接続する構成をとる。温度補償回路21は、MOSFET12の動作温度に応じて、ボディに供給する電圧を制御して、ホディ電圧とゲート電圧との関係で入力端子及び出力端子間に流れる電流の抵抗値を調整する。

(もっと読む)

温度補償バイアス回路、高周波増幅器及び高周波減衰器

【課題】負電圧で動作可能であり、かつ出力電圧の温度変化が大きな特性が得られる温度補償バイアス回路を提供する。

【解決手段】プラス側電圧印加端子3にドレイン端子が接続し、温度が高くなるにつれてドレイン電流が増加する傾向を示す閾値電圧Vth付近の電圧範囲のゲート−ソース間電圧Vgsが印加されるトランジスタ4と、一端がトランジスタ4のソース端子に接続し、他端が抵抗6の一端に接続するダイオード5と、一端が抵抗6の他端に接続すると共に、他端がマイナス側電圧印加端子1に接続し、トランジスタ4のゲート端子が抵抗6との接続部に接続する抵抗7と、ダイオード5と抵抗6との接続部に接続して出力電圧が取り出される出力電圧端子2とを備えた。

(もっと読む)

MOS抵抗制御装置、MOS減衰器、無線送信機

【課題】MOS減衰器としての可変特性を所望に合わせ込んでそのばらつきを吸収することが可能なMOS抵抗制御装置、これを用いる無線送信機を提供すること。

【解決手段】ソースが第1の基準電位に接続されたMOSトランジスタと、該MOSトランジスタのドレインと第2の基準電位との間に挿入・接続された第1の制御電流源と、第1、第2の入力端、および出力端を有し、該第1の入力端がMOSトランジスタのドレインと第1の制御電流源との接続ノードに接続され、該出力端がMOSトランジスタのゲートに接続されたオペアンプと、該オペアンプの第2の入力端に一端が接続されたインピーダンス素子と、該インピーダンス素子に一端の側から電流を入力する基準電流源と、インピーダンス素子に一端の側からさらに電流を入力する第2の制御電流源と、MOSトランジスタのドレインに電流を入力する第3の制御電流源とを具備する。

(もっと読む)

交流直流電圧分離回路

【課題】トランジスタTrのエミッタ電圧帰還効果により、交流電圧ACに対して直流負荷Zdcを見かけ上で高インピーダンスとして、交流電圧ACが直流負荷Zdc側に印加されない交流直流電圧分離回路を提供する。

【解決手段】交流電圧ACと直流電圧DCが重畳された入力電圧が印加される回線10に接続したコンデンサC1で取り出した交流電圧ACを交流負荷Zacに印加する。回線10にトランジスタTrのコレクタを接続してそのエミッタを直流負荷Zdcに接続し、コレクタとベース間に抵抗R1を介装し、ベースを第2のコンデンサC2を介して接地し、エミッタに取り出された直流電圧DCを直流負荷Zdcに印加する。エミッタ電圧帰還効果により、コレクタ側から見た直流負荷Zdcが数10kΩ以上の値となり、交流電圧ACが直流負荷Zdcにより減衰されずに、また直流負荷Zdcに交流電圧ACが印加するようなことがない。

(もっと読む)

インダクタンス可変型共振回路及びそれを用いた放送用受信機。

【課題】 インダクタンス可変型共振回路を実現する手段を提供し、主に車載用放送受信機の感度の向上及び妨害波除去能力の向上を解決する為の手段を提供する。

【解決手段】 増幅器と誘導性素子を組み合わせ、増幅器の利得を+1未満の範囲で電子的に可変することによって、誘導性素子のインダクタンスを可変するLC共振回路を提供し、そのLC共振回路を、アンテナ容量が存在しても所望の周波数帯域を可変することが可能な同調回路及び局部信号発生器の発振器として利用することによって解決する。

(もっと読む)

MOS抵抗制御装置、MOS減衰器

【課題】MOS抵抗の制御精度を向上することができるMOS抵抗制御装置およびこれを利用したMOS減衰器を提供すること。

【解決手段】ソースドレインが直列に接続され、該直列に接続されたソースドレインのうち最も外側のソースが第1の基準電位に接続された2以上のMOSトランジスタと、この2以上のMOSトランジスタの直列に接続されたソースドレインのうち最も外側のドレインと第2の基準電位との間に挿入・接続された電流源と、第1、第2の入力端、および出力端を有し、該第1の入力端に第3の基準電位が供給され、該第2の入力端が最も外側のドレインと第2の基準電位との接続ノードに接続され、該出力端が2以上のMOSトランジスタのゲートそれぞれに接続されたオペアンプとを具備する。

(もっと読む)

アッテネータ

【課題】通過状態及び減衰状態において同程度の歪み特性を同程度の送信電力まで許容することができ、かつ通過状態において電力増幅器の利得圧縮特性を補償することができるアッテネータを得る。

【解決手段】リニアライザは、第5ダイオードD51〜D5nと、第3抵抗RLT1と、第6ダイオードD61〜D6nと、第1のnチャネルMOSトランジスタTr1とを有する。そして、第1,第4制御電圧端子Vc1,Vc4にロウレベルの電圧が印加され、かつ第2,第3制御電圧端子Vc2,Vc3にハイレベルの電圧が印加される場合に、第5制御電圧端子Vc5にロウレベルの電圧が印加され、第1,第4制御電圧端子Vc1,Vc4にハイレベルの電圧が印加され、かつ第2,第3制御電圧端子Vc2,Vc3にロウレベルの電圧が印加される場合に、第5制御電圧端子Vc5にハイレベルの電圧が印加される。

(もっと読む)

スイッチ回路

【課題】減衰器、移相器の動作制御に用いられ、減衰量および移相量を切替えるのに制御電圧が1つで済むことより、ICの小型化、低コスト化が可能なスイッチ回路を提供する。

【解決手段】スイッチ回路は、回路部1、2と、抵抗R11〜R14、RT0と、キャパシタC1、C2と、NMOSトランジスタT0とから構成されている。また、RF入出力端子Vio1、Vio2から信号の入出力が行われる。Vrefは基準となる電位であり、定電位に保持されている。また、不図示の制御手段により制御電圧Vcを変える事によりNMOSトランジスタT0のドレインーソース間抵抗が制御される。

(もっと読む)

1 - 20 / 30

[ Back to top ]