Fターム[5J104AA20]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 目的、効果 (22,786) | 演算方法の改善(高速化・効率化・簡素化) (933) | 並列化・パイプライン化 (73)

Fターム[5J104AA20]に分類される特許

1 - 20 / 73

新暗号規格(AES)向けの柔軟なアーキテクチャおよび命令

【課題】汎用プロセッサ用の柔軟なAES命令セットを提供する。

【解決手段】AES命令セットは、AES暗号化または復号化用に「1ラウンド」パスを行う命令を含み、さらに、鍵生成を行う命令を含む。128/192/256ビット鍵用の鍵生成の鍵サイズおよびラウンド数を示すのに直近を利用してよい。柔軟なAES命令セットは、暗黙のレジスタをトラッキングする必要がないので、パイプライン能力の最大限の発揮が可能である。

(もっと読む)

演算装置

【課題】演算装置を小型化する。

【解決手段】演算措置は、データの種類ごとにN個の前記データを連続するアドレスに記憶する記憶装置と接続され、予め定められた暗号方式の演算を実行する。演算装置は、演算部と、アドレス生成部と、制御部とを備える。演算部は、暗号方式で用いられる複数の演算処理を実行する。アドレス生成部は、演算処理で用いられる種類のN個のデータのうち先頭のデータのアドレスの上位ビットと、指定に応じて更新されるカウンタ値に応じた値であって先頭のデータのアドレスを基準とするオフセットと、に基づいて、演算処理で用いられるデータを記憶する記憶装置のアドレスを生成する。制御部は、暗号方式で定められる順序で演算処理を実行するように演算部を制御するとともに、演算処理で用いられるデータの種類を変更するタイミング、および、演算処理で用いられるデータを変更するタイミングでカウンタ値の更新を指定する。

(もっと読む)

情報処理装置、情報処理方法、及びコンピュータプログラム

【課題】乱数生成能力と素数判定能力とを有する情報処理装置において、より効率的に素数を生成する。

【解決手段】入力された数値が素数であるか否かを判定しかつ素数である場合に該数値を出力する複数の判定手段を備える。複数の乱数シードを取得し、1以上の判定手段が所属するそれぞれの判定グループに複数の乱数シードの何れかを対応付ける。乱数シードを用いて生成した乱数を、該乱数シードに対応付けられた判定グループに入力する。ここで、着目乱数シードを用いて、乱数を生成する乱数生成系列を初期化する。乱数生成系列を用いて乱数を生成する。乱数のビット列を所定ビット数のビット列へと分割する。分割によって得られたそれぞれのビット列が示す数値を、着目乱数シードに対応付けられた判定グループを構成する判定手段の何れかへと出力する。

(もっと読む)

情報処理システム、情報処理方法、及びプログラム

【課題】乱数生成能力と素数判定能力とを有する情報処理システムにおいて、並列に行われる素数生成処理を効率化する。

【解決手段】生成ユニットは、乱数を生成し、かつ生成した乱数のビット列の少なくとも一部を、少なくとも1つの判定ユニットに送信する。判定ユニットは、少なくとも1つの生成ユニットから送信されたビット列を組み合わせて所定ビット数の数値を生成し、生成した数値が素数であるか否かを判定し、かつ素数であると判定された数値を出力する。制御手段は、生成ユニットが乱数を生成するのに要する時間と、判定ユニットが数値について素数であるか否かを判定するのに要する時間とが近くなるように、複数の処理ユニットの一部若しくは全部のそれぞれを生成ユニット又は判定ユニットとして動作させる制御を行う。

(もっと読む)

ユーザ認証方法、ユーザ認証装置、およびプログラム

【課題】より効果的な生体認証を実現する。

【解決手段】ユーザの頭部伝達関数を用いて上記ユーザの周りの空間の第1の位置にある音源を仮想的に定位させた音データを上記ユーザに向けて再生すること、上記再生された音データを聴取した上記ユーザが上記音源の位置として推定した、上記ユーザの周りの空間の第2の位置を取得すること、および上記第1の位置と上記第2の位置との符合によって上記ユーザを認証することを含むユーザ認証方法が提供される。

(もっと読む)

情報処理装置、情報処理方法、及びプログラム

【課題】複数の演算ユニットを用いた並列処理において、より高速に素数を求める。

【解決手段】複数の演算ユニットのうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。複数の演算ユニットのそれぞれは、乱数発生処理の実行が指示されると、メモリに格納されているシードを用いて乱数を生成し、メモリに格納されているシードを生成した乱数で更新し、生成した乱数が素数であれば、該生成した乱数を出力する。乱数発生処理の実行を指示した演算ユニットによる更新処理が完了したことを検知すると、演算ユニットとは別の演算ユニット群のうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。

(もっと読む)

暗号処理装置

【課題】データの転送回数を従来より削減し、復号処理と認証処理との並列化処理を高速化した暗号処理装置を提供する。

【解決手段】復号処理を行う復号処理手段107と、認証処理を行う認証処理手段108と、前記復号処理手段および前記認証処理手段への入出力データを処理する入出力データ処理手段106を有し、前記入出力データ処理手段106は、前記入出力データ処理手段106への入力データから、前記認証処理手段108で用いられるパラメータを算出するパラメータ算出手段1062と、前記パラメータ算出手段1062で算出されたパラメータ、あるいは、前記復号処理手段107で処理されたデータから算出されたパラメータと、前記入出力データ処理手段106への入力データから、前記認証処理手段107への入力データを成形する入出力データ成形手段1063を有する。

(もっと読む)

演算処理装置およびその方法、並びに、情報処理装置

【課題】 二つのデータを結合した結合データを構成する各データの独立性を維持して結合データを高速に加算処理する。

【解決手段】 判定部801は、二つのデータを結合した第一の結合データX、および、二つのデータを結合した第二の結合データYを入力する。分割部702は、第一の結合データXを上位ビットデータA641と下位ビットデータA642に分割し、第二の結合データを上位ビットデータB641と下位ビットデータB642に分割する。加算処理部704は、上位ビットデータA641と上位ビットデータB641を加算処理する。加算処理部705は、下位ビットデータA642と下位ビットデータB642を加算処理する。結合部708は、加算処理によって得られる上位ビットデータ641と下位ビットデータ642を結合した第三の結合データM'を出力する。

(もっと読む)

ストリーム暗号の暗号化装置、ストリーム暗号の復号化装置、ストリーム暗号の暗号化方法、ストリーム暗号の復号化方法およびプログラム

【課題】n個のストリーム暗号の暗号化器あるいはストリーム暗号の復号化器の処理を含む、すべての処理を並列して実行する。

【解決手段】並列処理暗号モジュールが、l−nビットの初期値と平文と秘密鍵とを入力し、nビットの初期値を生成し、生成したnビットの初期値と入力したl−nビットの初期値とを結合してlビットの初期値を生成する。また、入力した平文をn個に分割し、生成したnビットの初期値をn個のストリーム暗号の暗号化器に1ビットずつ出力するとともに、秘密鍵および1/nに分割した平文をn個のストリーム暗号の暗号化器に出力する。

(もっと読む)

暗号処理装置、および暗号処理方法、並びにプログラム

【課題】暗号処理構成の小型化を実現する。

【解決手段】データ処理対象となるデータの構成ビットを複数ラインに分割して入力し、各ラインのデータに対してデータ変換処理を繰り返して実行する暗号処理部を有し、暗号処理部は、複数ラインを構成する1ラインのデータを入力して、変換データを生成するF関数実行部と、F関数の出力に対する他ラインのデータとの排他的論理和演算を実行する排他的論理和演算実行部と、F関数実行部における変換データの生成過程の中間データを格納する中間データ格納レジスタと、中間データ格納レジスタの格納データに基づいて、F関数実行部に対する入力データを算出する逆演算実行部を有する。逆演算実行部における逆演算により、F関数実行部に対する入力値を算出可能となり、このデータを保持するレジスタを削減することが可能となる。

(もっと読む)

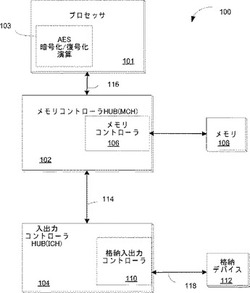

プロセッサ及びプロセッサシステム

【課題】わずかな回路の追加で、安全かつ高速なメモリアクセスを実現するプロセッサを提供する。

【解決手段】命令コードを実行するCPUコアと複数のウェイを有するキャッシュメモリ部とを備えるプロセッサにて、コアに対して入出力されるデータを共通鍵暗号方式で暗号化又は復号する暗号化カウンタデータを複数のウェイの内の1つのウェイに格納し、暗号化カウンタデータと入出力されるデータとをXOR演算するようにして、暗号化又は復号をする度に暗号化カウンタデータを生成する共通鍵暗号処理を行わず、安全性を損なうことなく高速なメモリアクセスを実現できるようにする。

(もっと読む)

情報処理装置、画像形成装置及び情報処理方法

【課題】データの処理順において連続する2つ以上のデータを演算した結果を用いて暗号化を行う場合に、処理の並列性を高めること。

【解決手段】所定の暗号方式によりデータを暗号化する情報処理装置であって、データを所定の暗号化方式により暗号化する複数の暗号器144と、暗号化すべきデータを定められたデータ量ごとに分割された分割データとして暗号器144に振り分けて入力するメモリバッファ制御部142と、暗号器144によって夫々暗号化された分割データを分割される前の順番に従って並べることにより暗号化データを生成し、分割データを夫々暗号化した前記暗号器の数を暗号化データと関連付けて記憶するHDDバッファ制御部145とを含むことを特徴とする。

(もっと読む)

演算装置

【課題】複数のデータに対してハッシュ処理のパイプライン処理が可能なハッシュ値算出装置の提供を目的とする。

【解決手段】ハッシュ値算出装置100は、入力したデータからハッシュ値を算出するまでの処理をp個に分割したそれぞれぞれの処理を順次行う第1処理部から第p処理部を備える。第1処理部はハッシュ値算出のためのデータを入力して処理し、処理した結果を第1処理データとして出力する。第2処理部は第1処理部の出力した、第i処理部は第i−1処理部の出力した第i−1処理データを入力して処理し、第1処理データを入力して処理し、処理した結果を第2処理データとして出力する。順次処理した結果を第i処理データとして出力する。第p処理部は第p−1処理部の出力した第p−1処理データを入力し、入力した第p−1処理データに基づいて、入力したデータに対応するハッシュ値を算出して出力する。

(もっと読む)

情報処理装置

【課題】最小限の回路規模により複数の暗号化処理を並列に行う。

【解決手段】メモリ上のデータを転送する複数の転送手段と、データに処理を施すデータ処理手段と、複数の転送手段から転送要求をアビトレーションするアビトレーション手段と、データ処理手段における処理に関するパラメータを複数の転送手段ごとに保持する手段と、アビトレーションの結果に基づき、パラメータをデータ処理手段に出力する手段と、処理されたデータの出力先を選択する出力先選択手段と、を有し、データ処理手段は、動作状況を示す動作中判別信号をアビトレーション手段に送信し、アビトレーション手段は、転送要求それぞれの優先度が記述されたアビトレーションポリシーを保持しており、当該アビトレーションポリシーと動作中判別信号とに基づき、転送要求をアビトレーションし、出力先選択手段は、アビトレーションの結果と動作中判別信号に基づき、データの出力先を選択する。

(もっと読む)

データ処理装置及びデータ処理プログラム

【課題】メッセージを分割して並列処理するデータ処理装置において、処理分岐条件式を減少し、最終ブロック処理の際のパディングデータ付与に起因するブロック増加数を減少できるデータ処理装置を提供する。

【解決手段】メッセージ分割部102は、最終ブロックのデータが220オクテット以下かを判定する。220オクテット以下と判定した場合は最終ブロックのデータを55オクテット以下の4つのデータに分割し、各データに9オクテットの付加データを付加して64オクテットブロックを生成する。最終ブロックのデータが220オクテットを超えると判定した場合は、最終ブロックに含まれるデータを55オクテットの3つのデータと、残りのデータとの4つのデータに分割し、各55オクテットデータに9オクテットの付加データを付加して3つの64オクテットブロックを生成し、残りのデータに付加データを付加して128オクテット長のデータを生成する。

(もっと読む)

認証装置

【課題】

現代社会において個人情報を含む情報の取り扱いが増え、幅広い分野で個人を同定する個人認証手段が必要不可欠となっている。しかしこのような個人認証技術の利用と共に、機器に対するセキュリティの向上のために、機器への認証動作、再認証動作といった処理時間の増加が問題となっている。

【解決手段】

ユーザ認証処理を生体情報によって認証する入出力装置と、ユーザの生体情報を用いて認証処理を行う認証処理部とを有し、前記入出力装置によるユーザ認証操作の開始時にバックグラウンドで機器へのユーザ所望の処理準備を開始始する事を特徴とする。

(もっと読む)

共用メモリ配線を有する暗号化プロセッサ

【課題】さまざまな秘密鍵および公開鍵の暗号化アルゴリズムを処理するようプログラム可能な暗号化チップを提供する。

【解決手段】暗号化チップは、演算処理装置のパイプラインを含み、該演算処理装置の各々は、秘密鍵アルゴリズム内の1ラウンドを処理することが可能である。データは、該演算処理装置間で、デュアルポートメモリを介して転送される。中央処理装置は、単一サイクルのオペレーションで、グローバルメモリからの非常に幅の広いデータ語を処理することができる。加算器回路は、比較的小さい複数の加算器回路を使用することによって簡素化され、合計およびキャリが複数サイクルでループバックされる。乗算器回路は、非常に幅の広い中央処理乗算器となるよう連結することができるように、より小さい演算処理装置乗算器を適用することによって、複数の演算処理装置と中央処理装置との間で共用することができる。

(もっと読む)

暗号処理装置

【課題】電力解析攻撃に対する耐性を確保しつつ、処理時間を短くできる暗号処理装置を提供する。

【解決手段】暗号処理装置1は、それぞれが暗号処理を実行する第1及び第2のラウンド関数演算回路27a、27bと、第1のラウンド関数演算回路27aと前記第2のラウンド関数演算回路27bを並列に動作させる並列動作モード(PM)と、第1のラウンド関数演算回路27aと第2のラウンド関数演算回路27bを直列に動作させる直列動作モード(SM)とをランダムに切り替えて、第1のラウンド関数演算回路27aと第2のラウンド関数演算回路27bを動作させる制御回路30とを有する。

(もっと読む)

データ送信装置、データ送信方法

【課題】 制御周期に影響を与えることなく大容量のデータ送信を可能にするデータ送信装置、データ送信方法を提供する。

【解決手段】 取得されたデータに対して所定の処理を施して通信データとして送信する処理実行部11,134,144と、送信すべき優先度の高いデータに対する優先度の低いデータについての処理を複数のブロックに分割する分割部134,144と、前記処理実行部による前記優先度が低いデータについての処理中に、前記優先度の高いデータを取得した場合、前記処理実行部により処理が行われているブロック以後に処理されるブロックに先んじて前記優先度の高いデータを処理させる優先制御部133,143とを有する。

(もっと読む)

データ変換装置、およびデータ変換方法、並びにプログラム

【課題】圧縮関数実行部の改善された構成を実現する。

【解決手段】メッセージデータの分割データを並列に入力する複数の処理系列の複数の圧縮関数実行部を適用したデータ変換処理を実行する。複数の圧縮関数実行部の各々は、メッセージデータの分割データを入力してメッセージスケジュール処理を行うメッセージスケジュール部を適用した処理と、このメッセージスケジュール部の出力と前段処理部からの出力である中間値を入力してデータ圧縮により中間値と同一ビット数の出力データを生成する連鎖値処理部を適用した処理を行う。複数の圧縮関数実行部は、メッセージスケジュール部または連鎖値処理部の少なくともいずれかを共有し、単一のメッセージスケジュール部、または単一の連鎖値処理部を利用する。本構成により、ハードウェア構成の小型化、処理ステップの簡略化が実現される。

(もっと読む)

1 - 20 / 73

[ Back to top ]