Fターム[5J104AA23]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 目的、効果 (22,786) | 演算方法の改善(高速化・効率化・簡素化) (933) | 素数生成に関する (18)

Fターム[5J104AA23]に分類される特許

1 - 18 / 18

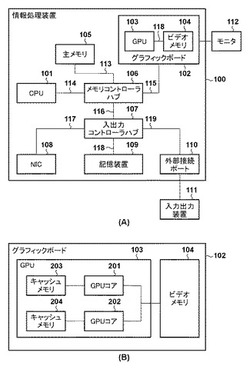

情報処理装置、情報処理方法、及びコンピュータプログラム

【課題】乱数生成能力と素数判定能力とを有する情報処理装置において、より効率的に素数を生成する。

【解決手段】入力された数値が素数であるか否かを判定しかつ素数である場合に該数値を出力する複数の判定手段を備える。複数の乱数シードを取得し、1以上の判定手段が所属するそれぞれの判定グループに複数の乱数シードの何れかを対応付ける。乱数シードを用いて生成した乱数を、該乱数シードに対応付けられた判定グループに入力する。ここで、着目乱数シードを用いて、乱数を生成する乱数生成系列を初期化する。乱数生成系列を用いて乱数を生成する。乱数のビット列を所定ビット数のビット列へと分割する。分割によって得られたそれぞれのビット列が示す数値を、着目乱数シードに対応付けられた判定グループを構成する判定手段の何れかへと出力する。

(もっと読む)

情報処理システム、情報処理方法、及びプログラム

【課題】乱数生成能力と素数判定能力とを有する情報処理システムにおいて、並列に行われる素数生成処理を効率化する。

【解決手段】生成ユニットは、乱数を生成し、かつ生成した乱数のビット列の少なくとも一部を、少なくとも1つの判定ユニットに送信する。判定ユニットは、少なくとも1つの生成ユニットから送信されたビット列を組み合わせて所定ビット数の数値を生成し、生成した数値が素数であるか否かを判定し、かつ素数であると判定された数値を出力する。制御手段は、生成ユニットが乱数を生成するのに要する時間と、判定ユニットが数値について素数であるか否かを判定するのに要する時間とが近くなるように、複数の処理ユニットの一部若しくは全部のそれぞれを生成ユニット又は判定ユニットとして動作させる制御を行う。

(もっと読む)

情報処理装置、情報処理方法、及びプログラム

【課題】複数の演算ユニットを用いた並列処理において、より高速に素数を求める。

【解決手段】複数の演算ユニットのうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。複数の演算ユニットのそれぞれは、乱数発生処理の実行が指示されると、メモリに格納されているシードを用いて乱数を生成し、メモリに格納されているシードを生成した乱数で更新し、生成した乱数が素数であれば、該生成した乱数を出力する。乱数発生処理の実行を指示した演算ユニットによる更新処理が完了したことを検知すると、演算ユニットとは別の演算ユニット群のうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。

(もっと読む)

公開鍵暗号技術におけるドメインパラメータの生成

【課題】暗号プロトコルや公開鍵暗号に係る処理において計算負荷を減少させる。

【解決手段】公開鍵暗号方式において秘密鍵と公開鍵の生成に使用されるpおよびqを生成する方法。p,qは素数であり、pは、素数であるrか、qと同じ若しくはqより大きな素数の合成数であるrを用いて、式p=2qr+1により計算されるセキュアー素数である。公開鍵暗号方式に使用するセキュリティパラメータをk,qのビット長をN,aを0<a<2kである奇数としたとき、qを、式q=22k−aもしくは式q=2N−a、または、式q=22k+aもしくは式q=2N−1+aに基づいて生成する。pの所望のビット長をL,bを0<bである奇数としたとき、qを、式q=22k−aもしくは式q=2N−aにより生成した場合は、rを、式r=2L−2k−1+bもしくは式r=2L−N−1+b、または、式r=2L−2k−bもしくは式r=2L−N−bにより生成する。

(もっと読む)

パラメータ設定装置、離散対数計算装置、事前計算装置、パラメータ設定方法、離散対数計算方法、事前計算方法、プログラム

【課題】離散対数の計算量と素因数分解の計算量の比を大きくする

【解決手段】本発明のパラメータ設定装置は、条件設定部、素数生成部、整数生成部を備える。条件設定部は、整数Nを素因数分解するための計算量が、数体篩法の方が楕円曲線法よりも少なくなるように、整数Nのサイズと素因数の数R(ただし、Rは2以上)を決める。素数生成部は、整数Nのサイズと素因数の数Rから、R個の素数pr(ただし、rは1からRの整数)を生成する。整数生成部は、素数prから整数Nを求める。本発明の離散対数計算装置は、整数N、素数p1,…,pR、要素g、要素yを入力として、y=gxを満たす整数xを求める。本発明の離散対数計算装置は、因子基底計算部と群要素計算部とを備える。

(もっと読む)

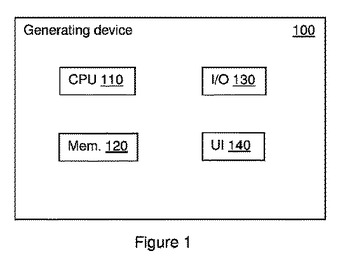

格納されている入力値および格納されているカウント値を利用する暗号化鍵生成

【課題】情報処理システムは、1以上の暗号化鍵を用いて情報を暗号化、復号化するが、これらの鍵が大きな鍵(例えば一対の2048ビットのRSA鍵)の場合、記憶装置に格納することでシステム当たりのコストを上昇させるため、1以上の固有の暗号化鍵を再生成する機能を提供して、コスト低減する。

【解決手段】格納されている入力値および格納されているカウント値を利用して暗号化鍵を生成する方法であって、プロセッサ100は、入力値とカウント値とを格納する不揮発性記憶装置140と、格納されている入力値と格納されている第1のカウント値とに基づいて、暗号化鍵を生成するロジック122とを備え、暗号化鍵を生成する。

(もっと読む)

電子署名検証システム、電子署名装置、検証装置、電子署名検証方法、電子署名方法、検証方法、電子署名プログラム、検証プログラム

【課題】本発明は、電子署名を構成する要素の数を少なくし、電子署名長が短く、情報量及び通信量が少なく、また、検証時の計算量の少ない電子署名検証方法及び装置を提供することを目的とする。

【解決手段】本発明の電子署名検証システムは、登録装置と、電子署名装置と、検証装置からなる。電子署名装置は、乱数x及びyとG1及びG2それぞれの生成元g1及びg2を用いて、X=g2x、Y=g2yを計算し、公開鍵pkを生成する。g1、g2、乱数ri、x、y及び平文miを用いて、電子署名σを生成する。検証装置は、公開鍵pk、電子署名σ及び平文miを用いて、改竄等が行われていないか検証する。

(もっと読む)

電子署名システム、鍵合意システム、電子署名方法および鍵合意方法

【課題】Waters偽造不可署名と同程度の効率を有する強偽造不可署名方式のスタンダードモデルおよび安全性と効率性とを有する三者間SAKAPのスタンダードモデルを提供する。

【解決手段】電子署名方式が、送信者が自分自身のlong-term private keyを知っているという事実を受信者が送信文書から検証することができるという基本的な属性を含む強偽造不可(定理1)であり、かつ、送信者の認証機能付き鍵合意プロトコルSAKAPとして、キー生成、メッセージ生成、ベリフィケーション、キー・アグリーメントの4つのフェーズを有し、そのうち、前3つの各フェーズが、前記電子署名方式により構成され、かつ、如何なる送信者もshort-term secretを漏洩せず(定理2)、かつ、Known Key Security(定理3)、Perfect Forward Secrecy(定理4)、Key Compromise Impersonation Secure(定理5)の属性を満たす仕組みを実現する。

(もっと読む)

記憶位置抽出装置および記憶位置抽出方法

【課題】共通部分抽出に必要となる処理の並列化を可能とし、処理全体の効率化を図って処理時間を高速化することを課題とする。

【解決手段】共通アドレス抽出装置10は、各バイトに対して篩処理一回目のログ加算処理を実施し、一回目のログ加算処理が終了した後の各バイトの値に対して、条件を満足するバイトのアドレスに付属するパリティビットをオンとする。続いて、共通アドレス抽出装置10は、パリティビットの値を保持した状態のまま、各バイトに対して篩処理二回目のログ加算処理を実施する。そして、共通アドレス抽出装置10は、二回目の篩処理が終了した後のバイトが保持する値それぞれに対して、条件を満足しないバイトのアドレスに付属するパリティビットをオフとする。その後、共通アドレス抽出装置10は、対応するパリティビットの値が1であるバイトのアドレスを、条件を満足するメモリアドレスの共通部分として、抽出する。

(もっと読む)

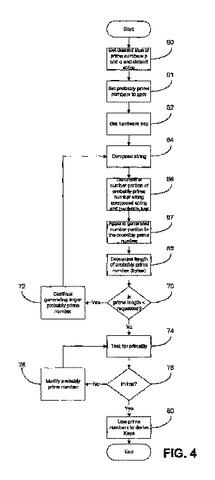

デバイス依存RSAキーの生成

暗号化データを他の電子装置と交換するための携帯電子装置(10)が、プロセッサ(22)と、該プロセッサと動作可能に結合されたメモリ(16)と、該プロセッサ及びメモリと動作可能に結合された素数生成回路(12a)とを含む。素数生成回路は電子装置内の一意の格納済みデータに基づいて少なくとも2つの素数を生成する論理回路を含むと共に、前記少なくとも2つの素数は常に同じ少なくとも2つの素数である。次いで、生成された素数は、電子装置(10)内においてRSA公開キーと秘密キーとを生成するために用いることができる。  (もっと読む)

(もっと読む)

素数生成プログラム、該プログラムを記録した記録媒体、素数生成装置および素数生成方法

【課題】2のべき乗長以外の素数を確定的な素数判定(生成)手法を用いて効率的に生成すること。

【解決手段】所望の素数Pnのビット長の指定を受け付け、指定を受け付けた素数Pnのビット長に従って、素数{P1,…,Pn-1}の各ビット長を事前に算出する。そして、算出された素数{P1,…,Pn-1}の各ビット長に基づいて、素数Pi(1≦i≦n−1)と乱数riとを利用して、素数Piのビット長より長いビット長でかつ素数Piより大きな値の素数Pi+1を順次生成することにより、最終的に所望の素数Pnを生成することができる。

(もっと読む)

圧縮されたRSAモジュラスを生成する方法及び装置

少なくとも2つの係数を有するRSAモジュラスの係数を所定の部分Nhにより生成する方法及び装置。第1素数pが生成され、モジュラスNの一部を構成するNhの値が取得され、pqがNhを共有するRSAモジュラスとなるように、第2素数qがp及びNhに依存した区間において生成され、モジュラスNの計算を可能にする情報が出力される。  (もっと読む)

(もっと読む)

素数生成プログラム

【課題】 各素数候補の試行割算後の本格的素数判定に関し、高速化を図る。

【解決手段】 本格的素数判定に用いられる「ミラー-ラビンテスト」は、1つの底における素数判定が合格の場合、素数である可能性が高い。言い換えると、不合格の場合には、1つの底における素数判定で不合格となる傾向がある。従って、1つの底における「ミラー-ラビンテスト」、一般的には「pの本格的素数判定(途中まで)」を先に行う構成にすることにより、「ミラー-ラビンテスト(1つの底におけるテスト)(ST4)」、一般的には「pの本格的素数判定(途中まで)(ST4’)」が不合格となる場合に、以後の処理(ステップST5〜ST9または、ステップST5’〜ST9’)を実行せずに済む。このため、各素数候補の試行割算後の本格的素数判定に関し、以後の処理(ST5〜ST9または、ステップST5’〜ST9’)の分だけ高速化を図ることができる。

(もっと読む)

素数生成装置、プログラム及び方法

【課題】セーフプライム形の素数に限定されず、第1素数の多項式の形をもつ第2素数を高速に生成する。

【解決手段】第1素数pと、この第1素数pから算出可能で定数項(a0)が0ではない多項式f(p)(=an・pn + an-1・pn-1 + … + a2・p2 + a1・p + a0)の形をもつ第2素数f(p)とを生成する構成により、セーフプライム形の素数(2p+1)に限定されず、第1素数pの多項式の形をもつ第2素数f(p)を生成できる。これに加え、高速に計算可能な試行割算を先に行った後に、フェルマーの小定理を含む本格的な素数判定法を行う構成により、時間のかかる本格的な素数判定法の実行割合を減少できるので、前述した第1及び第2素数p,f(p)を高速に生成できる。

(もっと読む)

複素数及び行列による強化RSA系暗号

【課題】離散対数問題に難読性の根拠を置く暗号の強度を向上させる。また、RSA暗号の鍵を高速に作成する。

【解決手段】同じ因数が重複して含まれる合成数を法としても1と合同になる一般化されたフェルマーの小定理を導出し、これを利用する。また、因数に関する関係式を用いて、最大公約数からも秘密鍵と公開鍵の逆数の関係にある2数を計算する。 また、離散対数問題の強度の向上については、複素数、または行列の離散対数問題を利用する。

(もっと読む)

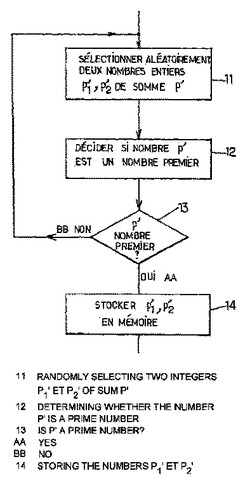

暗号計算を実行するための方法及び装置

本発明は、電子装置における特定の暗号アルゴリズムのための鍵を生成する方法に関し、電子装置に素数Pを格納し、少なくとも一つの秘密の素数を生成する。第1のステップ(a)では、和が数p’に等しい二つの整数p1’及びp2’を無作為に選択する(11)。第2のステップ(b)では、前記数p’の秘密を維持するために、格納された素数Pと数p1’及びp2’との組合せに基づき、数p’が素数であるかどうかを判定する(12)。第3のステップ(c)では、もし数p’が素数であると判定されれば、数p1’及びp2’を電子装置に格納し(14)、そうでなければ、ステップ(a)と(b)を繰り返す。  (もっと読む)

(もっと読む)

素数算出装置、鍵発行システム及び素数算出方法

素数の算出を行う際に、簡単な管理により重複を避けながら素数を算出する素数算出装置を提供する。 素数算出装置は、既知の素数qと、素数の利用範囲における一意の管理情報を記憶している。素数算出装置は、管理情報を読み出し、読み出した管理情報に依存する攪乱情報Rを生成し、素数qを読み出し、読み出した素数qと生成した攪乱情報Rとを用いて、数N=2×攪乱情報R×素数q+1により、素数候補Nを算出し、算出された素数候補Nが素数であるか否かを判定し、素数であると判定された場合に、算出された素数候補Nを素数として出力する。これにより、素数算出装置は、一意の管理情報から、重複を避けながら素数候補を算出することができる。 (もっと読む)

素数算出装置、鍵発行システム及び素数算出方法

正当に生成されたものであるか否かを確認できる素数を算出する素数算出装置を提供する。 素数算出装置は、乱数を生成し、管理識別子に前記乱数を乗じて乗算値Rを算出し、2×w×素数q+1=検証値 (mod 管理情報)を満たすwについて、N=2×(乗算値R+w)×素数q+1により、素数候補Nを算出する。次に、算出された素数候補Nが素数であるか否かを判定し、素数であると判定される場合に、算出された素数候補Nを素数として出力する。 (もっと読む)

1 - 18 / 18

[ Back to top ]