Fターム[5J104AA24]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 目的、効果 (22,786) | 演算方法の改善(高速化・効率化・簡素化) (933) | 素数判定に関する (13)

Fターム[5J104AA24]に分類される特許

1 - 13 / 13

半導体装置及びICカード

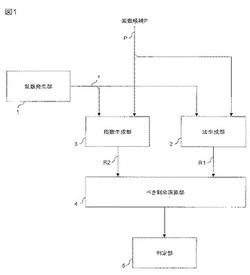

【課題】暗号に対するサイドチャネル攻撃から防御するために、素数性判定を行う半導体装置において、素数の漏えいを防止する。

【解決手段】素数性判定におけるべき剰余演算において、従来の指数のランダム化に加え、法をもランダム化する。乱数発生部により発生した乱数をランダム化数として、法生成部と指数生成部に入力する。法生成部と指数生成部は、ランダム化数を用いて素数候補Pをランダム化し、ランダム化された法R1と指数R2を生成する。ランダム化された法R1と指数R2を用いて素数性判定のためのべき剰余演算を実行し、その結果に基づいて、素数性候補Pの素数性を判定する。半導体装置の素数性判定中の消費電力が、判定対象の素数候補の値と無相関となり、サイドチャネル攻撃による素数の漏えいを防止することができる。

(もっと読む)

情報処理システム、情報処理方法、及びプログラム

【課題】乱数生成能力と素数判定能力とを有する情報処理システムにおいて、並列に行われる素数生成処理を効率化する。

【解決手段】生成ユニットは、乱数を生成し、かつ生成した乱数のビット列の少なくとも一部を、少なくとも1つの判定ユニットに送信する。判定ユニットは、少なくとも1つの生成ユニットから送信されたビット列を組み合わせて所定ビット数の数値を生成し、生成した数値が素数であるか否かを判定し、かつ素数であると判定された数値を出力する。制御手段は、生成ユニットが乱数を生成するのに要する時間と、判定ユニットが数値について素数であるか否かを判定するのに要する時間とが近くなるように、複数の処理ユニットの一部若しくは全部のそれぞれを生成ユニット又は判定ユニットとして動作させる制御を行う。

(もっと読む)

情報処理装置、情報処理方法、及びコンピュータプログラム

【課題】乱数生成能力と素数判定能力とを有する情報処理装置において、より効率的に素数を生成する。

【解決手段】入力された数値が素数であるか否かを判定しかつ素数である場合に該数値を出力する複数の判定手段を備える。複数の乱数シードを取得し、1以上の判定手段が所属するそれぞれの判定グループに複数の乱数シードの何れかを対応付ける。乱数シードを用いて生成した乱数を、該乱数シードに対応付けられた判定グループに入力する。ここで、着目乱数シードを用いて、乱数を生成する乱数生成系列を初期化する。乱数生成系列を用いて乱数を生成する。乱数のビット列を所定ビット数のビット列へと分割する。分割によって得られたそれぞれのビット列が示す数値を、着目乱数シードに対応付けられた判定グループを構成する判定手段の何れかへと出力する。

(もっと読む)

情報処理装置、情報処理方法、及びプログラム

【課題】複数の演算ユニットを用いた並列処理において、より高速に素数を求める。

【解決手段】複数の演算ユニットのうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。複数の演算ユニットのそれぞれは、乱数発生処理の実行が指示されると、メモリに格納されているシードを用いて乱数を生成し、メモリに格納されているシードを生成した乱数で更新し、生成した乱数が素数であれば、該生成した乱数を出力する。乱数発生処理の実行を指示した演算ユニットによる更新処理が完了したことを検知すると、演算ユニットとは別の演算ユニット群のうち何れか1つを選択し、選択した演算ユニットに対してメモリに格納されているシードを用いた乱数発生処理の実行を指示する。

(もっと読む)

素数判定方法、素数判定装置および素数判定プログラム

【課題】 所定の範囲の既知の素数のみに基づき、大きな対象数についても判定可能な素数判定方法、素数判定装置および素数判定プログラムを提供する。

【解決手段】 対象数N(Nは正の整数)が素数であるか否かを判定する素数判定方法であって、対象数Nの入力を受け付ける入力受付過程と、対象数Nを除する除数の範囲を定める範囲規定過程と、対象数Nを除数で除して、対象数Nが素数であるか否かを判定する素数判定過程と、対象数Nが素数であるか否かの結果を出力する結果出力過程と、を備え、範囲規定過程は、小さいほうからP(Pは2以上の整数)個の素数を掛け合わせた数を素数階乗数MPとして、N1/2/MPの小数点以下を切り上げた規定数Rを算出するものであり、素数判定過程は、整数を1からMP列に並べた配列において、第1行の素数およびR≧2なら第2行から第R行までの第1列およびMPを構成する素数を除いた素数列の数を除数とする。

(もっと読む)

双曲線暗号の設計ツール

【課題】2次双曲線群はその位数が一定で初等的取り扱い方が可能であるが、複数の単位暗号化装置を具備する鍵生成装置において多数の曲線パラメータの組を特定する作業が必要になる。例えば、整数論的関数で、法p及び曲線パラメータa,b,cを定めなければならない。従って、これ等の曲線パラメータ等を簡易に生成できるツール(ソフトウェア)を提供する。

【解決手段】双曲線暗号の設計ツールであって、素数テストツール、2次双曲線群設計ツール、2次双曲線群解析ツール、拡張2次双曲線群解析ツール等から構成されている複合ツールで、このツールだけで設計と解析が完結する構成を有している。

(もっと読む)

RSAアルゴリズムにおける素数生成の保護

【課題】本発明は、例えば、電子回路の電力消費の分析等によるサイドチャネル攻撃、又は故障注入攻撃から電子回路における素数の生成を保護する方法を提供する。

【解決手段】連続した候補数の素数特性の判定に基づく電子回路による少なくとも1つの素数の生成を保護する方法において、前記候補数毎に、少なくとも1つの第1の乱数を含む参照数を計算し、累乗モジュールの計算に基づく少なくとも1つの素数判定を行い、前記素数判定により素数であると判定された候補数毎に、前記候補数と前記参照数との間の無矛盾性を判定する。

(もっと読む)

データ処理装置

【課題】メモリ容量を消費せずに高速にフェルマーテストによって素数判定を行うことができるデータ処理装置を提供する。

【解決手段】2を元としたフェルマーテストをモンゴメリ剰余乗算コプロで実行するための高速耐タンパ手法であって、指数をmビットごとにまとめて乗算するm-ary法を実施する際に、剰余乗算に補正値を含めることで、モンゴメリ剰余乗算コプロを用いた場合に通常必要となる、事前計算や事前計算した値を格納するワークエリアの確保を不要とした。暗号鍵を生成するための素数生成を高速化する場合、大量のメモリや事前計算が必要になることや、消費電流などのリーク情報から内部で生成される暗号鍵が推定されることを解決することができる。

(もっと読む)

データ処理システム及びデータ処理方法

【課題】ICカードのように限られた記憶資源しか持たなくても効率的な暗号化処理の実現に資することができる技術を提供する。

【解決手段】暗号鍵の生成システムは、多数の小さい素数を再構成するための演算ユニット、小さい素数によって整数が割り切れるかを点検するための篩ユニット、整数の表現を変えるための再符号化ユニット、及び素数性判定テストユニットを備える。篩ユニットは最初に演算ユニットによって再構成される小さい素数によって整数が割り切れることを点検し、これによって「不適当な」素数候補を取り除く。その後、残りの素数候補は素数性判定テストユニットを使用してテストされる。このとき、再構成ユニットを使用して素数候補の表現が変換され、変換された表現形態を用いて素数性判定テストユニットが判定する。これにより、大きなメモリ容量を必要とすることなく、素数性判定のための演算処理数を減少することができる。

(もっと読む)

記憶位置抽出装置および記憶位置抽出方法

【課題】共通部分抽出に必要となる処理の並列化を可能とし、処理全体の効率化を図って処理時間を高速化することを課題とする。

【解決手段】共通アドレス抽出装置10は、各バイトに対して篩処理一回目のログ加算処理を実施し、一回目のログ加算処理が終了した後の各バイトの値に対して、条件を満足するバイトのアドレスに付属するパリティビットをオンとする。続いて、共通アドレス抽出装置10は、パリティビットの値を保持した状態のまま、各バイトに対して篩処理二回目のログ加算処理を実施する。そして、共通アドレス抽出装置10は、二回目の篩処理が終了した後のバイトが保持する値それぞれに対して、条件を満足しないバイトのアドレスに付属するパリティビットをオフとする。その後、共通アドレス抽出装置10は、対応するパリティビットの値が1であるバイトのアドレスを、条件を満足するメモリアドレスの共通部分として、抽出する。

(もっと読む)

情報処理方法、情報処理装置、および情報処理プログラム

【課題】数値表現の自由度の向上を図ること。

【解決手段】入力数値NをN=350460とする。(A)において、入力数値Nが入力されるとルートRを設定する。(B)において、数列S4を元に9本のブランチを生成する。ブランチの先端に配置された数値が分岐先ノードとなる。(C)に示すように、リーフ((C)中、ノードRより小さい●で表示)に変換する。数値が2以上のノードについては、素因数分解可能である。(D)では、数値「12」のノードからブランチを3本生成し、数列S4を構成する各数値を分岐先ノードとする。数値が1となる分岐先ノードはリーフ((D)中、ノードRより小さい●で表示)に変換する。(D)中、数値が2以上のノードについては、素因数分解可能である。このようにして、(E)に示したように、入力数値Nに固有なツリー構造データT(N)を生成することができる。

(もっと読む)

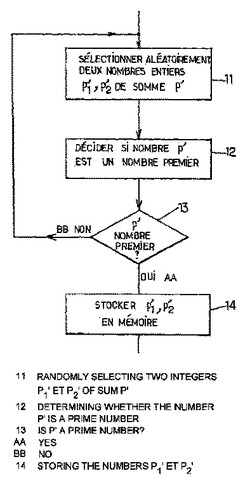

暗号計算を実行するための方法及び装置

本発明は、電子装置における特定の暗号アルゴリズムのための鍵を生成する方法に関し、電子装置に素数Pを格納し、少なくとも一つの秘密の素数を生成する。第1のステップ(a)では、和が数p’に等しい二つの整数p1’及びp2’を無作為に選択する(11)。第2のステップ(b)では、前記数p’の秘密を維持するために、格納された素数Pと数p1’及びp2’との組合せに基づき、数p’が素数であるかどうかを判定する(12)。第3のステップ(c)では、もし数p’が素数であると判定されれば、数p1’及びp2’を電子装置に格納し(14)、そうでなければ、ステップ(a)と(b)を繰り返す。  (もっと読む)

(もっと読む)

素数算出装置、鍵発行システム及び素数算出方法

正当に生成されたものであるか否かを確認できる素数を算出する素数算出装置を提供する。 素数算出装置は、乱数を生成し、管理識別子に前記乱数を乗じて乗算値Rを算出し、2×w×素数q+1=検証値 (mod 管理情報)を満たすwについて、N=2×(乗算値R+w)×素数q+1により、素数候補Nを算出する。次に、算出された素数候補Nが素数であるか否かを判定し、素数であると判定される場合に、算出された素数候補Nを素数として出力する。 (もっと読む)

1 - 13 / 13

[ Back to top ]