Fターム[5J104NA25]の内容

暗号化、復号化装置及び秘密通信 (108,990) | 構成要素 (27,346) | 物理的構成要素 (16,068) | マルチプレクサ・デマルチプレクサ (8)

Fターム[5J104NA25]に分類される特許

1 - 8 / 8

プログラマブル・ロジック・デバイス

【課題】ダイナミック・リコンフィギュラブル・LSI等のプログラマブル・ロジック・デバイスにおいて、算術論理演算以外の演算であるデータの並べ替えや適切なビット配置等の処理を行う場合においても、演算器を使用するために回路規模が大きくなる。

【解決手段】プログラマブル・ロジック・デバイス101は、各々外部からの設定によって毎サイクル機能変更が可能であり、かつ64ビットの入力信号を任意の順番に並べ替えて64ビット信号を出力することが可能な第1の並べ替えセル104を複数内蔵する。

(もっと読む)

パケット化トランスポート・ストリームの処理方法

【課題】エンタイトルメント・データが直ちにプログラム・マテリアルを受信するための権利を否定するように階層化されたシステムを提供する。

【解決手段】本装置は、条件付きアクセス・ペイロード・ヘッダと残りの権利付与データのペイロードを含むペイロードを有する信号パケットを選択するパケット・トランスポート・プロセッサを含む。各ペイロード・ヘッダは、受信機が権利付与データを処理することを可能または不能にするように符号化されるバイトのグループを含む。加入者固有の条件付きアクセス・コード・ワードで予めプログラムされたフィルタは、加入者固有の条件付きアクセス・コード・ワードと一致させるために条件付きアクセス・ヘッダのそれぞれのバイトのグルーピングを検査する。一致が生じる場合、プロセッサは権利付与データを処理する。権利付与は伝送信号の暗号解読部のための暗号解読キーを生成するために利用される。

(もっと読む)

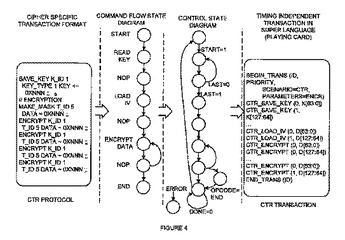

暗号化ハードウェアサービスのための暗号独立型のインターフェース

暗号独立型の暗号化ハードウェアサービスが開示される。暗号独立型のトランザクションが入力スロット内に受信される(202)。当該入力スロットは当該トランザクションを維持するためのFIFOを含む。当該トランザクションが当該FIFOから除去されるにつれて、当該トランザクションは暗号独立型の形態から暗号依存型の形態に変換されて(206)暗号依存型のタイミングに変換される。暗号固有のハードウェアによる暗号化処理の後、それらの結果は出力FIFOに送られる(212)。複数の暗号化機能が並行して、かつ同時に実行されることが可能なように、複数のFIFO及び暗号化ハードウェアが使用され得る。  (もっと読む)

(もっと読む)

暗号処理装置

【課題】FO関数及びFL関数の演算において、FO関数の演算結果を格納する中間レジスタを不要にする暗号処理装置を提供する。

【解決手段】2Nビットの入力と第1拡大鍵とに基づいてFL関数の演算を行って2Nビットの出力を生成するFL関数演算部と、Nビットの入力と第2拡大鍵と第3拡大鍵とに基づいてFI関数の部分関数の演算を行ってNビットの出力を生成する部分関数演算部と、部分演算部の出力を記憶するNビットの中間レジスタと、FL関数演算部の出力に基づくデータを記憶することができる2Nビットの第1データレジスタと、FL関数がFO関数の演算結果を用いる第1ケースにおいて、部分関数演算部に部分関数の演算を6サイクル行わせ、中間レジスタの出力をFL関数演算部へ入力し、FL関数演算部の出力に基づくデータを第1データレジスタへ記憶させる制御部とを有する。

(もっと読む)

誤り検出機能を備える、符号化又は復号処理のための回路構成

【課題】符号化・復号回路の動作時のエラー検出を確実に行い、かつ回路規模と動作速度に対するペナルティを軽微なものとする回路構成を提供すること。

【解決手段】あるステージにおいて符号化処理が実行されている時、その1つ前段のステージでは、直前のサイクルにおける符号化処理の検証としての復号処理が並行して実行される。復号されたデータは、直前のサイクルにおいて符号化の対象となったデータと比較されて、一致しているかどうかが調べられる。その次のサイクルでは、当該ステージにおいて先に符号化されたデータが復号され、符号化される前のデータと一致しているかどうかが調べられる。並行して、先に符号化されたデータに対して次段のステージで符号化処理が進められ、前段のステージには新たなデータが入力されて符号化処理が行われる。

(もっと読む)

半導体集積回路

【課題】AES方式の暗号化及び復号化における処理を、論理回路を中心とするハードウェアと、ソフトウェアに基づいて動作するマイクロプロセッサとに分担させることによって、所望の処理スループットを実現しつつ回路規模又は消費電力を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路で、暗号処理において用いられる少なくとも1つの鍵及び複数の制御信号を生成するマイクロプロセッサと、複数の入力データ群と複数の帰還データ群との内の一方を選択する選択回路と、選択回路から出力される複数のデータ群を格納する格納回路と、前処理として複数の帰還データ群を生成して帰還ループに供給すると共に、その後、複数の帰還データ群を順次用いて行った演算結果を変換テーブルを参照して変換することにより複数の入力データ群に対して暗号化又は復号化処理を施す論理回路とを具備する。

(もっと読む)

暗号処理回路

【課題】共通鍵ブロック暗号方式の換字処理を行う暗号処理回路において、ハードウェアを修正せずに換字処理における入力データと出力データとの対応規則を変更可能とすることにより、安全性を高める。

【解決手段】複数ビットの入力データを変換して出力する共通鍵ブロック暗号方式の換字処理を行う暗号処理回路であって、前記入力データと、前記入力データの並べ替えを指示する選択データと、を受信し、前記入力データを前記選択データに基づいて並べ替えたデータを所定の対応規則に基づいて変換して出力する論理回路であることとする。

(もっと読む)

暗号処理回路

【課題】共通鍵ブロック暗号方式における暗号化及び復号の処理を低消費電力で、かつ、高速に行う。

【解決手段】複数ビットの入力データをビット毎の対応規則に基づいて並べ替えて出力する共通鍵ブロック暗号方式の転置処理を行う暗号処理回路であって、前記入力データを受信し、受信した前記複数ビットの入力データを並列出力する出力ポートを有するデータ入力部と、複数ビットのデータが並列入力される入力ポートを有し、前記入力ポートに入力された前記データを出力するデータ出力部と、前記出力ポートと前記入力ポートとを、前記ビット毎の対応規則に基づいて接続する転置部と、を備える。

(もっと読む)

1 - 8 / 8

[ Back to top ]