Fターム[5J106AA03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583)

Fターム[5J106AA03]の下位に属するFターム

PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA03]に分類される特許

21 - 40 / 171

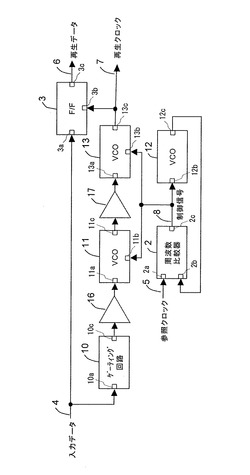

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

同期信号生成装置、同期信号生成方法

【課題】ホールドオーバ状態からGPS通信衛星の電波を捕捉できる状態に復帰した場合、もしくはGPS通信衛星の電波を捕捉している状態からホールドオーバ状態に移行した場合、高精度の同期を迅速に行う同期信号生成装置、同期信号生成方法を提供することを課題としている。

【解決手段】同期信号生成装置1は、同期信号抽出部11と、制御部12と、同期部13と、DAC部(デジタル信号−アナログ信号変換部)14と、発振部15とを備えている。また、同期信号生成装置1には、GPS通信衛星アンテナ3と、基地局5とが接続されている。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

送信装置および通信システム

【課題】 従来の送信装置では、クロックとデータとの間のスキューが変動した場合にも高精度の通信を実現することが困難であった。

【解決手段】 N(Nは自然数)ビットの第1のパラレルデータ信号を、基準クロックをN逓倍した第1変換クロックでパラレル/シリアル変換を行い、N×K(Kは自然数)ビットの第2のパラレルデータ信号を、基準クロックをN×K逓倍した第2変換クロックでパラレル/シリアル変換を行う。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

双方向無線通信システム、無線通信装置及び双方向無線通信方法

【課題】PLL回路を含んだ回路に比べて周波数同期回路等を簡単な回路によって構成できるようにする。

【解決手段】入力信号を変調した変調信号に所定の搬送周波数の基準搬送信号を重畳して送信信号を送信する双方向用のTRX1と、通信許可信号を生成するTRX2とを備える。TRX2は自走発振周波数の信号を発振する発振器を有している。TRX2は、TRX1から受信した受信信号を発振器23に注入する。これと共に、発振器23の自走発振周波数を可変制御しながら受信信号を受信し、発振器23の信号の自走発振周波数が注入同期に至る周波数範囲に入って注入した受信信号の搬送周波数に周波数同期したか否かを検出する。TRX2は、発振器23の信号の自走発振周波数が、注入した受信信号の搬送周波数に周波数同期したことを検出したときに、通信許可信号をTRX1に送信するものである。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

半導体装置

【課題】搭載された異なるPLL回路の夫々の出力信号の同期化を実現する半導体装置を提供する。

【解決手段】所定の周波数の信号を入力し、当該入力信号の整数倍の周波数の信号を当該入力信号と同期させて出力する、2つの異なるPLL回路(2、4)によって同期化された信号を夫々分周し、当該分周した信号の位相差に応じた所定の遅延量に基づいて一方のPLL回路(2)の出力信号を遅延させることで、他方のPLL回路(4)の出力信号(42)に同期させたクロック信号(41)を生成する。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】比較的小さな電源電圧による速度変動を高精度で抑制して比較的大きな電源電圧による速度変動を高速で抑制する。

【解決手段】半導体集積回路は、第1と第2の機能ブロックMOD00、01、クロック生成回路PLL、クロック供給回路CS0を具備する。第1と第2の機能ブロックMOD00、01には、電圧値の相違する第1と第2の電源電圧VDD00、1が供給される。MOD00は一方の電源電圧VDD01が供給可能な第1の内部回路BUF00と第1の論理回路MFF00を含み、MOD01は他方の電源電圧VDD00が供給可能な第2の内部回路BUF01と第2の論理回路MFF01を含む。クロック供給回路CS0は微調遅延段回路FC0と粗調遅延段回路CC0と位相差計測回路RSM0を含み、RSM0は第1と第2の動作クロック信号COUT00、01の位相差に応答してFC0の遅延時間TF0とCC0の遅延時間TC0を制御する。

(もっと読む)

遅延ロックループ回路、半導体集積回路装置

【課題】低い周波数から高い周波数までの幅広い周波数帯域に対応して、回路面積の小さい遅延ロックループ回路、その遅延ロックループ回路を搭載する半導体集積回路装置を提供する。

【解決手段】遅延ロックループ回路は、位相変更回路と、遅延線回路と、遅延制御回路とを具備する。位相変更回路は、入力される基準クロックに対して第1の位相差を有する第1の信号と、第2の位相差を有する第2の信号とを出力する。第1の位相差と第2の位相差との差分は所定の位相遅延量を示す。遅延線回路は、変更可能な単位遅延量を備える遅延回路を複数含む。遅延制御回路は、単位遅延量の合計が基準位相遅延量になるように単位遅延量を制御する。

(もっと読む)

位相調整装置及び方法

【課題】CCDを駆動するクロック信号を自動的に最適な位相に調整し、CCDからクロック信号成分が出力されない位相調整装置及び方法を提供する。

【解決手段】本発明の位相調整装置は、2相駆動型の電荷結合素子を用いたフィルタ回路に入力する第1の信号及び第2の信号の位相関係を調整する位相調整装置において、第1の信号に対して遅延を与える遅延付与手段と、遅延付与手段により遅延が与えられた第1の信号と、第2の信号とを加算又は減算する合成手段と、合成手段から出力する参照信号の電力値に基づいて、第1の信号と第2の信号とが逆位相となるように遅延付与手段の遅延設定量を制御する位相調整制御手段とを備えることを特徴とする。

(もっと読む)

異種周期クロックドメイン間の同期化システム、同期化装置、同期化失敗検出回路及びデータ受信方法

【課題】異種周期クロックドメイン間の同期化システム、同期化装置、同期化失敗検出回路及びデータ受信方法を提供する。

【解決手段】本発明の一様態による同期化システムは、異種周期の第1クロックと第2クロックとによってそれぞれ動作するセンダーとレシーバーを含む異種周期クロックドメイン間の同期化システムであって、第1クロックを第1時間遅延させた予測クロックを出力するセンダー及び予測クロックを利用して第1クロックと第2クロック間の同期化失敗が発生するか否かを予測し、予測結果によって選択的に第2クロックを第2時間遅延させて第1クロックと同期化させるレシーバーを含む。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】DLL回路のロックに要する時間を短縮する。

【解決手段】外部クロック信号CLKとレプリカクロック信号RCLKの位相差量を検出する位相差量検出回路100と、位相差量に基づいて外部クロック信号CLKを遅延させることにより内部クロック信号LCLKを生成する可変遅延回路21と、内部クロック信号LCLKを遅延させることによりレプリカクロック信号RCLKを生成するレプリカバッファ24とを備える。本発明によれば、外部クロック信号CLKに対してレプリカクロック信号RCLKの位相が進んでいるか或いは遅れているではなく、その位相差量に基づいて可変遅延回路21が制御されることから、位相差量が大きい場合であっても、高速にDLL回路をロックさせることが可能となる。

(もっと読む)

同期信号生成装置及び同期信号生成方法

【課題】コストの増大を抑止しつつ、障害発生時にも複数装置間の同期を障害回復まで維持することを可能とすること。

【解決手段】同期信号生成装置であって、他の装置との間で同期をとるための信号を受信し、受信された信号に基づいて第一同期用信号を出力する受信部と、第一同期用信号と所定のずれを生じながら第二同期信号を出力する発振部と、第一同期用信号と第二同期用信号とのずれを予め記憶する記憶部と、受信部が信号を受信している場合には第一同期信号に基づいて同期信号を出力し、受信部が信号を受信していない場合には第二同期信号及び記憶部に記憶されるずれに基づいてずれを補正することにより同期信号を出力する同期信号生成部と、を備える。

(もっと読む)

遅延固定ループ回路およびこれを利用した半導体メモリ装置

【課題】入力されるソースクロックREFCLKと、出力される遅延固定クロックDLLCLKとの間の位相差が最大値に達するか否かを検知し、レジスタ制御型遅延固定ループ回路の動作を制御することができる遅延固定ループ回路を提供する。

【解決手段】ソースクロックの位相とフィードバッククロックの位相とを比較し、比較結果に対応して遅延固定信号を生成する位相比較部200と、前記遅延固定信号に応答して、前記ソースクロックを遅延させて遅延固定クロックとして出力し、限界遅延量に達した後にも遅延固定が行われない場合に遅延終了信号を活性化させるクロック遅延部220と、前記遅延固定クロックに前記ソースクロックの実際の出力経路の遅延時間を反映し、前記フィードバッククロックとして出力する遅延複製モデル部240と、前記遅延固定信号および前記遅延終了信号に応答して遅延固定動作を終了させる遅延固定動作制御部250とを備える。

(もっと読む)

周波数同期装置、受信機および周波数同期方法

【課題】インパルス状の外乱が生じる環境でも、精度の良い周波数同期を確立することができる周波数同期装置を得ること。

【解決手段】再生周波数を受信信号に同期させる周波数同期制御を行う周波数同期装置であって、受信信号に基づいて周波数偏差を求める周波数偏差検出部2と、周波数偏差の時間変化量を算出する差分部3と、時間変化量に基づいて、前記周波数偏差を周波数制御値として用いるか否かを示す制御値選択信号を生成する観測部6と、制御値選択信号が周波数偏差を周波数制御値として用いないことを示す値であった場合には、過去の周波数制御値に基づいてその時点での周波数制御値の推定値である推定制御値を求め、求めた推定制御値を周波数制御値として選択するホールド部7と、を備える。

(もっと読む)

21 - 40 / 171

[ Back to top ]