Fターム[5J106AA03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583)

Fターム[5J106AA03]の下位に属するFターム

PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA03]に分類される特許

61 - 80 / 171

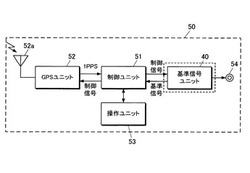

基準信号発振装置

【課題】使用する無線通信の周波数帯が変更された場合に、基準信号の周波数の精度を容易且つ適切に変更することである。

【解決手段】GPS信号を受信してUTCに同期した時間信号を取得するGPSユニット52と、基準信号を発振する基準信号ユニット40と、基準信号ユニット40により発生された基準信号のパルス数を測定する測定時間、又は基準信号の周波数の精度の操作入力を受け付ける操作ユニット53と、GPSユニット52により取得された前記時間信号に基づいて、操作ユニット53により入力された測定時間、又は前記入力された精度に対応する測定時間をカウントするとともに、当該測定時間内の前記基準信号のパルス数を測定し、正確なパルス数からの前記測定したパルス数の誤差をなくすように基準信号ユニット40が発生する基準信号の周波数を補正する制御ユニット51と、を備える。

(もっと読む)

タイミング信号発生回路

【課題】 種々の時間間隔のタイミング信号を低コストで正確に発生させる。

【解決手段】 クロック回路と、クロック信号を入力するカウント回路と、外部から入力する基準タイミング信号を取得し、少なくとも2以上の基準タイミング信号を含む所定の2時点間のカウント回路のカウント値の増分と、該2時点間の時間とを対応させて記録する記憶回路と、カウント回路が所定の2時点間に対応するカウント値だけ増分した時点を中心とする所定の期間に基準タイミング信号を取得し、基準タイミング信号を受信した時点のカウント回路のカウント値を所定の2時点間に対応するカウント値として記録し、所定の2時点間の時間を周期とするタイミング信号をカウント回路のカウント値の増分を契機として発生させ、さらに基準タイミング信号を取得し、基準タイミング信号を取得した時点からカウント値の増分を計数し直す制御手段とを備える。

(もっと読む)

位相同期回路及び半導体チップ

【課題】 複数のチップ内の内部回路に供給される動作タイミング用のクロック信号の位相を正確に同期させることができる位相同期回路を提供する。

【解決手段】 第1チップ内において第1クロック信号を遅延させて第2クロック信号を生成し、2クロック信号を第1内部回路の動作タイミング用として第1内部回路に供給する第1遅延手段と、第2クロック信号を遅延させて第3クロック信号を生成する第2遅延手段と、第2チップ内において第1クロック信号を第1チップとの間の第1配線を介して入力し、その入力した第1クロック信号を第2内部回路の動作タイミング用として第2内部回路に供給する入力手段と、第1入力手段によって入力された第1クロック信号を第2配線を介して帰還クロック信号として第1チップに帰還させる帰還手段と、第3クロック信号と帰還クロック信号との位相差が減少するように第1及び第2遅延手段各々の遅延時間を制御する位相比較手段とを備える。

(もっと読む)

CDR回路

【課題】再生クロックのジッタを低減する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスにより発振位相が制御されるクロックを生成するゲーテッドVCO3と、フィードバック入力端子にゲーテッドVCO3の出力クロックが入力され、ゲーテッドVCO3の出力クロックと同じ周波数の再生クロックを生成するVCO4と、入力データを遅延させる遅延回路5と、遅延回路5を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

CDR回路

【課題】製造のばらつきや環境変化あるいは入力データのパルス幅歪に対して強い耐性を持つCDR回路を提供する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、周波数制御信号に応じて発振周波数が制御されかつゲーティング回路2の出力パルスにより発振位相が制御される再生クロックを生成するゲーテッドVCO3と、入力データを遅延させる遅延回路4と、遅延回路4を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。遅延回路4は、ゲーティング回路2と同じ構成の遅延回路であるレプリカ回路40と、ゲーテッドVCO3と同じ構成の遅延回路であるレプリカ回路41とから構成される。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

クロック制御回路、方法、及び、プログラム

【課題】受信データ取り込みに用いるクロック信号の位相を複数回変化させずに、クロックの位相調整が可能なクロック制御回路を提供する。

【解決手段】周期パルス受信部14は、比較用クロックCCLKに基づいて、入力データDATAと共に送信された入力周期パルスFPを取り込み、受信周期パルスFP1として出力する。比較パルス生成部15は、比較用クロックCCLKに基づいて、入力周期パルスFPと同じ周期の期待周期パルスFP2を生成する。制御部12は、比較用クロックCCLKの位相を変化させ、複数の比較用クロックCCLKの位相にて受信周期パルスFP1と期待周期パルスFP2とが一致するか否かを監視し、監視結果に基づいて、受信用クロックRCLKの位相を決定する。

(もっと読む)

高分解能の時間/デジタル変換器

【解決手段】時間/デジタル変換器(TDC)は、インバータの伝播遅延よりも優れた分解能を有し得る。一例では、非整数遅延素子回路は、TDC入力信号を受信し、そこから、第1信号の時間シフトした複製である第2信号を生成する。第1信号は、第1遅延線タイムスタンプ回路(DLTC)に供給され、第2信号は第2DLTCに供給される。第1DLTCは、TDCへの参照入力信号のエッジと第1信号のエッジとの間の時間を示す第1タイムスタンプを生成する。第2DLTCは、参照入力信号のエッジと第2信号のエッジとの間の時間を示す第2タイムスタンプを生成する。第1及び第2タイムスタンプは合成されて、共に高い分解能の全体のTDCタイムスタンプを構成する。これは、第1または第2タイムスタンプよりも優れた分解能を有する。 (もっと読む)

フレームパルス信号ラッチ回路および位相調整方法

【課題】フレームパルス信号とクロックとの位相調整を自動化する。

【解決手段】フレームパルス信号ラッチ回路は、パルス幅をmクロック周期より長くしたフレームパルス信号FPINを出力するパルス幅伸張部1と、位相を調整した出力クロックCLK’を生成する位相調整部3と、フレームパルス信号FPINをラッチするフリップフロップ4と、フレームパルス信号FPOUTに対して、1〜mクロックシフトした各信号を生成し、フレームパルス信号FPOUTとクロックシフトした各信号との論理積の結果に基づいてレーシング状態を検出するレーシング検出部5と、位相調整部3に対して異なる位相調整量を順次選択して指示し、レーシング状態が検出された際の最悪位相調整量に基づいて、最適位相調整量を決定して位相調整部3へ指示する制御部6とを備える。

(もっと読む)

同期確立装置および通信装置

【課題】それぞれの発振器を備えた複数の受信部の同期を容易に確立すること。

【解決手段】現用系A受信部140の同期確立部200は、複数の受信部(140、150、160)それぞれに備えられた第一の発振器230によって生成された互いに周波数が異なる複数の波形信号を入力する入力部(210、220、240)と、入力部によって入力された複数の波形信号に対する論理演算により複数の受信部に共通する波形の共通波形信号を算出する算出部250と、算出部250によって算出された共通波形信号から各受信部内部における処理周波数を規定するローカル信号を生成するPLL部260、第二の発振器270および分周器265と、を備える。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

位相比較器及び測定装置

【課題】2つの信号の位相比較結果を確実に保持できる位相比較器を提供する。

【解決手段】2つの信号CMP、REFの位相を比較して、その位相関係を出力する比較部10と、比較部より出力される位相比較結果を入力信号として受信し信号OUTとして出力するホールド回路30と、比較部の出力に基づいて位相比較結果が確定したか否かを判定し、位相比較結果が確定したと判定した場合にホールド信号Cを出力するホールド信号生成部20とを備え、ホールド回路は、ホールド信号が出力されている期間は前記入力信号を保持するようにして、比較部による位相比較結果が確定する前に状態が保持されることを防止し、位相比較結果を確実に保持できるようにする。

(もっと読む)

半導体素子、クロック同期化回路、及び、クロック同期化回路の駆動方法

【課題】クロック同期化回路は、インジェクションロッキング方式を使用してジッタピーキング現象と制御電圧にパターンジッタが大きくなる現象なく、所望の位相・周波数ロッキング動作を行う。

【解決手段】クロック同期化回路は、基準クロック信号とフィードバックされるフィードバッククロック信号の位相・周波数差を検出信号として出力する位相・周波数検出手段332と、検出信号に応答してチャージポンプ動作を行うチャージポンプ手段334と、チャージポンプ動作に応答して発振制御電圧を生成する制御電圧生成手段336と、発振制御電圧に対応してフィードバッククロック信号を生成する電圧制御発振手段338と、発振制御電圧に応答して自由発振周波数が設定され、基準クロック信号に同期化した内部クロック信号を生成するインジェクションロッキング発振手段310とを具備する。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

DLL回路およびその制御方法

【課題】より迅速な固定完了時間を有し、半導体集積回路の高速化実現をより効率的に支援するDLL回路およびその制御方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックと動作開始信号に応答して初期動作信号を生成する初期動作設定手段と、前記初期動作信号、位相比較信号、および初期設定コードに応答して遅延制御コードを生成するシフトレジスタと、前記初期動作信号および前記遅延制御コードに応答して前記基準クロックまたはフィードバッククロックを遅延させ、複数の単位遅延クロックを生成する遅延ラインと、前記基準クロックと前記複数の単位遅延クロックに応答して前記初期設定コードを生成する初期遅延モニタリング手段とを含むことを特徴とする。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

信号処理装置、信号処理方法、信号処理プログラム及びその記録媒体

【課題】

演算量を低減しつつ、入力信号に精度良く同期した信号を迅速に生成する。

【解決手段】

直交信号生成部110Aが、信号源910AからのサンプルレートfSM1でサンプリングされた信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られ、サンプルレートfSM2(<fSM1)でサンプリングされた信号PWA1,PWA2を生成する。これらの信号PWA1,PWA2に基づいて、位相算出部120Aが、パイロット信号の位相を算出する。こうして算出されたパイロット信号の位相をサンプルレートfSM1に戻した後、パイロット信号の位相に基づいて、基準信号発生部130Aが、パイロット信号と所定関係にある基準信号BSAを生成する。そして、基準信号BSAを利用して、信号加工部140が、信号SIAを加工する。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】クロック生成回路が、ロック状態とは180°位相のずれた状態(擬似ロック状態)の出力クロックを出力する可能性がある。

【解決手段】遅延同期ループ型のクロック信号生成回路として、(a)第1のクロック信号を遅延して第2のクロック信号を生成する遅延線路と、(b)第2のクロック信号が第1のクロック信号に位相同期するように、遅延線路における遅延量を可変制御する遅延量制御部と、(c)第1のクロック信号と第2のクロック信号との擬似ロック状態を検出する擬似ロック検出部と、(d)擬似ロック状態の検出時、遅延線路の遅延量を変更する擬似ロック状態解除部とを有するものを提案する。

(もっと読む)

位相雑音除去装置及び方法、受信装置及び方法、並びにプログラム

【課題】使用予定のダウンコンバータが複数ある場合でも、位相雑音を適切に除去する。

【解決手段】位相雑音除去回路31では、位相雑音量検出器41は、ダウンコンバータ22から供給されるIF信号から位相雑音量を検出し、ゲイン決定回路42は、位相雑音量に応じた、IF信号に対する位相同期で用いられるループゲインを示す対照表を複数有し、その複数の対照表のうちの1つに基づいて、検出される位相雑音量に応じたループゲインを決定し、位相同期回路43は、決定されたループゲインに基づいて、IF信号の位相雑音を除去する。本発明は、例えば、TV受像機等に適用できる。

(もっと読む)

61 - 80 / 171

[ Back to top ]