Fターム[5J106AA03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583)

Fターム[5J106AA03]の下位に属するFターム

PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA03]に分類される特許

121 - 140 / 171

パルス発生回路

【課題】論理回路の動作の遷移時間程度に細いパルスを発生しようとすると論理回路が誤動作し細いスパイク状のノイズが発生するが、このようなノイズ発生の影響を排除する新たなパルス発生回路および該回路を使ったUWB通信システムによって、安定で誤動作のない短パルスの発生回路とUWB通信を実現させる。

【解決手段】縦続接続されたN段(Nは正の整数)の遅延回路と、前記遅延回路の各段の出力の積をとる乗算回路とで構成する。

(もっと読む)

パルス発生回路および電子回路

【課題】論理回路の動作の遷移時間程度に細いパルスを発生しようとするときに論理回路が誤動作し細いスパイク状のノイズが発生することを排除し、安定で誤動作のない短パルスの発生回路を実現させる。

【解決手段】縦続接続されたM段(Mは正の偶数)の遅延回路と、前記遅延回路のi(iは1≦i≦Mの偶数)段目の出力Diおよび前記遅延回路のi−1段目の出力の否定論理XDi-1の論理積をとる論理積回路と、前記論理積回路出力の論理和を取る論理和回路と前記遅延回路の初段目の出力D1の否定論理XD1および前記遅延回路の最終段目の出力DMの論理積XD1DMが偽の間の所定のタイミングに信号を出力する論理回路と前記論理回路出力が真のとき前記論理積回路または前記論理和回路の少なくとも一方を非活性にする手段とを備えて構成する。

(もっと読む)

クロック信号のデューティサイクルを補正するための補正装置

【課題】クロック信号のデューティサイクル補正を行うために、確実かつ簡便に実現される技術を提供する。

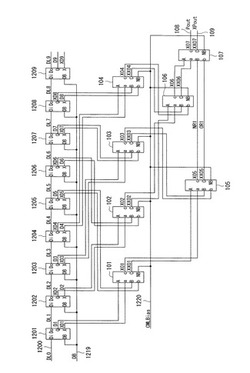

【解決手段】クロック信号(CLK)から第1グループおよび第2グループのn個の遅延された各バージョンをそれぞれ生成するために各遅延デバイス(DA、DB)を設ける。第1グループの各バージョンでは前側エッジが後側エッジに対して時間増分τだけずつ段階的に遅延し、第2グループの各バージョンでは後側エッジが前側エッジに対して時間増分τだけずつ段階的に遅延する。第1グループの信号が消失する点での遅延増分値の順序数xを確定する。第2グループの各信号が発振が消失する点での遅延増分値の順序数yを確定する。遅延補正デバイス(DC)を、x>yまたはx<yである場合にクロック信号のパルスの前側エッジまたは後側エッジを(V=τ×|x−y|/2)だけ遅延して補正クロック信号CLK’を得るために制御可能に設ける。

(もっと読む)

DLL回路

【課題】Delay Locked Loop回路(DLL回路)の源クロック停止、動作中の源クロック周波数変化などの異常動作時にも、自動的にリセットを行い、正常ロックさせることが可能な擬似ロック防止回路を提供することを目的とする。

【解決手段】1はチャージポンプ回路、2は位相遅延回路、3は位相比較器、4は位相制御回路、5はリセット回路、8はチャージポンプ電圧比較回路、9は擬似ロック基準電圧発生回路である。ロック周波数による必要電圧は1のチャージポンプの電圧によって決定されるため、このチャージポンプ電圧を8のチャージポンプ電圧比較回路によりモニターし、9の擬似ロック基準電圧発生回路によって生成される、周波数ごとに変化する擬似ロック判定電圧レベル、源クロック停止判定電圧レベルと比較することで擬似ロック、源クロック停止、源クロック周波数変動を認識する。

(もっと読む)

発振器結合システム

【課題】ノイズ抑制の困難度を簡易な回路素子で簡単化するための発振器結合システムを提供する。

【解決手段】複数の発振素子と、複数の遅延素子とを備え、該遅延素子は、少なくとも2つの発振素子の間に接続され、それらの複数の遅延素子の間には特定の位相または時間遅延関係があり、該遅延素子により少なくとも該2つの発振素子の位相または周波数のノイズ抑制関連特性が結合されることで、回路システム動作中においてノイズの自己相関性が低下し、位相または周波数のノイズ抑制効果が増進し、スペースを取るような固体(solid state)サーキュレータ(circulator)またはアイソレーター(isolator)または共振器(resonator)の使用はなく、信号のひずみが低減され、システムの安定性が向上している。

(もっと読む)

ディジタル位相同期装置

【課題】入力された正弦波と周波数が等しく、かつ位相が同期した正弦波を、簡易で正確に、出力する装置を提供する。

【解決手段】位相差検出回路1は、外部から入力された第一の正弦波と正弦波生成回路5より出力する第二の正弦波との位相差を、ディジタル信号処理により算出する。その算出値に基づいて第二の正弦波の位相と周波数を調整するので、正弦波生成回路5は入力された第一の正弦波に周波数が等しく、かつ位相が同期した第二の正弦波を簡易に正確に出力することができる。

(もっと読む)

ADSLのTTRオフセット調整装置及びその方法

【課題】ADSL装置とTCM−ISDN装置とが整合されてサービスされるときに発生するNEXTまたはFEXTのノイズをTTRのオフセット調整を通じて除去することのできるADSLのTTRオフセット調整装置及びその方法を提供する。

【解決手段】TTRcに同期された第1及び第2クロックを相互に同期化し、前記同期化された第2クロックを一定の大きさの第3クロックに分周し、前記TTRcを前記分周された第3クロックを用いてハイクロック及びロウクロックに区分して各々カウントし、オフセット調整値の分だけ前記カウントされたハイクロック及びロウクロックを各々オフセット補正し、補正された第4クロック及び前記第1及び第2クロックを前記ADSL装置に提供するようにする。

(もっと読む)

クロック再生装置

【課題】本発明はクロック再生装置に関し、バーストモードに対応でき、また10Gbps以上の高速通信の場合にも安定に発振することができるクロック再生装置を提供することを目的としている。

【解決手段】入力データを受けて該入力データからパルスを作成するパルス作成回路20と、ゲート付きオッシレータ31と、該ゲート付きオッシレータ31の出力と基準クロックとを比較し、その比較結果により前記ゲート付きオッシレータ31に遅延時間を設定するための位相制御信号を与える周波数コントロール回路32から構成されるクロック再生回路30と、によりなり、前記パルス作成回路20の出力で前記ゲート付きオッシレータ31をリセットすると共に、当該ゲート付きオッシレータ31の出力をクロック再生出力とするように構成される。

(もっと読む)

適応的遅延調整を有する位相補間器

【課題】 参照信号と補間信号間の位相関係を確実に保持し、より小さく、より簡単な構成の装置を実現するために応用可能な位相補間器を提供する。

【解決手段】 位相補間器は、2つの可調整遅延器30及び31、可調整遅延器30で遅延された信号と可調整遅延器31で遅延された信号との位相差を検出する位相比較器32、位相比較器32の出力を積分する積分器33、可調整遅延器30及び31の制御電圧を設定する乗算器34−1、34−2を備える。位相比較器32と積分器33を備えるフィードバックループは、可調整遅延器30の遅延量を制御し、{ACK1、ACK2}及びICK間の位相関係を確実に保持し、安定なICK位相を実現する。

(もっと読む)

クロック同期方法およびクロック同期回路

【課題】 互いに非同期である送信側装置と受信側装置とのクロック同期をとるために、入力データ速度に対して数倍程度のクロック周波数があれば同期可能なクロック同期方法およびクロック同期回路を提供する。

【解決手段】 受信フレームが、クロックの同期のために利用される予め定められた信号を有する任意のビット数のクロック同期情報を備え、受信装置が、入力信号識別手段と、積分手段と、最適位相判定手段とを備え、受信装置が、受信フレームを受信したときに、入力信号識別手段が、前記受信フレームのクロック同期情報を識別し、積分手段が、前記入力信号識別手段の識別結果を位相毎に累積加算し、最適位相判定手段が、前記積分手段の累積加算結果を位相毎に比較することにより、クロック同期を得るために最適な位相を判定する。

(もっと読む)

外部クロック信号に同期する内部クロック信号を発生する方法および装置

【課題】外部クロック信号に同期した内部クロック信号を生成するクロック回路を提供すること。

【解決手段】位相ロックループ(PLL)からなる集積回路のためのクロック発生回路は、遅延した外部クロック信号の位相を内部クロック信号の位相と比較する位相検波器を含む。2つのクロック信号間の位相差分に一致するエラー信号が、差動増幅器に与えられる。エラー信号は位相検波器に結合される時、外部クロック信号の遅延に一致する値だけオフセットされる。オフセットエラー信号は、内部クロック信号を発生する電圧制御発振器の制御入力に与えられる。内部クロック信号の位相は、外部クロック信号の位相と実質的に同じになるように調整される。電圧制御発振器は、オフセットエラー信号が比較的狭い範囲の内部クロック信号の周波数を制御するだけで済むように複数の別個の周波数帯域内で動作するように構成される。

(もっと読む)

キャリア位相同期回路およびキャリア位相同期方法

【課題】 キャリア位相スリップの影響を低減する。

【解決手段】 キャリア位相変動成分を補償する1次ループと、初期位相推定回路と、1次ループの周波数引き込み終了後に、初期推定位相に第1の係数を乗じた値をループフィルタの初期値として設定し、位相検出回路の検出位相と第2の係数の乗算値をループフィルタで積分した結果を加算回路で加算して可変発振回路に入力する制御信号とする2次ループとを備えたキャリア位相同期回路において、初期位相推定回路は、位相検出回路の検出位相を所定の時間間隔で平均する移動平均回路と、移動平均回路から出力される移動平均位相を所定の抽出タイミングでサンプリングする抽出回路と、抽出回路で得られる異なる抽出タイミングにおける複数の移動平均位相サンプリング値を所定の制御タイミングで平均化し、初期推定位相として出力する選択制御手段とを備える。

(もっと読む)

遅延ロックループ回路、タイミング発生器、半導体試験装置、半導体集積回路及び遅延量校正方法

【課題】 遅延量の測定に代わる手法で、カウンタの初期設定値を決めて、遅延回路の校正にかかる時間を短縮可能とする。

【解決手段】 複数のカウンタ設定値の中から一つのカウンタ設定値がロードされ、遅延ロックループ回路10−1がロックモードに切り替えられ、サイクルスリップ検出回路20−1の順序回路22がリセットされ、その後、順序回路22から出力されるサイクルスリップ検出信号が読み込まれると、このサイクルスリップ検出信号にもとづき、遅延回路11の出力信号がサイクルスリップを起こしているか否かが判定され、起こしているときはカウンタ設定値が切り替えられ、一方起こしていないときは、ロックされて完了する。

(もっと読む)

PLL回路及びこれを用いた通信装置

【課題】入力信号に出力クロックが同期するまでの時間を短縮したPLL回路及びこれを用いた通信装置を実現する。

【解決手段】入力信号の位相に同期した新たな信号を生成するPLL回路に関し、特に同期化時間を短縮したPLL回路に関する。入力信号の周波数の2n(nは整数)倍のクロックを発生するクロック発生手段と、クロック発生手段から発生したクロックの周波数を1/nに分周して出力する第1の分周器と、第1の分周器の出力クロックの周波数を1/2に分周して出力する第2の分周器と、入力信号に同期したクリア信号を生成するクリア信号生成手段と、を有し、第2の分周器の出力クロックは、第1の分周器の出力クロックがクリア信号生成手段のクリア信号によりクリアされることで入力信号と同期する構成とした。

(もっと読む)

無線通信装置及び無線エントランスシステム

【課題】現用系装置と待機系装置との間での位相同期を効率よく行う無線通信装置及び無線エントランスシステムを提供する。

【解決手段】PLL回路14aは、インターフェース部100からの第1タイミング信号と読出カウンタ20aからの第2タイミング信号とが同相となるように、第2クロックを読出カウンタ20a、送信用無線フレーム処理部122a及びフレーム変調部124aに出力する。PLL回路14bは、前記第1タイミング信号と読出カウンタ20bからの第3タイミング信号とが同相となるように、第3クロックを読出カウンタ20b、送信用無線フレーム処理部122b及びフレーム変調部124bに出力する。

(もっと読む)

トリガ信号発生装置

【課題】入力信号に同期し、ジッタの少ないトリガ信号を生成するトリガ信号発生装置を実現することにある。

【解決手段】入力される入力信号よりも低い周波数のトリガ信号を出力するトリガ信号発生装置に改良を加えたものである。本装置は、入力信号を分周する分周回路と、この分周回路で分周された信号を入力信号に同期させる同期化手段を有する同期化回路とを設けたことを特徴とするものである。

(もっと読む)

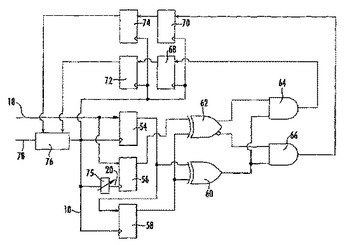

同期クロック信号を調整する方法および装置

もし同期クロック信号に対して半サイクル分遅らされたオフセットクロック信号のパルスの前にデータ信号の遷移が発生した場合には、同期クロック信号の遅延を減少させることによって同期クロック信号をデータ信号に対して調整することができる。もしオフセット同期クロック信号のパルスの後にデータ信号の遷移が発生した場合には、同期クロック信号を遅延させることができる。  (もっと読む)

(もっと読む)

伝送装置

【課題】SONETやSDH等の規格に基づき、現用予備の二重化構成を取る端局中継装置において、回線を増設するための回線のインターフェースを備えた装置を増設する際のクロック同期に関する発明である。

【解決手段】

増設した装置内において、現用/予備用装置から供給されるそれぞれのクロックを比較する。 比較結果に基づきそれぞれのクロックを可変遅延させ、増設した装置においても現用と予備回線に対してクロック位相制御を行えるようにする。

(もっと読む)

遅延固定ループ回路

【課題】遅延ラインを変更してDLLの出力クロックよりも速い位相を有するクロックを生成することで、DLLをPVT条件に合せて制御できる。

【解決手段】外部からクロックを受信して、複数のマルチクロックとマルチ位相信号とを出力するクロック遅延補償手段と、前記複数のマルチクロックと前記マルチ位相信号との位相を比較して、シフト動作を制御するための複数の位相制御信号を出力する位相制御部と、前記複数の位相制御信号の状態に応じてシフト動作を行って、前記クロック遅延補償手段を制御するマルチ位相遅延制御部とを備える。

(もっと読む)

ロックフェイル防止のための遅延固定ループクロックの生成方法及びその装置

【課題】相対的に長時間パワーダウンモードにとどまる場合、チップの温度等の様々な環境の変化によってロックフェイルが発生することを防止する遅延固定ループ装置を提供すること。

【解決手段】本発明の遅延固定ループ装置は、パワーダウンモードへの出入を決定する制御信号を生成するパワーダウンモード制御部と、制御信号によりノーマルモードで外部クロックをバッファリングし第1の内部クロック信号を生成する第1のクロックバッファと、制御信号によりパワーダウンモードで外部クロックをバッファリングし第2の内部クロック信号を生成する第2のクロックバッファと、制御信号によりノーマルモードでは第1の内部クロック信号を選択し、パワーダウンモードでは第2の内部クロック信号を選択して伝達するクロック選択部と、クロック選択部で選択された信号を使用して位相更新を行うことによりDLLクロックを出力する位相更新部とを備える。

(もっと読む)

121 - 140 / 171

[ Back to top ]