Fターム[5J106AA03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583)

Fターム[5J106AA03]の下位に属するFターム

PLL(位相同期ループ回路) (1,412)

Fターム[5J106AA03]に分類される特許

1 - 20 / 171

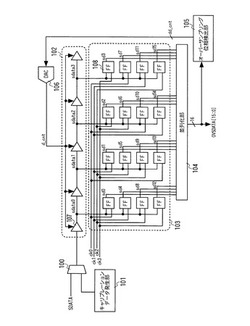

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

半導体装置、受信機、送信機、送受信機及び通信システム

【課題】周波数誤差に基づく送信クロックを生成し、送信データに対して任意にSSCの適用が選択可能な半導体装置が、望まれる。

【解決手段】半導体装置は、受信信号を入力し、動作クロック信号に基づいて受信信号からクロック信号とデータ信号を取り出すクロックアンドデータリカバリ部と、受信信号から取り出したクロック信号と動作クロック信号との周波数誤差信号を求める周波数誤差調整部と、周波数誤差信号を記憶する周波数誤差信号記憶部と、周波数誤差信号に基づいて動作クロック信号の周波数を制御する動作クロック生成部と、周波数誤差信号記憶部が記憶する周波数誤差信号の値に基づいて、動作クロック生成部が生成する動作クロック信号をスペクトラム拡散させて変動させるSSCG部と、を備えている。

(もっと読む)

同期ネットワークデバイス

【課題】物理層デバイスおよび同期デバイスの複数のポート間でクロックを同期させる方法を提供する。

【解決手段】制御方法は、グランドマスタークロックのソースとなるポートを選択するステップを含む(302)。選択されたポートは、リンク先からの送信に基づいてグランドマスタークロックを再生する。マルチポートPHY ICは、グランドマスターソースポートのRX_CLKを出力する(304)。グランドマスターソースポートのTX_CLKは、ローカルオシレータから取得される(306)。そして、ほかの全てのポートのTX_CLKは、クロック同期部の出力から取得される(308)。クロック同期部は、グランドマスターソースポートを有するマルチポートPHY ICからの再生クロックに基づいて同期させる(310)。

(もっと読む)

DLL回路、逓倍回路、及び半導体記憶装置

【課題】例えば、遅延クロックの位相と基準クロックの位相とを同期させるためのロック時間を低減する。

【解決手段】1つの実施形態によれば、ディレイチェーン、複数の位相比較器、制御部を有するDLL回路が提供される。ディレイチェーンでは、複数段の遅延素子が直列に接続されている。複数段の遅延素子は、基準クロックに対して互いに異なる遅延量のクロックを発生させる。複数の位相比較器は、基準クロックをそれぞれ受けるとともに、複数段の遅延素子における互いに異なる段の遅延素子からクロックを受ける。制御部は、複数の位相比較器による比較結果に基づいて、複数段の遅延素子のうち基準クロックに対して位相が同期するクロックを発生させる段数を決定する。制御部は、遅延クロックを出力するように、その決定された段数に基づいて複数段の遅延素子における出力段数を選択する。遅延クロックは、基準クロックが要求に応じた遅延量で遅延されたクロックである。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

クロック生成回路、及びクロック生成方法

【課題】一種類の多相クロックより多くの周波数の種類の単相クロックを得ることができるクロック生成回路及びその方法を提供する。

【解決手段】少なくともn個の位相補間器を有し、周波数がfで位相差が1/(f×m)づつ異なるm相クロックを、周波数がfで位相差が1/(f×n)づつ異なるn相クロックに変換するクロック変換回路1と、前記n相クロック信号の一部又は全部を用いて、周波数(f×n)/Aの単相クロック信号を生成する単相クロック生成回路2と、前記位相補間器に設定する内分比を制御する制御回路とを有し、前記各位相補間器は、前記m相の内の異なる二つのクロックを入力し、それらのタイミング差を、制御回路により設定した内分比で分割した遅延時間のクロックを生成して出力し、前記制御回路は、基準クロックと、回路の末端で分配されたクロックとのタイミングとが一致するように内分比を制御する。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

モータ速度制御装置、及び画像形成装置

【課題】安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供する。

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

(もっと読む)

誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

クロック生成装置及びクロック同期方法

【課題】冗長構成を有するとともにクロックの同期が確実に行えるクロック生成装置、及び、クロック同期方法を提供する。

【解決手段】クロック生成装置は、クロックC1、クロックC2をそれぞれ出力するVCXO14、24と、クロックC1又はクロックC2が供給されるとともに主たる機能に使用される主機能部31に設けられ、クロックC1及びクロックC2の位相を比較し、クロックC1及びクロックC2の位相ずれの情報を含む位相差情報を生成する位相比較器33と、この位相差情報に基づいてVCXO24に出力する制御電圧を調整し、クロックC1の位相にクロックC2の位相を同期させる第2制御部22と、を有する。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

デジタルクロックリカバリ回路及び半導体チップ

【課題】小型で、省電力で、かつパルスベースの超高速シリアル転送にも用いることのできるデジタルクロックリカバリ回路(CDR)を実現することを目的とする。

【解決手段】デジタルロックループ(DLL)、エッジ検出器、デジタルコンパレータ等を用いて、データ信号にDLLクロック信号をロックさせ、全ての回路要素をデジタル回路で構成し、クロックデータリカバリ(CDR)を実現する。

(もっと読む)

半導体装置

【課題】クロック生成回路からクロック信号を受けるドライブ回路の経年劣化を抑制する。

【解決手段】半導体装置1は、クロック信号INT1−SIGを生成して出力するクロック生成回路2と、クロック生成回路2からクロック信号INT1−SIGを受けるドライブ回路3とを備え、クロック生成回路2は、クロック信号INT1−SIGを生成して出力ノード2aから出力するクロック出力モードと、出力ノード2aの電位をハイレベルに固定する第1のクロック停止モードと、出力ノード2aの電位をロウレベルに固定する第2のクロック停止モードとを有する。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

位相制御装置

【課題】従来のこの種の装置では不可能な伝送路長の大きな変化による位相変動を調整できると同時に、検出精度を高める。

【解決手段】高周波信号である原信号を発生する原発振器1と、制御信号に基づいて原信号の通過時間を調整する移相器2と、原信号が伝送される伝送路3と、位相検出用信号を発生する位相検出用発振器4と、位相検出用信号の周波数を切り替える信号を発生する周波数切替信号発生器5と、位相検出用信号を2つに分岐して、基準信号と変調信号として出力する方向性結合器6と、方向性結合器6により分岐した変調信号が伝送される伝送路7,8と、方向性結合器6により分岐した基準信号と方向性結合器6により分岐して伝送路7,8を伝播した変調信号との位相を比較し、比較結果に応じて、原信号の通過時間を調整する制御信号を生成し移相器2に出力する位相検出器9とを備えた位相制御装置である。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

1 - 20 / 171

[ Back to top ]