Fターム[5J106BB00]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086)

Fターム[5J106BB00]の下位に属するFターム

Fターム[5J106BB00]に分類される特許

1 - 5 / 5

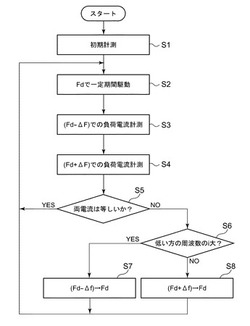

共振点追尾型駆動装置

【課題】 共振周波数を有する負荷の駆動中における該共振周波数の変動検知等を効率的にした共振点追尾型駆動装置を提供する。

【解決手段】 ステップS2及びS3において、共振周波数の変動検知動作開始前の駆動周波数(Fd)の位置より一定値の周波数だけ離れた2つの特定位置(周波数がFd+ΔFとFd−ΔFの位置)での負荷電流を計測し、それらをステップS5で比較して共振周波数の変動を検知し、その上で該変動に応じた追尾動作をするようにした。

(もっと読む)

タイミング調整装置

【課題】温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

ガスセル型原子発振器

【課題】 原子発振器の出力する安定な周波数の信号を使う場所が離れている場合に、その信号を長い同軸ケーブルで搬送していた。外部環境が同軸ケーブルに影響して発生する信号の周波数の揺らぎを削減する。

【解決手段】金属原子に対する励起光を出力する光源部1を設置する。その場所から離れて設置された原子共鳴部30には、該光源部1からの出射光を伝播させる光ファイバ33,34から出射される励起光と共鳴マイクロ波とを入力する。原子共鳴部30は、光マイクロ波二重共鳴を起し、その際に生じる共鳴周波数を出力する。

(もっと読む)

ロック検出装置及び光フェーズロックループシステム

【課題】光フェーズロックループ装置において、入力光信号とビート光信号とのロックを検出することである。

【解決手段】入力光信号及びビート光信号の第1の位相比較信号を出力する第1の位相検出器10と、第1の位相比較信号を整形するループフィルタ20と、整形した第1の位相比較信号に基づいてビート光信号を出力する光学電圧制御発振器(OVCO)30と、を備える光フェーズロックループ装置1と、ビート光信号の位相をシフトする位相シフト器としてのπ/2シフト器130Aと、入力光信号及び位相シフトされたビート光信号の第2の位相比較信号を出力する第2の位相検出器140と、を備え、π/2シフト器130Aは、ビート光信号に対して、第2の位相検出器140で比較される2つの光信号の位相が同期した場合に、その位相比較信号が0にならないπ/2を位相シフトする。

(もっと読む)

1 - 5 / 5

[ Back to top ]