Fターム[5J106CC00]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414)

Fターム[5J106CC00]の下位に属するFターム

発振回路、VCO (2,067)

位相比較(弁別)回路 (1,788)

周波数比較(弁別)回路 (250)

フィルタ回路 (1,598)

周波数変換回路 (1,116)

位相変換回路 (594)

Fターム[5J106CC00]に分類される特許

1 - 1 / 1

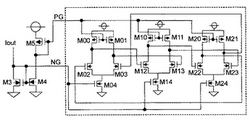

PLL回路

【課題】 PLL回路において製造ばらつきによらず広い周波数帯域且つ大幅なジッタ低減を簡単な構成で実現する。

【解決手段】 位相比較器と、ローパスフィルタと、電圧制御発振器とからなるPLL回路において、電圧制御発振器は、ローパスフィルタから出力される制御電圧を電流に変換する電圧電流変換回路と、該電流により発振周波数を制御されるリング状に接続された複数の差動インバータ回路より構成する発振回路とからなる。発振回路を構成するトランジスタのゲート長及びゲート幅を制御して位相雑音やジッタノイズを減少させる。

(もっと読む)

1 - 1 / 1

[ Back to top ]