Fターム[5J106CC03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | パルス・クロック発振回路 (169)

Fターム[5J106CC03]に分類される特許

1 - 20 / 169

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

分周回路およびPLL回路

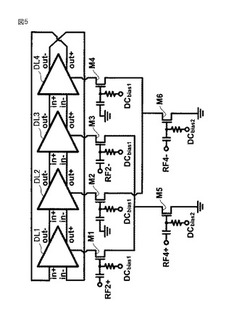

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

PLL回路

【課題】電圧制御発振回路の発振周波数レンジを広く保持しつつ、出力クロックのジッターを低減することが可能なPLL回路を提供する。

【解決手段】PLL回路は、基準クロックと出比較回路チャージポンプ回路を備え、チャージポンプ回路の出力に一端が接続された抵抗素子と、抵抗素子の他端に一端が接続され且つ接地に他端が接続された容量素子とを有し、チャージポンプ回路が出力した電流を変換して、抵抗素子の一端から第1の制御電圧信号を出力し且つ容量素子の一端から第2の制御電圧信号を出力する第1の低域通過フィルタを備える。PLL回路は、抵抗素子の一端に第1の非反転入力端子が接続され、容量素子の一端に第2の非反転入力端子が接続され、出力端子と反転入力端子とが接続され、出力端子から第3の制御電圧信号を出力するアンプ回路を備える。PLL回路は、第3の制御電圧信号に応じた周波数の出力クロックを出力するVCO回路とを備える。

(もっと読む)

周波数シンセサイザ

【課題】少数点逓倍の精度を向上させ、累積ジッタを低減した周波数シンセサイザを提供する。

【解決手段】位相比較器1と、チャージポンプ2と、ローパスフィルタ3と、電圧制御発振器4と、該電圧制御発振器の出力クロック信号を小数点分周して前記帰還クロック信号を生成する帰還回路とを備える。帰還回路は、電圧制御発振器4の出力クロック信号を分周する可変分周器5と、電圧制御発振器4の8相のクロック信号から1つの位相のクロック信号を選択するマルチプレクサ7と、マルチプレクサ7で選択した特定の位相のクロック信号により可変分周器5のクロック信号をリタイミングするリタイミング回路(DFF回路8,9とアンド回路10)とを備える。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

【課題】デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作を提供する。

【解決手段】DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積し、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

PLL回路、PLL回路の誤差補償方法及び通信装置

【課題】デジタル制御発振器を持つPLL回路に用いられるTDC回路の有限な分解能により発生する周期性誤差を補償することが可能なPLL回路を提供する。

【解決手段】発振回路の累積クロック数をデジタル値として検出する累積クロック数検出部と、前記発振回路の累積クロック数の小数部のデジタル値の、第1の基準クロックを基準とする周期性を検出する周期検出部と、前記発振回路の出力クロックの1周期のデジタル値、前記発振回路の累積クロック数の小数部が持つ周期性の1周期のデジタル値、および前記発振回路の累積クロック数の小数部が持つ周期性の各周期の開始点から前記第1の基準クロック数をカウントした値から補正値を算出する補正値算出部と、前記周期性の各周期の開始点から前記第1の基準クロックの周期で、前記累積クロック数の小数部に前記補正値を加算する加算部と、を備える、PLL回路が提供される。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

送信装置、受信装置及び伝送システム

【課題】簡易な構成によりクロックリカバリを実現し、伝送時のオーバーヘッドを削減する。

【解決手段】送信装置1−1は、制御用メタデータを生成し、制御用メタデータを定期的に受信装置2−1へ送信する。また、送信装置1−1は、コンポーネントの符号化を行い、自身のコンポーネントのクロックを用いてPCR、DTS及びCTSを生成し、または、他のコンポーネントのクロックを用いてDTS及びCTSを生成し、コンポーネントの符号データ等を受信装置2−1へ送信する。受信装置2−1は、制御用メタデータを定期的に受信すると共に、コンポーネントの符号データ等を受信する。そして、受信装置2−1は、制御用メタデータに従って、受信したPCRに基づいて自身のコンポーネントのクロックに対しクロックリカバリを行い、復号等を行う。また、受信装置2−1は、他のコンポーネントのクロックを流用して復号等を行う。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

クロック発生回路

【課題】 PLLを動作させた状態で、同期外れを起させず、入力クロックの切り替えおよびそれに伴う分周比の切り替えを行うことが可能なクロック発生回路を提供する。

【解決手段】 タイミング制御部8は、入力クロックを指定するクロック選択情報が切り替わった後、分周器1がリファレンスクロックCLKREFを出力するのに応じて、クロック選択指令SELCKを切り替える動作と、分周器1に1個のリファレンスクロックCLKREFを出力させるための入力クロックの個数Rと、分周器6に1個のフィードバッククロックCLKFBを出力させるための出力クロックCLKOの個数Fのうちの少なくとも一方の設定を切り替え、切り替え後の設定個数Rに対応した入力クロックの分周器1によるカウント動作および切り替え後の設定個数Fに対応した出力クロックの分周器6によるカウント動作の両方を開始させる。

(もっと読む)

1 - 20 / 169

[ Back to top ]