Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

101 - 120 / 1,193

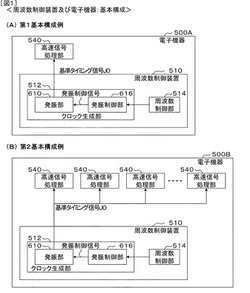

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

同期回路

【課題】基準信号に異常が発生した場合でも大きな位相ずれ量が発生しない同期信号(タイミング信号)を出力する同期回路を提供する。

【解決手段】同期回路1は、発振器クロック信号を発生する電圧制御発振器16と、第1の基準クロック信号及び第2の基準クロック信号を含む複数の基準クロック信号と前記発振器クロック信号との間のそれぞれの位相ずれ量を検出する位相ずれ量検出部12と、前記複数の基準クロック信号の状態に応じた制御信号に基づいて同期信号を出力する同期信号処理部13,14と、前記同期信号と前記発振器クロック信号との間の位相ずれ量に応じて電圧制御発振器16のコントロール電圧を生成するコントロール電圧生成部15とを備える。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

基準信号発生装置および基準信号発生方法

【課題】基準信号発生装置全体の消費電力を削減する。

【解決手段】OCXO120が、GPSモジュール110が同期信号を受信している間、当該同期信号を用いて基準信号を発生し、GPSモジュール110が同期信号を受信していない間は、あらかじめ設定された値を用いて基準信号を発生し、温度制御部130が、GPSモジュール110が同期信号を受信している間、OCXO120の温度を所定の温度よりもあらかじめ設定された温度だけ高い温度で変化させ、GPSモジュール110が同期信号を受信していない間は、OCXO120の温度をGPSモジュール110が同期信号を受信しなくなった際の温度に固定させる。

(もっと読む)

デルタシグマ変調型分数分周PLL周波数シンセサイザおよびそれを備えた無線通信装置

【課題】デルタシグマ変調型分数分周PLL周波数シンセサイザにおいて、スプリアスを抑制し、さらに、位相雑音特性を良好に保つ。

【解決手段】分周器(25)を変調することで分数分周を行うデルタシグマ変調型分数分周PLL周波数シンセサイザは、分数部データKに加算すべきシフト量Sを求め、シフト量Sと、シフト後分数部データK2とをそれぞれ出力する演算処理手段(27)と、シフト後分数部データK2を積分して量子化する第1のデルタシグマ変調器(28)と、シフト量Sを積分して量子化する第2のデルタシグマ変調器(29)と、第1のデルタシグマ変調器(28)の出力系列と第2のデルタシグマ変調器(29)の符号反転出力とを加算する第1の加算器(30)と、整数部データMと第1の加算器(30)の出力とを加算する第2の加算器(31)とを備え、第2の加算器(31)の出力により分周器(25)を変調させる。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、送信回路100と、受信回路170と、制御部110と、記憶部130とを含む。記憶部130は、送信回路用キャリブレーションパラメーターと受信回路用キャリブレーションパラメーターとの相関を表す情報を記憶する。制御部110は、送信回路100の送信状態の検出結果に基づいて送信回路用キャリブレーションパラメーターを設定し、設定された送信回路用キャリブレーションパラメーターと相関を表す情報とに基づいて受信回路用キャリブレーションパラメーターを設定する。送信回路100は、送信回路用キャリブレーションパラメーターに基づく送信処理を行う。受信回路170は、受信回路用キャリブレーションパラメーターに基づく受信処理を行う。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

デジタルクロックリカバリ回路及び半導体チップ

【課題】小型で、省電力で、かつパルスベースの超高速シリアル転送にも用いることのできるデジタルクロックリカバリ回路(CDR)を実現することを目的とする。

【解決手段】デジタルロックループ(DLL)、エッジ検出器、デジタルコンパレータ等を用いて、データ信号にDLLクロック信号をロックさせ、全ての回路要素をデジタル回路で構成し、クロックデータリカバリ(CDR)を実現する。

(もっと読む)

同期信号生成装置および同期信号生成方法

【課題】ホールドオーバー状態からGPSロック状態に復帰する際の基地局の状態に応じて、内部パルスおよび内部周波数信号をGPS基準パルスに同期させた状態に復帰させることができる同期信号生成装置および同期信号生成方法を提供することである。

【解決手段】本発明に係る基地局3にパルスを提供する同期信号生成装置は、GPS衛星から受信した信号からGPS基準パルスを生成するGPS受信器11と、内部周波数信号を生成する発振器15と、内部周波数信号を分周して内部パルスを生成する分周器12と、GPS基準パルスと内部パルスとを比較して前記内部パルスを前記GPS基準パルスに同期させる同期部14と、基地局3の状態に応じて、ホールドオーバー状態からGPSロック状態に復帰するときの、同期部14のループタイムを決定する制御部13と、を備える。

(もっと読む)

PLL回路

【課題】平均値計算器に演算能力が比較的低い計算器を用いることが可能な技術を提供することを目的とする。

【解決手段】PLL回路は、基準クロック信号frと比較クロック信号fpとの位相比較を基準クロック信号frの周期毎に実行し、高電圧レベルの第1パルス及び低電圧レベルの第2パルスを含む信号を、前記第1及び第2パルスの当該周期単位でのパルス幅の差が当該位相比較での位相差に対応するように生成する位相比較器2と、位相比較器2が生成した信号の電圧を基準クロック信号frの周期毎に平均化する平均値計算器3とを備える。そして、平均値計算器3からの出力を基準クロック信号frの1周期分よりも長く遅延させるm周期遅延器5を備える。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

半導体装置

【課題】クロック生成回路からクロック信号を受けるドライブ回路の経年劣化を抑制する。

【解決手段】半導体装置1は、クロック信号INT1−SIGを生成して出力するクロック生成回路2と、クロック生成回路2からクロック信号INT1−SIGを受けるドライブ回路3とを備え、クロック生成回路2は、クロック信号INT1−SIGを生成して出力ノード2aから出力するクロック出力モードと、出力ノード2aの電位をハイレベルに固定する第1のクロック停止モードと、出力ノード2aの電位をロウレベルに固定する第2のクロック停止モードとを有する。

(もっと読む)

PLL回路

【課題】PLL回路のロック状態での定常位相誤差を抑制する。

【解決手段】PLL回路は,レファレンスクロックとフィードバッククロックの位相を比較し,当該位相の差を示す位相比較信号を出力する位相比較器と,位相比較信号が示す位相の差に応じた期間,第1のチャージポンプ電流と第2のチャージポンプ電流とを出力するチャージポンプ回路と,第1及び第2のチャージポンプ電流に基づく電荷を蓄積するキャパシタを有し,蓄積電荷による制御電圧を生成するループフィルタと,制御電圧に応じた周波数の出力クロックを生成する発振器と,出力クロックを分周して前記フィードバッククロックを出力する分周器とを有し,さらに,ロック状態のときに,位相比較信号が示す位相の差に応じて,当該位相の差が抑制されるように,第1または第2のチャージポンプ電流の電流値を調整するチャージポンプ調整回路とを有する。

(もっと読む)

送受信装置

【課題】構造簡単な距離を測定可能とした送受信装置の実現

【解決手段】第1信号の受信と第2信号の送信とを共通化した送受信アンテナ20と、第1信号を復調して第1パルス信号を得る復調器30と、制御信号を入力して目標周波数を設定する目標周波数設定レジスタ61と目標位相を設定する目標位相設定レジスタ66とを有し、目標周波数設定レジスタに設定されている目標周波数と目標位相設定レジスタに設定されている目標位相とに一致した周波数と位相の第2パルス信号を出力するパルス発振器60を有する。第2パルス信号により搬送波を変調する変調器70と、第1パルス信号と、第2パルス信号との位相差を検出する位相比較器32を有する。また、位相差信号の時間変動からその時の第1パルス信号と第2パルス信号との周波数差をもとめ、その周波数差に基づいて目標周波数を制御する周波数制御装置と、位相差信号の示す位相差に基づいて目標位相を制御する位相制御装置とを有する。

(もっと読む)

小数点分周PLL回路および集積回路

【課題】ループフィルタのカットオフ周波数を低く設定することなく、スプリアスを抑制する。

【解決手段】基準発振器で生成された基準周波数を所定の基準クロックに分周する第1の分周器103と、電圧制御発振器で生成された発振周波数を所定の帰還クロックに小数点分周する第2の分周器105と、基準クロックと帰還クロックとの位相を比較する位相比較器106と、位相比較器106による比較結果に基づいて電圧制御発振器の発振周波数を制御するチャージポンプ107と、を備えた小数点分周PLL回路1において、第1の分周器103側の電源パッド1−2と、第2の分周器105側の電源パッド1−1と、位相比較器106側の電源パッド1−3と、チャージポンプ107側の電源パッド1−4とを、それぞれ別個に備える。

(もっと読む)

101 - 120 / 1,193

[ Back to top ]