Fターム[5J106CC21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788)

Fターム[5J106CC21]の下位に属するFターム

Fターム[5J106CC21]に分類される特許

161 - 180 / 1,193

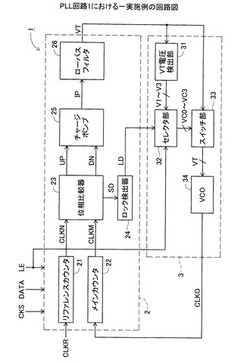

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

デジタル位相差検出器およびそれを備えた周波数シンセサイザ

【課題】高精度で回路面積および消費電力が小さいデジタル位相差検出器を提供する。

【解決手段】デジタル位相差検出器は、第1の信号を累積的に遅延させて各遅延量の信号を生成する遅延回路(10)と、第2の信号に同期して各遅延量の信号をラッチするフリップフロップ群(20)と、フリップフロップ群の出力から、第1の信号の立ち上がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第1の位相差、および第1の信号の立ち下がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第2の位相差を検出するエッジ検出器(30)と、第1および第2の位相差を記憶する記憶回路(40)と、記憶回路が記憶している過去の第1および第2の位相差の差分およびエッジ検出器が新たに検出した第1および第2の位相差の差分から第1の信号の周期を算出し、当該周期を基準にして第1および第2の信号の位相差を正規化する正規化回路(50)とを備えている。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

位相制御装置

【課題】従来のこの種の装置では不可能な伝送路長の大きな変化による位相変動を調整できると同時に、検出精度を高める。

【解決手段】高周波信号である原信号を発生する原発振器1と、制御信号に基づいて原信号の通過時間を調整する移相器2と、原信号が伝送される伝送路3と、位相検出用信号を発生する位相検出用発振器4と、位相検出用信号の周波数を切り替える信号を発生する周波数切替信号発生器5と、位相検出用信号を2つに分岐して、基準信号と変調信号として出力する方向性結合器6と、方向性結合器6により分岐した変調信号が伝送される伝送路7,8と、方向性結合器6により分岐した基準信号と方向性結合器6により分岐して伝送路7,8を伝播した変調信号との位相を比較し、比較結果に応じて、原信号の通過時間を調整する制御信号を生成し移相器2に出力する位相検出器9とを備えた位相制御装置である。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

位相固定ループ及びその動作方法

【課題】位相固定ループのロッキングタイムを減らすことができる、特にターゲット値(出力クロックの目標周波数)が変化しても常に短いロッキングタイムを有する位相固定ループ及びその動作方法を提供する。

【解決手段】位相固定ループは、入力クロックCLK_INの位相とフィードバッククロックCLK_FBの位相とを比較する位相比較部310と、位相比較部310の比較結果UP,DNに応じて周波数制御信号DCO_CONTROL_SIGNALSを生成する制御部330と、周波数制御信号DCO_CONTROL_SIGNALSに応答して出力クロックCLK_OUTを生成するオシレータ部340と、入力クロックCLK_INの周波数を検出して、検出結果に応じて初期値INIT_VALUEを制御部330に提供する初期値提供部350とを備える。

(もっと読む)

無線通信のエミッション抑制のための送信元、方法及び位相同期回路

【課題】送信機の出力スペクトルをフィルタリングするための効率的な方法及びシステムを提供する。

【解決手段】本明細書に開示する方法は、位相同期回路の出力を位相同期回路の入力で受け取った信号と同期させることを備える。方法は、更に、位相同期回路の第1利得及び第1抵抗の内の少なくとも1つを、潜在的に問題のあるチャネルにおける通信に適用することによって、潜在的に問題のあるチャネルにおけるエミッションを抑制することを備え、第1利得及び第1抵抗の内の少なくとも1つは、潜在的に問題のあるチャネル以外のチャネルにおける通信に適用される第2利得及び第2抵抗とは異なっている。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

PLL回路

【課題】ロックアップタイムの高速化とリファレンスリークの低減化をとバランス良く達成する。

【解決手段】電圧制御発振器(104)の制御電圧VCONTをアナログ/デジタル変換して得られるデジタル信号(ADCO)を出力するアナログ/デジタル変換回路(106)と、基準クロック信号(FREF)と帰還クロック信号(FDIV)とがロックしたことを検出した時にロック検出信号(S201)を出力するロック検出部(201)と、ロック検出部からロック検出信号が入力された時にアナログ/デジタル変換回路から入力されたロック時デジタル信号を保持する保持部(107)と、保持部に保持されたロック時デジタル信号とアナログ/デジタル変換回路から出力されたデジタル信号との比較結果に基づいてチャージポンプ電流の電流量を段階的に減少させるチャージポンプ電流量制御信号(CPCONT)を生成するチャージポンプ制御部(108)と、を備えるPLL回路。

(もっと読む)

回路、制御システム、制御方法及びプログラム

【課題】ジッタ・ワンダ抑圧性能を満足しつつ、高速な周波数追従性能を実現することが可能な回路を提供する。

【解決手段】本実施形態の回路は、OTN(Optical Transport Network)信号からSDH(Synchronous Digital Hierarchy)信号及びEthernet信号のクロックを再生するPLL部100の位相比較データを基に、ジッタ・ワンダ成分及び周波数急変状態を検出、解析し、その結果を基に、PLL部100のループゲインを制御することを特徴とする。

(もっと読む)

PLL回路、DLL回路

【課題】基準クロック信号と比較対象となるクロック信号の両者の位相を比較する位相比較器から位相差信号が出力され続けるPLL回路又はDLL回路にあって、両信号の同期を適切に検出して低ジッタ動作を実現する。

【解決手段】同期判定回路(15)は、基準クロック信号(R)の位相を基準として帰還クロック信号(V)の位相が進相又は遅相であるかを検出し、両信号の位相差の期間、進相検出信号(DOWN)又は遅相検出信号(UP)を出力する進相及び遅相検出部(158)と、進相検出信号(DOWN)が出力されている期間、初期値からの計数を開始する進相期間計数部(155)と、遅相検出信号UPが出力されている期間、初期値からの計数を開始する遅相期間計数部(156)と、進相期間計数部又は遅相期間計数部の計数値が第1の規定値に到達しない回数が第2の規定値を上回ったとき、位相同期検出信号(P_DET)を出力する位相同期判定部(157)と、を備える。

(もっと読む)

アクチュエータの駆動装置ならびにそれを用いる平行移動機構、干渉計および分光器

【課題】被駆動部材となる可動部とそれを駆動する駆動部とを備えて成るアクチュエータをPLL回路で駆動し、機械共振駆動を行わせる駆動装置において、短時間でかつ確実な位相引き込み動作を可能にし、さらに回路規模の増大やコストアップを抑える。

【解決手段】PLL回路のループフィルタ部14aを、位相比較器13の位相比較信号Vpdを平滑化してVCO11へ制御電圧Vcとして与えるLPFとしての機能を実現する積分回路21に、基準電圧源22とリセット手段としての短絡スイッチ23とを設ける。したがって、前記制御電圧Vcは、積分動作に伴い、基準電圧Vrefから共振周波数の目標電圧付近に滑らかに移行するので、オーバーシュートやリンギングの発生がなく、短時間でかつ確実な位相引き込み動作(位相ロックイン)を行うことができる。また、PLLループの外部に、制御信号を掃引するための特別な構成を設ける必要もない。

(もっと読む)

半導体装置

【課題】ジッタが小さいクロック信号を選択して使用することができる半導体装置を提供する。

【解決手段】本実施の形態の半導体装置100は、外部からクロック信号が入力されるクロック入力端子MCKと、クロック入力端子MCKを介して入力されたクロック信号を波形整形するクロックバッファ回路34と、クロックバッファ回路34の出力に基づいてクロック信号よりも周波数の高い第1の内部クロック信号ICKPFを発生するためのPLL回路36と、第1の内部クロック信号ICKPFを分周してクロック信号の周波数に戻した第2の内部クロック信号ICKPとクロックバッファ回路の出力ICKSとを受けて、受けた複数の信号の中から選択した選択クロック信号を出力するセレクタ40とを備える。

(もっと読む)

原子発振器

【課題】PLL回路の回路構成を単純化することが可能となり、調整箇所の削減と低消費

電力化を実現した原子発振器を提供する。

【解決手段】この原子発振器40のPLL回路4は、VCXO2の出力周波数を1/Rに

分周する1/R分周器5と、VCXO2に同期したマイクロ波周波数を生成する電圧制御

発振器6と、VCO6から出力されるマイクロ波周波数を分周する1/Mプリスケーラ7

と、1/Mプリスケーラ7の出力周波数をK/Lに分周するK/L分周器8と、1/R分

周器5の出力とK/L分周器8の出力との位相差を出力する位相比較器9と、位相比較器

9の出力に基づいて直流分を取り出すLPF10と、を備えて構成されている。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

クロック位相同期回路

【課題】従属同期網に於けるクロック位相同期回路に関し、誤接続によるクロックループ接続状態の有無を判定する。

【解決手段】基準となる上位局からのリファレンス入力と電圧制御発振器1の出力信号又は分周器4により分周した信号との位相差を位相比較器3により求め、その位相差に対応した制御値を算出し、制御値に従った制御電圧を電圧制御発振器1に入力し、リファレンス入力に位相同期したクロックを出力するクロック位相同期回路であって、位相比較器3により求めた位相比較出力信号を基に、電圧制御発振器1の制御値を求める制御値演算部2と、この制御値演算部2により求めた制御値に所定の変動量を所定時間だけ加算して、制御値の変動経過を監視する監視制御部6とを備え、制御値算出部7により求めた制御値に、所定の変動量を所定時間加算したことによる制御値の変化を基に正常な従属同期網を構成しているか否かを判定する構成を備えている。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

周波数制御回路及び出力周波数制御方法

【課題】接地電位が変動した場合においても、通信品質の劣化が生じない周波数制御回路及び出力周波数制御方法を提供すること

【解決手段】本発明にかかる周波数制御回路は、入力電圧に応じて出力周波数を変化させる電圧制御発振器10と、電圧制御発振器10から出力される出力周波数と基準周波数との位相差を検出し、当該位相差に応じて出力電圧を変化させる位相検出器11と、電圧制御発振器10における接地電位と位相検出器11における基準接地電位との間に発生する抵抗によって生じる電位差を、出力電圧に加算して電圧制御発振器10へ出力する加算器12と、を備えるものである。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

161 - 180 / 1,193

[ Back to top ]