Fターム[5J106CC23]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | マルチプライヤ型 (7)

Fターム[5J106CC23]に分類される特許

1 - 7 / 7

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

無線受信機及び電子機器

【課題】低消費電力の振幅変調無線受信機を提供すること。

【解決手段】無線受信機は、無線周波数入力信号および利得制御信号を受信し、増幅信号

を提供する増幅器と、高閾値コンパレーターの出力を受信し利得制御信号を提供する自動

利得制御回路と、増幅信号および局部振動信号を組み合わせて混合出力を提供するミキサ

ーと、混合出力を基準レベルと比較し高閾値コンパレーターの出力を提供する高閾値コン

パレーターと、混合出力を基準レベルと比較し無線受信機の出力を提供する低閾値コンパ

レーターとを含む。

(もっと読む)

PLL回路

【課題】差動入力型VCO回路の利点である同相ノイズに強く、さらに入力電圧範囲がシングル入力より広いPLL回路を提供する。

【解決手段】差動入力型VCO回路とループフィルタ回路と位相検出回路とを備え、半導体集積回路に設けられるPLL回路であって、差動入力型VCO回路に位相検出した信号を供給する位相検出回路と、位相検出回路の出力と差動入力型VCO回路の一方の差動入力を接続し、位相検出回路の出力とグランド間に設けたループフィルタ回路と、差動入力型VCO回路の他方の差動入力に位相検出回路と略同じバイアス電圧を供給するダミー出力用バイアス回路と、を具備する半導体集積回路に設けられるPLL回路である。

(もっと読む)

PLL回路およびそれを用いた光ディスク装置

【課題】 PLL回路において位相誤差信号の線形性を改善して位相スリップを防止する。

【解決手段】 位相誤差信号を生成する位相誤差生成手段(2〜8)と、位相誤差信号の2次高調波を生成する2次高調波生成手段(13〜17)と、位相誤差信号と2次高調波生成手段の出力とを加算する加算手段(18)とを備え、加算手段の出力を新たな位相誤差信号とすることを特徴とする。

(もっと読む)

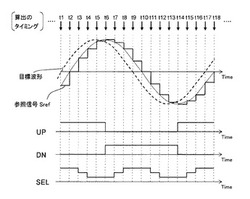

位相周波数検出回路およびPLL

【課題】 媒体の傷等の影響を受けず、変調マークに左右されずに安定に高速にPLLを引き込むことが可能な位相周波数検出回路およびPLLを提供することにある。

【解決手段】 再生信号に基づいて再生クロック信号を生成する回路において、前記再生クロック信号を生成する電圧制御発振器と、前記再生クロックから前記所定周期の信号を発生する第1の周期発生器と前記第1の周期発生器とは位相が異なり、前記再生クロックから前記所定周期の信号を発生する第2の周期発生器と、前記再生信号と前記第1の周期発生器の出力とを乗算する第1の乗算器と、前記再生信号と前記第2の周期発生器の出力とを乗算する第2の乗算器と、前記第1の乗算器の出力と第2の乗算器の出力に応じて前記電圧制御発振器の制御電圧を制御するPLL。

(もっと読む)

PLL回路およびそれを用いた無線通信端末機器

【課題】PLL帯域を広げることなくセットリング時間を短縮し、かつ、IC化に適したPLL回路を提供する。

【解決手段】PLL回路の位相比較器1を電流出力型とし、セットリング時間を短縮するために、電流出力型位相比較器1の出力端に定電流源2を接続する。また、PLLのリセット用スイッチ3を電流出力型位相比較器1の出力端に接続する。セットリング時間を短縮するために、PLL帯域を広げる必要がなく、雑音を低減できる。また、リセット用スイッチおよびセットリング時間短縮用の定電流源のIC化が可能となる。

(もっと読む)

信号発生装置及び信号発生方法

【課題】遅延要素を有する信号発生装置において、遅延要素の遅延量変化に関わらず安定した信号発生を可能にする。

【解決手段】信号発生装置100の共振器1では、BPF6の出力信号が遅延要素3に入力されると、その入力された信号に遅延が与えられる。遅延要素3の出力信号は、IQ変調器16により位相が制御される。位相制御された信号は増幅器5にフィードバックされる。外部同期装置2では、ミキサ8により、BPF6の出力信号と基準信号の位相差が検出され、位相差を示す信号がループフィルタ9を介して複素VCO10に入力される。複素VCO10では、この位相差に基づいてIQ変調器16への制御信号が生成され、IQ変調器16では、複素VCO10から印加された制御信号に従って、遅延要素3により遅延された信号の位相が制御される。

(もっと読む)

1 - 7 / 7

[ Back to top ]