Fターム[5J106CC24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | アップダウン型 (271)

Fターム[5J106CC24]に分類される特許

1 - 20 / 271

高安定発振器

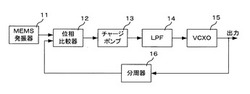

【課題】小型化が容易であり、低コストで製造可能であって、発振出力周波数における短期安定度と長期安定度とを両立させた高安定発振器を提供する。

【解決手段】一定の周波数の信号を出力する高安定発振器は、出力発振器として電圧制御型水晶発振器15を備えるPLL回路と、MEMS振動子を有するMEMS発振器11と、を備える。MEMS発振器11の出力を基準信号としてPLL回路の位相比較器12に供給する。MEMS発振器11によって出力周波数の長期安定度が維持され、電圧制御型水晶発振器15によって出力周波数の短期安定度が維持されるようにする。

(もっと読む)

発振器

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

PLL回路

【課題】電圧制御発振回路の発振周波数レンジを広く保持しつつ、出力クロックのジッターを低減することが可能なPLL回路を提供する。

【解決手段】PLL回路は、基準クロックと出比較回路チャージポンプ回路を備え、チャージポンプ回路の出力に一端が接続された抵抗素子と、抵抗素子の他端に一端が接続され且つ接地に他端が接続された容量素子とを有し、チャージポンプ回路が出力した電流を変換して、抵抗素子の一端から第1の制御電圧信号を出力し且つ容量素子の一端から第2の制御電圧信号を出力する第1の低域通過フィルタを備える。PLL回路は、抵抗素子の一端に第1の非反転入力端子が接続され、容量素子の一端に第2の非反転入力端子が接続され、出力端子と反転入力端子とが接続され、出力端子から第3の制御電圧信号を出力するアンプ回路を備える。PLL回路は、第3の制御電圧信号に応じた周波数の出力クロックを出力するVCO回路とを備える。

(もっと読む)

位相ロック・ループにおけるVCOの動的バイアス印加

【課題】無線通信機器における局部発振器を提供する。

【解決手段】局部発振器が位相ロック・ループを含む。位相ロック・ループは電圧制御発振器23と新規のVCO制御回路27を含む。VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、VCO制御回路は、PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次にPLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程はPLLがロックされたままで行われる。

(もっと読む)

位相同期回路及びテレビジョン信号受信回路

【課題】チューニングラインに設けられるラインフィルタのフィルタ特性の低下を防止すること。

【解決手段】この位相同期回路は、チャージポンプ(35)から出力されるパルス信号を積分するローパスフィルタ(19)と、ローパスフィルタ(19)から電圧制御発振回路(17A)に対して制御電圧を供給する制御電圧供給ライン(LUHF)に設けられたラインフィルタ(20)と、を具備し、ラインフィルタ(20)のキャパシタ(C1)の一端をチャージポンプ(35)の出力端子からCP電流切替回路(36)の抵抗(r)を介してグランドに高周波的に接続した。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

PLL回路

【課題】サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ループフィルタをオンチップ化する際、トランジスタの素子サイズのバラツキによるPLL回路の特性バラツキを軽減して、回路規模と消費電力の増大を軽減する。

【解決手段】半導体集積回路は、位相周波数比較器1とループアッテネータ2とチャージポンプ3とループフィルタ4と電圧制御発振器5と分周器6を具備するフェーズロックドループ回路を内蔵する。アッテネータ2は、サンプリング回路21とカウンタ22とを含む。回路21にサンプリングパルスSPL_CLKと位相周波数比較器1から出力される第1と第2の出力信号が供給され、回路21はサンプリング出力信号を出力する。カウンタ22は回路21から出力される所定個数のサンプリングパルスのカウントアップを完了すると、カウントアップ完了出力信号を出力する。チャージポンプ3は、カウントアップ完了出力信号に応答してループフィルタ4に充電電流または放電電流を出力する。

(もっと読む)

発振装置

【課題】水晶振動子の動作時間の経過に伴う発振周波数の変化を補償して安定した発振周波数が得られる発振装置を提供すること。

【解決手段】基準時から所定の時間が経過した後における第1及び第2の水晶振動子の周波数差と、基準時における第1及び第2の水晶振動子の周波数差と、の差分値ΔF(即ち、第1の水晶振動子における周波数について基準時からの変化分と、第2の水晶振動子における周波数について基準時からの変化分との差分値ΔF)を求める。そして基準時からの時間の経過に対して、第1の水晶振動子の周波数の変化分と第2の水晶振動子の周波数の変化分との比率が同じであるとして取り扱ったときの当該比率を経時変化の補正係数とし、差分値ΔFに対応する値と経時変化の補正係数とに基づいて、発振装置の出力を作り出すための水晶振動子の周波数について補正値を取得する。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

PLL回路および半導体装置

【課題】 PLL回路の発振精度の低下を抑制しつつ、ロックアップタイムを短縮する。

【解決手段】 PLL回路は、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号を分周する分周器と、基準信号と分周された出力信号との位相差を検出し、位相差に応じて第1検出信号および第2検出信号を生成する位相比較器と、第1検出信号に基づいてオン/オフが制御される第1スイッチおよび第2検出信号に基づいてオン/オフが制御される第2スイッチを含み、制御電圧を調整するチャージポンプ回路と、チャージポンプ回路により充放電される容量素子を含み、チャージポンプ回路の出力を平滑化して制御電圧を生成するローパスフィルタと、電圧制御発振器に初期電圧を与える初期設定期間に、第1スイッチおよび第2スイッチの少なくとも一方をオンし、容量素子の充放電を制御することにより、制御電圧を初期電圧に設定する電圧供給部とを有している。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

位相周波数比較回路及びPLL回路

【課題】入力クロックが停止しても出力クロックの周波数を保持するPLLを用いて、ロジック回路を駆動する方法を提供する。

【解決手段】位相周波数比較回路をPFD主要部と基準クロック停止検出部202Bの二つのモジュールから構成する。基準クロック停止検出部202BはPFD主要部のRS−FFのデータ端子に基準データ信号pfd_in_enを出力する。この基準データ信号pfd_in_enは、基準クロック停止検出部202B内のフリップフロップ202B−1に由来して生成される。このフリップフロップ202B−1は位相比較動作の終了を表すオーバラップ信号overlapをタイミングとし、基準クロックref_clkによってリセットされる。基準クロックref_clkが停止すると、基準データ信号pfd_in_enは「L」のままとなり、結果PFD主要部の動作が停止する。

(もっと読む)

フェーズロックドループの方法及び装置

【課題】2点変調を採用するフェーズロックドループを用いた通信システムを提供する。

【解決手段】フェーズロックドループは、位相検出器106の第1の入力に動作可能に接続された出力を有する主発振器100、位相検出器106の第2の入力に動作可能に接続された出力を有する従発振器102、及び位相検出器106の生誤り端末に動作可能に接続されたフォワード利得適応モジュールを含む。フォワード利得適応モジュールは、位相検出器106の生誤り端末と動作可能に接続された、フォワード利得適応モジュールの可変利得増幅器200と、前記フォワード利得適応モジュールの可変利得増幅器200と前記従発振器102とに動作可能に接続された、フォワード利得適応モジュールの積分器202とを具備する。

(もっと読む)

位相ロックループ回路

【課題】簡素な回路構成で、電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路1と、検出された位相差に応じた電流を容量に出力するチャージポンプ回路2と、容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路4とを有する位相ロックループ回路にて、制御電圧がロック状態時の電圧であった場合に電圧制御発振回路4の入力部に流れるリーク電流に等しい電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

1 - 20 / 271

[ Back to top ]