Fターム[5J106CC31]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250)

Fターム[5J106CC31]の下位に属するFターム

周波数電圧変換型 (9)

周波数数値変換型 (8)

基準信号と比較 (33)

複数の周波数比較(弁別)回路 (13)

Fターム[5J106CC31]に分類される特許

1 - 20 / 187

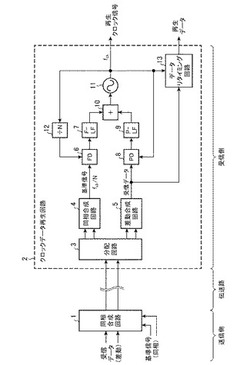

信号伝送システム、信号送信装置およびクロックデータ再生回路

【課題】良好な通信品質で、高速な位相同期ループを得る。

【解決手段】送信側は、一方が差動信号であり他方が同相信号であるデータ信号および基準信号を同相合成し、一対の伝送路を通じて伝送する同相合成回路1を備え、クロックデータ再生回路2は、同相合成回路1からの信号からデータ信号および基準信号を分離する信号分離手段(分配回路3、同相合成回路4および差動合成回路5)と、データ信号と位相が同期した再生クロック信号を生成する再生クロック信号生成手段(位相比較回路8、位相同期ループ用ループフィルタ9および電圧制御発振器11)と、再生クロック信号を分周し、当該分周した信号の周波数を基準信号の周波数に同期させる制御信号を生成し、当該制御信号により再生クロック信号の周波数を制御する再生クロック信号収束手段(周波数比較回路6、周波数同期ループ用ループフィルタ7、電圧制御発振器11およびN分周回路12)とを備えた。

(もっと読む)

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

原子発振器

【課題】磁気量子数mF=0におけるEIT信号のピーク値を高くした原子発振器を提供する。

【解決手段】本発明の原子発振器100は、アルカリ金属原子に電磁誘起透過現象を発現させるための第1の共鳴光、及び第2の共鳴光を発生する半導体レーザー(光源)1と、半導体レーザー1から発生した共鳴光1aを円偏光するλ/4波長板2と、アルカリ金属原子が封入された原子セル3と、原子セル3から出射した共鳴光3aの強度を検出する光検出手段5と、アルカリ金属原子に所定の強度の直流磁場を与える直流磁場発生手段4と、直流磁場の強度に応じた所定の周波数の交流磁場をアルカリ金属原子に与える交流磁場発生手段8と、光検出手段5から出力された共鳴光の中心波長を制御する中心波長制御手段9と、アルカリ金属原子にEIT現象を発現させるように、第1の共鳴光と第2の共鳴光との周波数差を制御する制御手段10と、を備えて構成されている。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

無線機

【課題】煩雑なメンテナンスを行わなくても周波数精度を高く保つことができ、かつ変調信号による周波数偏移を大きくすることができる無線機を提供する。

【解決手段】基準信号を出力する電圧制御水晶発振器と、高周波信号を出力する電圧制御発振器と、基準信号と高周波信号とが入力され、高周波信号の位相が基準信号と同じになるように位相同期を行う位相同期回路と、参照信号を発生する参照信号発生部と、基準信号の周波数を補正する周波数補正信号を電圧制御水晶発振器に出力するとともに、基準信号と参照信号とに基づき、基準信号の周波数が参照信号の周波数に対して所定の範囲内となるように周波数補正信号の値を変更する制御部と、から無線機を構成する。

(もっと読む)

PLL回路およびそのキャリブレーション方法

【課題】1回のキャリブレーションによって電圧制御発振器のフリーラン発振周波数がPLLロックレンジ内に入るようにして、キャリブレーション時間の大幅な時間短縮が可能となり、低消費電流化に貢献できるようにする。

【解決手段】PLLループをオープンにし、電圧制御発振器1に制御電圧Vcとして基準電圧Vaを入力したとき、基準信号f3のパルスによって帰還信号f2のパルス幅をカウントし、得られたカウント値に基づき、電圧制御発振器1の発振周波数f1を調整するキャリブレーションを実行するキャリブレーション回路10を設ける。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

信号生成回路、レーダー装置

【課題】低雑音で高周波数精度かつ高線形なFMCW信号を得ることのできる信号生成回路、レーダー装置を提供する。

【解決手段】アナログ制御信号により発振信号の周波数が制御される発振器を有している信号生成回路は、発振信号の位相情報を検出してディジタルの位相情報を出力するディジタル位相検出部と、ディジタルの位相情報を微分してディジタルの周波数情報を出力する第1の微分部と、発振周波数を設定する周波数設定コードとディジタルの周波数情報とを比較してディジタルの周波数誤差情報を出力する比較部と、ディジタルの周波数誤差情報の高周波成分を除去するローパスフィルタ部とを備えている。さらに、高周波成分が除去されたディジタルの周波数誤差情報をアナログの周波数誤差情報に変換するD/A変換部と、アナログの周波数誤差情報を積分してアナログの位相誤差情報に変換しアナログ制御信号として出力する積分器とを備えている。

(もっと読む)

改良された帯域幅を備える電圧制御発振器を有する位相同期ループ回路

【課題】改良された電圧制御発振器を提供する。

【解決手段】電圧制御発振器(16)は複数の直列に接続された合成利得段(42、44、46)を含む。合成利得段はトランスコンダクタンス段(48)及びトランスインピーダンス段(50)を含む。トランスコンダクタンス段は第1電源電圧端子から第2電源電圧端子への第1電流経路(52、56、64)及び第2電流経路(54、58、66)を有する。第1可変抵抗(62)は第1電流経路と第2電流経路との間に接続される。トランスインピーダンス段は、第1電流経路の出力に接続された入力端子と、出力端子とを有する第1インバータ(68、72)及び第2電流経路の出力に接続された入力端子と、出力端子とを有する第2インバータ(70、74)を有する。第2可変抵抗(76)は第1インバータの入力端子と出力端子との間に、第3可変抵抗(78)は第2インバータの入力端子と出力端子との間に接続される。

(もっと読む)

位相ロックループ回路

【課題】電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路と、検出された位相差に応じた電流を第1の容量に出力するチャージポンプ回路と、第1の容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路とを有する位相ロックループ回路にて、チャージポンプ回路による第1の容量への電流の出力完了後の第1の時刻に第1の電圧を保持し、保持された第1の電圧に基づき電圧制御発振回路の入力部に流れるリーク電流に応じた電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して第1の容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

発振装置

【課題】水晶振動子の動作時間の経過に伴う発振周波数の変化を補償して安定した発振周波数が得られる発振装置を提供すること。

【解決手段】基準時から所定の時間が経過した後における第1及び第2の水晶振動子の周波数差と、基準時における第1及び第2の水晶振動子の周波数差と、の差分値ΔF(即ち、第1の水晶振動子における周波数について基準時からの変化分と、第2の水晶振動子における周波数について基準時からの変化分との差分値ΔF)を求める。そして基準時からの時間の経過に対して、第1の水晶振動子の周波数の変化分と第2の水晶振動子の周波数の変化分との比率が同じであるとして取り扱ったときの当該比率を経時変化の補正係数とし、差分値ΔFに対応する値と経時変化の補正係数とに基づいて、発振装置の出力を作り出すための水晶振動子の周波数について補正値を取得する。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を含むSSCG回路であって、出力クロック信号のジッタを低減する。

【解決手段】SSCG回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた第1の移相量で変化させるように、さらに、所定の範囲内で周期的に変化する第2の移相量を第1の移相量に加算するように、位相選択回路6を制御する。

(もっと読む)

周波数追尾装置

【課題】異なるコヒーレント加算時間で算出した積算パワーの平方根の差分によって周波数ずれ量を算出することで、高精度な周波数ずれ量を算出する。

【解決手段】 所望の衛星信号yを加算時間MAでコヒーレント加算し、NA回ノンコヒーレント加算をして、積算パワー|yA|2を算出する積算器17と、衛星信号yを加算時間MAと異なる加算時間MBでコヒーレント加算し、NB回ノンコヒーレント加算をして、積算パワー|yB|2を算出する積算器18と、積算器17によって算出される積算パワーの平方根|yA|と、積算器18によって算出される積算パワーの平方根|yB|との差分から、周波数ずれ量Δf2を算出する周波数ずれ演算器20と、を備え、周波数ずれ演算器20で算出された周波数ずれ量Δf2に基づいて、所望の衛星信号yを追尾する。

(もっと読む)

1 - 20 / 187

[ Back to top ]