Fターム[5J106CC37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598)

Fターム[5J106CC37]の下位に属するFターム

Fターム[5J106CC37]に分類される特許

61 - 65 / 65

半導体集積回路装置

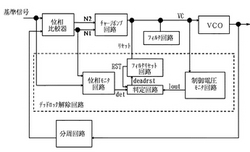

【課題】 高信頼性のデッドロック解除機能を持つPLL回路を備えた半導体集積回路装置を提供する。

【解決手段】 PLL回路のデッドロック解除回路として、制御電圧モニタ回路によりPLL回路の位相比較出力に対応したVCO制御電圧が規定値を超えることを検出し、位相モニタ回路により基準信号と帰還信号の位相が入力半サイクル以上外れていることを検出し、判定回路により上記制御電圧モニタ回路と位相モニタ回路の両検出信号が成立した場合にのみデッドロック状態と判定して、上記VCO制御電圧を強制的に下げてデッドロック状態の解除を行う。

(もっと読む)

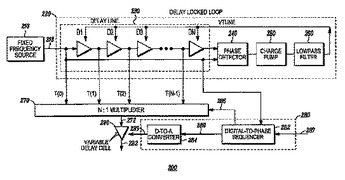

周波数合成の方法と装置

DPC(200)であって、周波数源(20)と、クロック信号を受信し複数の位相シフトされたクロック信号を生成する遅延ロックループ(220)と、合成信号の所望の周波数を識別する入力信号を受信する為の、DPS(282)とDAC(284)とを有した制御装置(280)と、複数の位相シフトされたクロック信号を受信し、位相シフトされたクロック信号の1シーケンスを選択し、粗い合成信号を出力する選択回路(270)と、可変遅延セル(290)とがあるDPC(200)であり、可変遅延セル(290)が、粗い合成信号を修正して、周波数が実質的には所望の周波数である合成信号(292)を生成する為に、粗い合成信号を受信するべく選択回路に結合された第1の入力と、微同調調整信号を受信する為に制御装置に結合された第2の入力とを有している。DPCには更に、DPCを較正するトレーニング装置がある。  (もっと読む)

(もっと読む)

チューナ回路

【課題】発振周波数を分周して混合器に供給する形式の回路において、分周回路で生成された高調波成分や、原発振周波数成分などの不要成分が混合器に入力されることにより種々のビート成分が発生し、これが原因でテレビジョン受像機画面にノイズが入る。

【解決手段】分周回路21で生成された不要成分が混合器6または16に供給されるのを防ぐため、分周回路21と混合器6または16の間に、遮断周波数変動手段を有するフィルタ回路61を設け、受信周波数に応じて適切に遮断周波数を変動させて、前記不要成分を除去することにより、ビート成分を抑圧し、テレビジョン受像機画面を鮮明にすることができる。

(もっと読む)

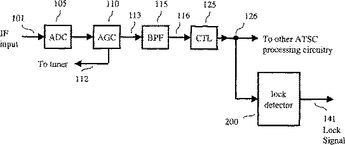

搬送波トラッキング・ループ・ロック検出器

ATSC(次世代TVシステム委員会)VSB(残留側波帯)受信機(15)は、受信したATSC‐VSB信号を処理する搬送波トラッキング・ループ(CTL)115と、CTLロック検出器(200)を具える。CTLロック検出器は、受信されダウンコンバートされたATSC‐VSB信号を平均化してDCオフセットを発生する平均化フィルタ(135)、DCオフセットを推定する推定器(130)、およびDCオフセットの推定値とDCオフセットとの比較の関数としてロック信号を発生する比較器(140)を具える。ロック信号は、CTLのロックされた状態またはアンロックされた状態の何れかを表す。  (もっと読む)

(もっと読む)

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

61 - 65 / 65

[ Back to top ]