Fターム[5J106CC37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598)

Fターム[5J106CC37]の下位に属するFターム

Fターム[5J106CC37]に分類される特許

1 - 20 / 65

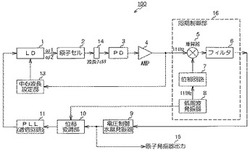

原子発振器

【課題】キャリア光を帯域通過フィルタによって減衰させて、信号検出のS/Nを改善して周波数安定度を高めた原子発振器を提供する。

【解決手段】の原子発振器100は、半導体レーザーにより構成されるLD(光源)1と、LD1に直流電流を与え、LD1の波長を所定の値に設定する中心波長設定部13と、アルカリ金属が封止された原子セル2と、アルカリ金属原子を透過したキャリア光(ωc)と共に第1の共鳴光(ω1)、及び第2の共鳴光(ω2)のうちいずれか一方の光を減衰させる波長フィルタ14と、波長フィルタ14を通過した原子セル2の透過光を検出するPD(光検出器)3と、を備えて構成される。

(もっと読む)

バーストクロック発生回路

【課題】バーストクロック信号を安定に生成できるバーストクロック発生回路を提供する。

【解決手段】このバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では位相ロックフィルタ4の応答速度を0に設定し、各垂直帰線期間のうちの垂直同期期間を除く期間では位相ロックフィルタ4の応答速度を比較的速い速度v1に設定し、複合映像信号における垂直帰線期間以外の表示期間では位相ロックフィルタ4の応答速度を比較的遅い通常の速度v2に設定する。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成できる。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、

波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティングの温度を制御する温度制御部20bと、を有する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティング20aに電圧を印加する電圧印加部20bと、を有する。

(もっと読む)

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

(もっと読む)

ダイレクト・デジタル・シンセサイザ回路

【課題】 正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路を提供する。

【解決手段】 周波数設定データをデータ分離部1で上位ビットと下位ビットに分離し、位相内挿補正値出力部10が下位ビットの累積によるオーバーフローで補正パラメータ1を出力し、下位ビットの積分値から得られた補正値を補正パラメータ2として出力し、上位ビットのデータに補正パラメータ1を正弦波ROMアドレス生成部2で加算して積分して正弦波ROMテーブル5で対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部6で直交成分に補正パラメータ2を乗算し、同相成分との差分を演算することで、位相補正を行うDDS回路である。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

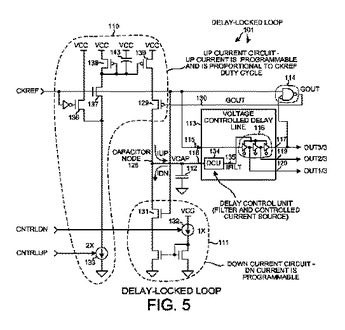

入力信号デューティサイクル変動に依存しない遅延を有する遅延ロックループ

遅延ロックループ(DLL)は、第1の信号を「遅延時間」だけ遅延させ、それによって第2の信号を生成するために、遅延線を使用する。キャパシタは、第1の信号の第1のエッジで開始して第2の信号のエッジまで続く第1の率で充電される。次いで、キャパシタは、第1の信号の別のエッジまで第2の率で放電される。制御ループは、キャパシタが充電される量が、キャパシタが放電される量と同じであるように、遅延時間を制御する。遅延時間は、一定であり、第1の信号のデューティサイクルの変動に実質的に依存しない。一例では、デューティサイクル歪み相殺(duty cycle distortion cancellation)は、第1の信号のデューティサイクルの変化に対して比例して第1の率を変更することによって達成される。別の例では、第1の率および第2の率は、第1の信号のデューティサイクルに依存しない。  (もっと読む)

(もっと読む)

同期伝送装置及びジッタ抑圧方法

【課題】同期伝送装置及びジッタ抑圧方法に関し、入力クロックとシステムクロックの周波数偏差のゼロ交叉点付近で発生するピークジッタを抑圧する。

【解決手段】入力クロックを自装置内のシステムクロックでリタイミングした基準クロックを生成するディジタル回路15_1と、基準クロックに同期した出力クロックを生成するPLL回路15_2と、入力クロックの周波数偏差とシステムクロックの周波数偏差との接近を検出する周波数偏差接近検出部1_1と、該周波数偏差の接近が検出されたとき、該周波数偏差の差が増大するよう、システムクロックの発振器1_3の発振周波数を調整する周波数調整部1_2を備える。

(もっと読む)

周波数掃引方法及び回路

【課題】階段状波形による繰返し周波数信号が生成されることなく、高速掃引が可能となり、また温度等の環境条件に左右されることなく、周波数制御を安定して行う。

【解決手段】VCO1からの出力をプログラマブルカウンタ14、PFD16、安定化フィルタ17及び傾き制御用フィルタ18を介して帰還させるループを形成し、プログラマブルカウンタ14からの現在の周波数ポイントの制御信号に基づく周波数引込み時間内に、次の周波数ポイントの制御信号をPFD16に出力し、位相同期状態を経ることなく、連続した周波数の掃引を実行する。上記傾き制御用フィルタ18では、掃引における周波数変化の傾きを制御する。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

1 - 20 / 65

[ Back to top ]