Fターム[5J106CC39]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | BPF (32)

Fターム[5J106CC39]に分類される特許

1 - 20 / 32

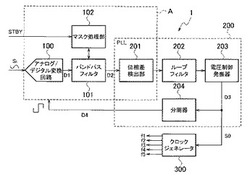

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

無線受信機

【課題】PLLのループフィルタの帯域を大きくすることにより、局部発振器の位相雑音性能が大幅に改善し、隣接チャネル選択性能を改善する受信機を提供する。

【解決手段】受信信号と局部発振器から出力されるローカル信号とをミキサでミキシングし、生成された中間周波数(IF)信号をバンドパスフィルタで選択して復調する無線受信機において、局部発振器は、受信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成であり、バンドパスフィルタは、受信信号の受信すべきチャネルによって通過帯域の中心周波数を切り替える構成である。

(もっと読む)

送受信装置及び同期システム

【課題】2つの送受信装置の間の同期確立と距離を測定する

【解決手段】他の第2送受信装置に対して第1信号を送信し、第2送受信装置において受信した第1信号を折り返して第2信号として返信して、フェズドロックループ(PLL)により同期をとる送受信装置である。基準信号を出力する基準発振器と、送信ベースバンド信号を発生する、位相と周波数が可変の信号発振器と、送信ベースバンド信号により搬送波を変調して得られる第1信号を送信する送信器を有する。第2送受信装置から受信した第2信号を復調して受信ベースバンド信号を得る受信器と、送信ベースバンド信号と基準発振器の出力する基準信号との第1位相差を検出する第1位相比較器と、受信ベースバンド信号と基準発振器の出力する基準信号との第2位相差を検出する第2位相比較器と、第1位相差と第2位相差との絶対値の差を出力する比較器とを有する。比較器の出力が零となるように、信号発振器の位相と周波数をフィードバック制御した。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

原子発振器

【課題】回路部分の小型化や省電力化が容易な原子発振器を提供する。

【解決手段】原子発振器1は、アルカリ金属原子に共鳴光対を照射することにより生じる電磁誘起透過現象を利用する原子発振器であって、光源10、気体状のアルカリ金属原子20、光検出部30、周波数制御部40を含む。光源10は、可干渉性を有し、周波数が異なる第1の光と第2の光を含む複数の光を発生させて、アルカリ金属原子20に照射する。光検出部30は、アルカリ金属原子20を透過した複数の光22を受け取り、当該複数の光22の干渉により得られる所定の周波数のビート信号を含む検出信号32を生成する。周波数制御部40は、検出信号32に含まれる所定の周波数のビート信号に基づいて、第1の光と第2の光がアルカリ金属原子20に電磁誘起透過現象を起こさせる共鳴光対となるように、第1の光及び第2の光の少なくとも一方の周波数制御を行う。

(もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

位相同期回路

【課題】ノイズが混入した場合であっても、所望の周波数で発振信号を生成することが可能な位相同期回路を提供する。

【解決手段】位相同期回路は、低域通過フィルタからの出力電圧に応じて発振回路から出力される発振信号を、制御信号に基づいた利得で増幅する可変利得増幅回路と、可変利得増幅回路からの増幅信号の位相に応じた第1の位相と、増幅信号の基準となる基準信号の第2の位相とを比較して、第1の位相と第2の位相とを一致させるための比較信号を低域通過フィルタに出力する位相比較回路と、出力電圧に基づいて、第1の位相と第2の位相とが一致しているか否かを検出する検出回路と、検出回路の検出結果に基づいて、第1の位相と第2の位相とが一致している場合、利得が所定の値となるような制御信号を生成し、第1の位相と第2の位相とが一致していない場合、利得を所定の値より増加させるような制御信号を生成する制御信号生成回路と、を備える。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ時間を短時間にする。

【解決手段】マイクロ波MWに基づき共鳴信号RSを発生する原子共鳴器1と、原子共鳴器1が発生する共鳴信号RSを増幅する増幅器2と、位相変調信号LWを出力する低周波発振器10と、共鳴信号RSと位相変調信号LWとに基づき制御電圧VCを出力する周波数制御部4と、制御電圧VCによって発振信号OUTの周波数が制御される電圧制御発振器8と、発振信号OUTを位相変調信号LWに基づき逓倍及び位相変調してマイクロ波MWを出力する逓倍位相変調部9と、記憶部27と、共鳴信号RSの周波数がロックされたロック状態の時に制御電圧VCを所定の時間間隔TSで記憶部27に同期電圧SVとして記憶させ、共鳴信号RSの周波数がロックされていない非ロック状態の時に制御電圧VCと同期電圧SVとに基づき周波数制御部4に制御信号S2を出力する制御部26と、を含むルビジウム原子発振器100。

(もっと読む)

基準信号生成装置及びこれを用いた機器

【課題】広く普及しているADSL方式等を採用した通信回線を利用して、利用者側において、通信品質の低下や発着信の制約等を生じることなく、高精度な基準信号を容易且つ安価に得ることが可能な基準信号生成装置及びこれを用いた機器を提供する。

【解決手段】局側の通信装置と、利用者側の端末装置との間で、通信回線を介して通信を行う通信システムを用いて基準信号を生成する基準信号生成装置において、前記局側の通信装置から前記通信回線を介して伝送される一定の周波数を有する基準信号が含まれる信号を入力し、前記入力信号から基準信号を抽出する基準信号抽出回路を備えるように構成した。

(もっと読む)

高周波発振器

【課題】周囲の環境温度による光ファイバの熱伸縮に対してもPLL制御を正常に行うことができる高周波発振器を得る。

【解決手段】レーザ光源が発生したレーザ光を光変調器により変調し、光ファイバを介して伝送した変調後のレーザ光を光電変換器により高周波信号に変換し、変換後の高周波信号からバンドパスフィルタにより所定の通過帯域成分を取り出し、当該所定の通過帯域成分の高周波信号の周波数を変調信号として前記光変調器に帰還すると共に発振信号として出力する高周波発振器において、高周波信号の周波数が一定になるように制御するPLL制御手段と、当該高周波発振器の発振周波数の変動をPLL制御手段の予め設定した周波数引き込み範囲内に納めるように高周波信号の位相を調整する位相調整手段を備えた。

(もっと読む)

PLL発振回路

【課題】ループ中に、バッファアンプや逓倍回路と、不要周波数成分を除去するフィルタを含むPLL発振回路において、広帯域に発振周波数を変化させた場合でも、簡単な構成によって、発振ループ中の不要周波数信号成分を除去し、安定化した発振出力を得ることが可能なPLL発振回路を提供する。

【解決手段】PLL発振回路において、電圧制御発振器と位相比較器との間に不要周波数成分を除去するフィルタ回路を挿入するとともに、電圧制御発振器の制御電圧情報を記憶した制御電圧メモリの出力信号によって、上記フィルタ回路の通過周波数帯域を変更するように構成する。

(もっと読む)

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

周波数変調機能付きクロック生成回路

【課題】良好なスペクトラム拡散効果を有し、ノイズの発生が少なく周辺回路や電子部品の誤動作を低減することができる周波数変調機能付きクロック生成回路を提供する。

【解決手段】クロック生成回路1は、帰還用分周器17を有し、周波数変調されたクロックを出力するPLL回路10と、帰還用分周器17から所定の周波数のみ取り出しPLL回路10に入力するバンドパスフィルタ20と、三角波を生成する三角波生成回路40とを有し、バンドパスフィルタ20は、サイン波生成器としても機能し、所定のタイミングでサイン波を生成して三角波と合成して帰還用分周器17の分周比を変化させる。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

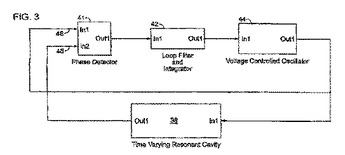

入力電圧の周波数に共振空胴の共振周波数を一致させる

シンクロサイクロトロンは、共振空胴を画定する磁気構造と、共振空胴に粒子を供給するイオン源と、共振空胴に高周波(RF)電圧を供給する電圧源と、RF電圧と時間とともに変化する共振空胴の共振周波数との間の位相差を検出する位相検出器と、この位相差に応答して、RF電圧の周波数が共振空胴の共振周波数と実質的に一致するように電圧源を制御する制御回路とを含む。電圧源が電圧制御発振器VCOを備え、フィードバック回路が、入力電圧の周波数と共振周波数との間の位相差を検出する位相検出器を備え、VCOが、位相差が所定値を逸脱したとき入力電圧の周波数を変化させるように構成される。  (もっと読む)

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、外部基準信号の検波における温度特性に応じて外部基準信号の入力レベルの適正範囲内を特定し、その適正範囲の内外に対して電圧制御発振器の制御電圧を制御して高安定な発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、温度センサ22と、固定電圧供給回路23と、外部基準同期モードとして位相比較器12とループフィルタ14を接続し、固定電圧モードとして固定電圧供給回路23とループフィルタ14を接続する選択スイッチ13と、検波回路17で検出された外部基準信号レベルの検波電圧が温度センサ22で検出された温度の温度特性に応じた適正範囲内であれば外部基準同期モードとし、適正範囲外であれば固定電圧モードとして選択スイッチ13を切り替えるCPU20とを有する発振周波数制御回路である。

(もっと読む)

1 - 20 / 32

[ Back to top ]