Fターム[5J106CC40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | HPF (9)

Fターム[5J106CC40]に分類される特許

1 - 9 / 9

PLL周波数シンセサイザ

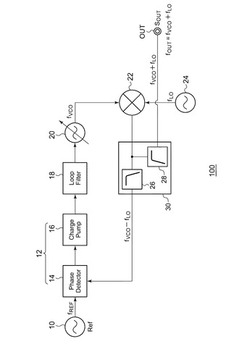

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

PLL回路

【課題】出力クロック信号のロングタームジッタを抑制するPLL回路を提供する。

【解決手段】位相比較器、チャージポンプ回路、ループフィルタ、及び電圧制御発振器を有するPLL回路において、基準クロック信号と帰還クロック信号との位相差が所定の閾値より大きい場合には、位相差の単位量当たりに対する変化を小さくして位相差に応じた出力電流を出力し、位相差が所定の閾値以下である場合には、位相差の単位量当たりに対する変化を大きくして位相差に応じた出力電流を出力するようにして、ロック後のループ帯域を広げることができるようにする。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

変調回路の変調度調整方法

【課題】VCXOによって変調が行われる帯域の変調度と、VCOによって変調が行われる帯域の変調度とのバランス調整作業を改善すること。

【解決手段】本発明に係る変調回路の変調度調整方法では、

音声信号とトーン信号が合成された信号をVCXOとVCOの両方に入力して変調を行う変調回路であって、VCXOによる変調の変調度とVCOによる変調の変調度のバランスを調整する電子ボリュームを備えた変調回路の変調度調整方法において、

前記変調回路に、変調出力信号の変調度を計測する計測手段を接続し、

前記変調回路に、VCXOとVCOの通過帯域が重なる重複帯域の上端における周波数の正弦波を入力したときに前記計測手段にて計測される変調度と、前記重複帯域の下端における周波数の正弦波を入力したときに前記計測手段にて計測される変調度との差が、所定の範囲内に収まるように、前記電子ボリュームを調整する。

(もっと読む)

PLL回路

【課題】 ループゲインを大きくすることができ、ループ利得が上がらない場合でも、ロック時の位相ノイズを良化できるPLL回路を提供する。

【解決手段】 入力端子1からの基準周波数を第1,3の分周器2,9で分周し、VCO8からの出力と発振器13からの出力をミキサ14で合成し、MCF15aで周波数を選択して、第2,4の分周器3,10で分周し、第1,第2の分周器2,3からの出力を位相比較器4で位相比較し、LPF5で平滑化し、第3,第4の分周器9,10からの出力を位相進み/遅れ検出器11で位相の進み又は遅れを検出し、積分器12で積分して電圧を出力し、加算器6でLPF5からの出力と積分器12からの出力を加算してVCO8に出力し、MCF15aからの出力を増幅器16で増幅して出力端子17に出力し、基準周波数に対して発振器13での周波数を調整するPLL回路である。

(もっと読む)

PLL回路及びそれを用いた周波数設定回路

【課題】ループフィルタ出力での基準周波数成分を十分に落とせ、かつ、PLLループ内の位相余裕を確保できるPLL回路の提供。

【解決手段】本発明のPLL回路は、電気信号により発振周波数が制御される周波数発振器(VCOまたはICO)13からの出力信号が高域通過フィルタ(HPF)14を介して位相検波器11の一方の入力端子に入力され、位相比較器11の他方の入力端子には基準周波数が入力され、前記位相比較器11の出力信号はループフィルタ12を介して、その直流成分を前記電気信号として周波数発振器13を制御する。

(もっと読む)

周波数シンセサイザ

【課題】 PLL回路では、構成部品で発生、もしくは外部から漏れ込んで出力信号にのってくるスプリアスを抑圧することは容易ではなく、特に近傍のスプリアスに関しては抑圧することが困難であった。

【解決手段】 基準信号及びN分周したフィードバック信号をそれぞれ2系統に分割し、一方の基準信号の位相を180度位相器により180度反転させることで、位相比較された互いに逆相の信号を生成し、高域通過フィルタによって一方の出力信号からノイズを取り出した後、一方の出力信号と高域通過フィルタの出力信号を合成器にて合成して、電圧制御発振器に入力される制御信号からノイズを打ち消す。

(もっと読む)

電圧制御発振回路、およびその調整方法

【課題】 簡易な回路構成により、構成素子の特性の製造バラツキにかかわらず、出力特性のバラツキを抑制する調整が可能な、電圧制御発振回路、およびその調整方法を提供すること。

【解決手段】 低域通過フィルタ15、高域通過フィルタ16は、電圧制御発振回路11を構成する素子と同一構造の素子で構成され、所定の相関関係が形成される。補正素子14は、電圧制御発振回路11において発振周波数制御信号VTが入力される主素子と並列に接続される。目標ゲイン値TGにおいて、低域通過フィルタ15と高域通過フィルタ16との周波数−ゲイン特性は互いに逆の傾きを有して交差する。容量値が低くばらつく場合、基準周波数fREFにおいて、出力信号SL2がSH2よりも出力レベルが大きくなり、出力レベル差LD2が発生し、LD2に応じた調整信号VCNT2が出力され、発振周波数fVCOが低くされる。

(もっと読む)

直接デジタル合成方式による周波数合成器

直接デジタル合成方式による周波数合成器は、入力(3)に存在する位相増分Mによって位相信号Pを周期的に増加するための位相アキュムレータ(1)と、位相信号Pの位相値に対応する正弦関数値を決定するため正弦関数値表をメモリーセルに記憶する記憶装置(6)と、時間対離散の正弦関数値を擬似アナログ正弦時間関数に変換するためのデジタル−アナログ変換器(11)と、擬似アナログ正弦時間関数を平滑化するためのアンチエイリアシングローパスフィルタ(16)とを備える。直接デジタル合成方式による周波数合成器はさらに、記憶装置(6)とデジタル−アナログ変換器(11)との間に接続された、時間対離散の正弦関数値に非周期的信号(NS)を重ね合わせる加算器(19)を含む。 (もっと読む)

1 - 9 / 9

[ Back to top ]