Fターム[5J106CC43]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | アナログ型 (51)

Fターム[5J106CC43]の下位に属するFターム

Fターム[5J106CC43]に分類される特許

1 - 17 / 17

PLL回路

【課題】電圧制御発振回路の発振周波数レンジを広く保持しつつ、出力クロックのジッターを低減することが可能なPLL回路を提供する。

【解決手段】PLL回路は、基準クロックと出比較回路チャージポンプ回路を備え、チャージポンプ回路の出力に一端が接続された抵抗素子と、抵抗素子の他端に一端が接続され且つ接地に他端が接続された容量素子とを有し、チャージポンプ回路が出力した電流を変換して、抵抗素子の一端から第1の制御電圧信号を出力し且つ容量素子の一端から第2の制御電圧信号を出力する第1の低域通過フィルタを備える。PLL回路は、抵抗素子の一端に第1の非反転入力端子が接続され、容量素子の一端に第2の非反転入力端子が接続され、出力端子と反転入力端子とが接続され、出力端子から第3の制御電圧信号を出力するアンプ回路を備える。PLL回路は、第3の制御電圧信号に応じた周波数の出力クロックを出力するVCO回路とを備える。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

電圧制御発振回路およびクロック信号生成回路

【課題】制御電圧に対する可変容量の容量値の変化の線形性を向上して位相ノイズを低減した電圧制御発振回路の実現。

【解決手段】制御電圧に応じて発振周波数が変化する発振信号OUT,OUTXを出力する電圧制御発振回路において、印加電圧に応じて容量値が変化する複数の可変容量VAC1-VAC4と、制御電圧を分圧して複数の可変容量に印加する分圧電圧VT,VT1-VT3を生成する分圧電圧生成部R1-R4と、を備える。

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

PLL発振回路

【課題】ループ中に、バッファアンプや逓倍回路と、不要周波数成分を除去するフィルタを含むPLL発振回路において、広帯域に発振周波数を変化させた場合でも、簡単な構成によって、発振ループ中の不要周波数信号成分を除去し、安定化した発振出力を得ることが可能なPLL発振回路を提供する。

【解決手段】PLL発振回路において、電圧制御発振器と位相比較器との間に不要周波数成分を除去するフィルタ回路を挿入するとともに、電圧制御発振器の制御電圧情報を記憶した制御電圧メモリの出力信号によって、上記フィルタ回路の通過周波数帯域を変更するように構成する。

(もっと読む)

アナログ位相拘束ループ装置

【課題】単一で安定し信頼性のあるアナログのタイプIII位相拘束ループ装置を提供する。

【解決手段】位相検出器2は入力基準信号4及び出力信号6の位相差を表すエラー信号12を発生する。選択器14は第1帯域幅パラメータ値の選択時にエラー信号を第1信号経路8に供給し、第2帯域幅パラメータ値の選択時にエラー信号を第2信号経路10に供給する。第1信号経路はエラー信号を積分する第1積分器16と、その積分信号を積分してエラー電圧信号を発生する第2積分器18と、このエラー電圧信号に応答して第1信号経路出力信号を発生する電圧制御発振器20とを具えている。第2信号経路も同様な積分器22,24及び電圧制御発振器26を具えている。選択器28は第1帯域幅パラメータ値の選択時にVCO20の出力を選択し、第2帯域幅パラメータ値の選択時にVCO26の出力を選択する。選択器28の出力信号が位相検出器2に帰還する。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

チャージポンプがない位相固定ループ回路及びこれを含む集積回路

【課題】チャージポンプがない位相固定ループ及びこれを含む集積回路を提供する。

【解決手段】チャージポンプがない位相固定ループは、位相周波数検出器及びループフィルタを含む。ループフィルタは、プルアップ抵抗、プルアップ抵抗と直列に連結されたプルダウン抵抗及びプルアップ抵抗とプルダウン抵抗の連結ノードと連結された電気容量部を含み、位相周波数検出器から第1制御信号が入力される時に提供される第1基準電圧の入力を受けてプルアップ抵抗と電気容量部によって形成されたパスを通じて電気容量部を充電させ、位相周波数検出器から第2制御信号が入力される時に提供される第1基準電圧より低い第2基準電圧の入力を受けてプルダウン抵抗と電気容量部によって形成されたパスを通じて電気容量部を放電させ、充電された又は放電された電気容量部に基づいて生成された制御電圧を出力する。

(もっと読む)

移相回路

【課題】 移相量を常に一定に制御可能とし、電源電圧変動時等の影響の低減、素子バラツキの影響を低減する移相回路の提供。

【解決手段】基準周波数信号が入力されて2分配され一方の信号は位相比較器102の一方の入力となり、他方の信号は移相器101を介してその位相が移相された後に、前記位相比較器102の他方の入力となり、位相比較器102の出力はループフィルタ(LPF)103を介して差動増幅器104の一方の入力端子に入力され、差動増幅器104の出力信号により移相器101の移相量が制御されるPLLループを有し、差動増幅器104の他方の入力端子に印加される基準電圧により前記移相器101での移相量が定まる。

(もっと読む)

映像検波回路

【課題】AM変調されたPIF信号から映像信号を同期検波するVIF回路において、過変調状態にて復調される映像信号の精度が低くなる。

【解決手段】比較器68は、過変調状態であるVTH超の映像信号か否かを判定する。VTH以下の期間では、スイッチ回路56はAPCフィルタ54の出力電圧をVCO48に入力させ、PLLを構成する。PLLは、PIF信号にロックするように動作し、搬送波を再生する。一方、VTHを超える期間では、スイッチ回路56はSH回路58の出力電圧VSHをVCO48に入力する。SH回路58は、水平同期期間でのロック状態のAPCフィルタ54の電圧を保持しており、これを用いてVCO48を制御することで、フリーランや周波数ドリフトが抑制される。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子からみたインピーダンスを低くして、VCOの位相雑音特性の劣化を防ぐことができるVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータを入力し、アナログ信号を出力する粗調用DAC4と、微調用周波数のデジタルデータを入力し、アナログ信号を出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを接続する抵抗R6 と、LPF5の出力にLPF7の出力が加算されるよう容量結合するコンデンサC8 とを有するVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

情報記録再生装置、およびその記録クロック生成方法

【課題】ウォブル信号に同期して生成される記録クロックの周波数安定化を簡素な構成で実現することができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクに記録クロックを用いてデータを記録する情報記録再生装置において、光ディスクの再生信号から抽出されるウォブル信号によるフェーズロック制御に基づいて周波数制御され、記録クロックの発振源となるVCOと、VCOの周波数変動量を検出する周波数変動検出部と、を備え、VCOは、フェーズロック制御に基づく周波数制御に加えて、周波数変動検出部にて検出される周波数変動量に基づいて周波数制御される、ことを特徴とする。

(もっと読む)

マルチパス角度変調器の利得を常時較正する方法

マルチパス角度変調は、メイン制御ループに追加されたクローズドの二次ループを含み、高周波利得に関して較正ファクタを自動的に調整する。メイン制御ループは、主要パスとして角度変調信号の低周波部分を処理するように構成され、二次ループは、補助ループとして角度変調信号の高周波部分を処理するように構成されている。二次ループは較正情報を検知し、システムが主要動作を行っている間、較正情報を用いて変調ループ内で常時利得をリアルタイムで較正する。その結果、中断時間などのシステム停止または較正に特異的なタイミングが必要でなくなり、変調パスのバランスがとれる。較正は背景プロセスとして常時行われる。角度変調はすべての変調タイプのシステムに適用可能である。 (もっと読む)

別途の比例経路を有するクロックデータリカバリループ

【課題】安定性の高いバンバンCDRループを提供すること。

【解決手段】本発明によるクロックデータリカバリループ(30)は、非線形(例えば、バンバン)位相検出器(311)、チャージポンプ(31)、RCループフィルタ(32)、および、信号生成器(例えば、電圧制御発振器(VCO)(33))を含む。データ速度が遅いときは、ループ(30)はチャージポンプ(31)と、安定な二次挙動を示すループフィルタ(32)とともに、動作され得る。このとき、ループフィルタ(32)の抵抗器Rは比例経路として機能する。また、別途の比例経路(312)も提供され、VCO(33)の制御入力に位相検出器(311)の出力を直接提供する。その間、ループフィルタ(32)の抵抗器Rもバイパスされる。データ速度の増加が、三次の影響を生じさせるとき、別途の比例経路(312)が二次挙動を維持するように活性化され得る。

(もっと読む)

変調制御回路

【課題】 本発明は、変調された光信号を出射する外部変調器に好適な動作点を設定しつつ変調信号を与える変調制御回路に関し、広範なビットレートによる高品質の変調を可能とすることを目的とする。

【解決手段】 変調信号に重畳される第一のパイロット信号またはこの変調信号に重畳された第一のパイロット信号と、その変調信号に応じて外部変調器11が出射する光信号から抽出した第二のパイロット信号との位相差を検出する位相差検出手段12と、検出された位相差を外部変調器11に帰還し、その外部変調器11の動作点をこの位相差が抑圧される動作点に保つ制御手段13とを備えた変調制御回路において、帰還を実現する帰還路に配置され、かつ変調信号の成分の内、この変調信号の波形に伴う波形の乱れに応じてその帰還路の通過域に分布し得る成分を抑圧する濾波手段14を備えて構成される。

(もっと読む)

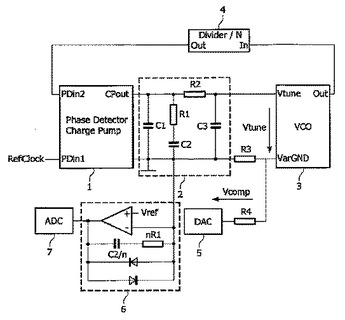

電圧制御周波数発生器における妨害を補償する装置及び方法

本発明は、電圧制御周波数発生器を有する位相同期ループにおいて妨害を補償する装置及び方法であって、周波数発生器が同調電圧Vtuneにより公称周波数に同調され、この周波数発生器の実際の周波数は周波数比較により基準周波数と比較され、周波数比較を介して偏差が検出された場合に再調整され、妨害が発生した場合に同調電圧Vtuneが妨害事象に依存する妨害電圧Vstorにより変えられ、かくして公称周波数から逸脱した周波数が発生し、該周波数偏差が位相同期ループにより再び補正されるような装置及び方法に関するもので、電圧制御周波数発生器を有する位相同期ループにおいて妨害補償をする装置及び方法を提供する目的に基づき、既知の妨害事象が起きたならば、この方法で既定の公称周波数からの偏差を避ける。この目的は、本発明により、もし既知の妨害事象が起きるならば、妨害電圧Vstorを補償する電圧Vcompが妨害電圧Vstorに同期して符号を反転して生成され、妨害電圧Vstorに重畳される、という方法により達成される。

(もっと読む)

(もっと読む)

1 - 17 / 17

[ Back to top ]