Fターム[5J106CC46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | デジタル型 (163)

Fターム[5J106CC46]の下位に属するFターム

D/A変換器出力型 (31)

アップダウンカウンタ出力型 (28)

Fターム[5J106CC46]に分類される特許

21 - 40 / 104

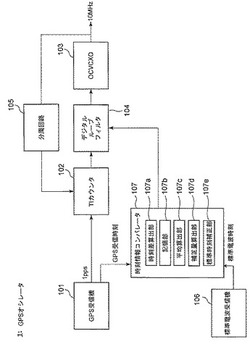

基準信号発生装置及び方法

【課題】 GPS信号の受信障害が発生しても、内蔵オシレータよりも高い周波数安定度の基準信号を発生することと、受信障害の発生前後で連続性の高い基準信号を出力することとを両立した基準信号発生装置を提供する。

【解決手段】 GPS受信機にて取得したGPS受信時刻と、そのGPS受信時刻の直前或いはその直後に標準電波受信機にて取得した標準電波受信時刻との時刻差を、予め定められた時間間隔毎に算出し、算出した時刻差と日時とを関連づけた時刻差データベースを構築する。GPS受信障害の発生を未検出のときGPS受信時刻に基づいて電圧制御発振器を制御して基準信号を発生し、GPS受信障害の発生を検出中は、時刻差データベースから取得した現在の日時に対応する時刻差に基づいて標準電波受信時刻を補正して電圧制御発振器を制御して基準信号を発生する。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

ADPLL、半導体装置及び携帯電話機

【課題】ノイズ等によって生じるチャタリングの発生を検知・訂正する機能をADPLLに提供する。

【解決手段】TDC802−2とカウンタ801−1を含むADPLLにおいて、TDCの出力(伝播遅延情報)をエンコードするエンコーダ802−3を用意する。エンコーダ802−3は複数のビットからなる伝播遅延情報を所定の単位に分けて、エンコーダ802−3内の16ビットエンコーダに個々の処理を行わせる。各16ビットエンコーダは、受け取った伝播遅延情報の一部の中に複数の変化点が存在する場合は、最下位ビットに近い変化点のみを残置させる。

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

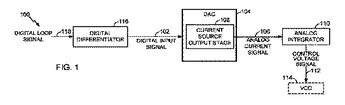

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

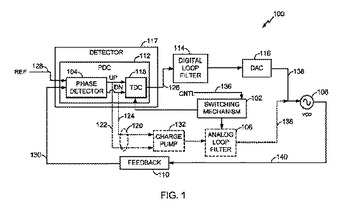

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

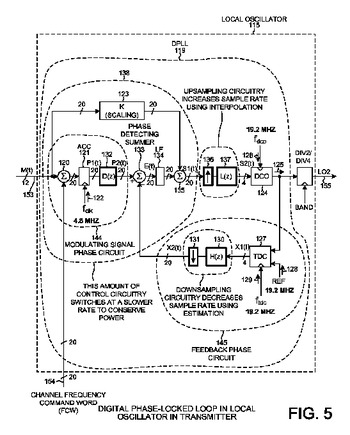

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

デジタルクロック・データ復元機およびこれを適用したトランシーバー

本発明は、デジタルフィルタ回路(digital filter)とデジタル制御発振器(DCO;digitally controlled oscillator)を用いて回路全体をデジタル回路化したクロック・データ復元機に関するものであり、本発明に係るデジタル制御発振器は、複数個のインバータチェーンを備えており、それぞれのインバータに電源電流を供給する電源電圧とインバータの間に可変抵抗スイッチングマトリックスを構成して供給電源を変化させ、発振周波数をチューニングする。

ここで、可変抵抗スイッチングマトリックスは、PMOSトランジスタ配列を用いて具現化するものの、低いレベルでの周波数チューニングステップと高いレベルでの周波数チューニングステップを互いに均等化するために、スイッチングマトリックスの列と列の間に垂直抵抗を追加挿入している。また、ジッタ発生問題を解消するために、第1シグマデルタモジュレータを用いてディザリング回路を具現化しており、セグメントサーモメーター方式を適用して少ない個数のルーティングラインでデジタル制御発振器をチューニングしている。  (もっと読む)

(もっと読む)

21 - 40 / 104

[ Back to top ]