Fターム[5J106CC46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | デジタル型 (163)

Fターム[5J106CC46]の下位に属するFターム

D/A変換器出力型 (31)

アップダウンカウンタ出力型 (28)

Fターム[5J106CC46]に分類される特許

61 - 80 / 104

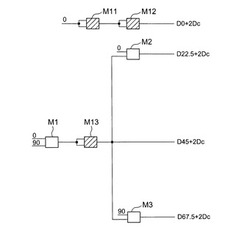

位相補間器及びクロックデータリカバリ装置

【課題】本発明は、ミキサの数を減らすことで回路面積及び消費電力を縮小し、位相の不整合を抑制することが可能な位相補間器を提供する。

【解決手段】位相差が0度のクロックD0を与えられミキサ2個分の遅延量を有するクロックD0+2Dcを出力する2ミキサM11、M12、位相差が0度のクロックD0と位相差が90度のクロックD90とを与えられ位相差が45度の遅延量とミキサ2個分の遅延量とを有するクロックD90+2Dcを出力するミキサM1、M13、クロックD0、D90、D45+2Dcのいずれか2つを用いて位相差が所定角度の遅延量とミキサ2個分の遅延量とを有するクロックを生成して出力する少なくとも1つのミキサを備える。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

通信装置、発振器、並びに周波数シンセサイザ

【課題】CDMAやOFDMといった大きな包絡線変動を伴う変調方式を使用することができ、送信機に線形性と高効率を両立するLINC送信機を提供する。

【解決手段】変調データの周波数変換を行なうPLLにおいて2ポイント変調方式を採用することで、発振器に入力される変調データはPLLにとって外乱とは見えなくなり、PLLのループ帯域幅に制限されない広帯域変調を実現することが可能となる。また、発振器の積分効果により、サンプリング周波数付近におけるレプリカを、アナログ・スムージング・フィルタを追加することなく大幅に抑制することができ、回路のリコンフィギャラビリティを高めることができる。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

1つの態様では、デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作する。DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積する。DPLLは、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。 (もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】クロック生成回路が、ロック状態とは180°位相のずれた状態(擬似ロック状態)の出力クロックを出力する可能性がある。

【解決手段】遅延同期ループ型のクロック信号生成回路として、(a)第1のクロック信号を遅延して第2のクロック信号を生成する遅延線路と、(b)第2のクロック信号が第1のクロック信号に位相同期するように、遅延線路における遅延量を可変制御する遅延量制御部と、(c)第1のクロック信号と第2のクロック信号との擬似ロック状態を検出する擬似ロック検出部と、(d)擬似ロック状態の検出時、遅延線路の遅延量を変更する擬似ロック状態解除部とを有するものを提案する。

(もっと読む)

PLL回路

【課題】DCOの変換利得が常に一定の目標値となるように調整して安定したPLL動作を実現する。

【解決手段】まず、DCOの前段に位置する乗算器に、デジタル値である“1”を入力した状態で一度収束動作を完了させる。続いて、最初の収束状態でのDCOの制御デジタル値を任意の設定値で除したデジタル値をDCOの前段に位置する乗算器に切り替えて入力して、2度目の収束状態でのDCOの制御デジタル値を任意の設定値に収束させる。PLLの系において、DCOを制御するデジタル値の基準値を任意の値に調整して、DCOの変換利得を所望の値に調整できる。

(もっと読む)

半導体集積回路

【課題】ロック動作の初期において高速引き込みを可能とすると伴に入力信号ジッタや入力雑音の影響の小さなディジタルフェーズロックドループを提供すること。

【解決手段】半導体集積回路は、位相比較器10、11、ディジタルループフィルタ12、ディジタル制御発振器13、フィードバック分周器14を含むディジタルフェーズロックドループADPLLを具備する。ディジタルループフィルタ12は、第1ゲインαを有して位相比較器10、11のディジタル位相出力信号θが供給される比例パス12aと、第2ゲインβを有して信号θが供給される積分パス12b、12c、12dと、信号θの大きさを判定する判定器12g、12hを含む。ディジタル位相出力信号θの大きさが所定の基準値θthよりも大きい場合には、判定器12g、12hは第2ゲインβと第1ゲインαとの比β/αを大に設定する。

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

デジタル周波数検出器及びこれを用いたデジタルPLL

【課題】デジタルPLLや周波数シンセサイザなどに使用されるデジタル周波数検出器及びこれを用いたデジタルPLLを提供する。

【解決手段】本デジタル周波数検出器は、第1周波数のハイレベル区間に動作する第1リングオシレータを利用して、第1周波数をデジタル形式の第1周波数情報として出力する第1変換部と、第2周波数のハイレベル区間に動作する第2リングオシレータを利用して、第2周波数をデジタル形式の第2周波数情報として出力する第2変換部と、第1周波数情報及び第2周波数情報の比を演算し、第1周波数に対するデジタル周波数を出力する演算部と、を含む。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

CDR回路

【課題】カットオフ周波数をアダプティブに制御する。

【解決手段】CDR回路40には、位相検出器1、シリアル−パラレル変換器2、デジタルフィルタ3、位相制御器4、位相補間器5、積分器6、マルチプレクサ7、及びマルチプレクサ8が設けられる。積分器6は、デジタルフィルタ3で計算されたアーリィ(Early)信号[0:n]−レート(Late)信号[0:n]の符号の情報信号である出力信号SFを入力し、この信号を一定期間Mでモニターし、遅延要素と加算器とを用いて周波数ジッタとして積分する。CDR回路40は、デジタルフィルタの閾値と位相補間器の位相ステップを最適な値に変更して、カットオフ周波数をアダプティブに制御する。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

位相差検出回路、PLL回路、位相差検出方法及び位相差検出プログラム

【課題】 ゼロクロスポイント検出用のハードを用いることなく、位相差の検出機能を実現する。

【解決手段】 位相差検出回路は、検出信号と内部基準信号の位相差を検出するための回路であって、d−q軸変換ユニット5と、1周期全加算ユニット6と、位相差算出ユニット7とを備えている。d−q軸変換ユニット5は、内部基準信号を用いて検出信号をd−q軸変換することで、瞬時値有効分dと瞬時値無効分qとを算出する。1周期全加算ユニット6は、瞬時値有効分dを1周期全加算することで有効分Dを算出して、さらに瞬時値無効分qを1周期全加算することで無効分Qを算出する。位相差算出ユニット7は、有効分Dと無効分Qを用いて位相差を算出する。

(もっと読む)

記録装置及び記録装置の制御方法

【課題】ディスクの回転に安定して同期した記録クロックを生成できるようにする。

【解決手段】ディスク状記録媒体に形成されているウォブルを読み取ってウォブル信号を検出し、前記ウォブル信号に基いて記録用のクロック信号を生成する記録装置であって、前記ディスク状記録媒体のウォブル周期に関連した周波数を有するクロックを生成する第1のクロック生成手段と、前記ディスク状記録媒体にデータを記録するためのチャネル周期に関連した周波数を有するクロックを生成する第2のクロック生成手段とを備え、前記第1のクロック生成手段に組み込まれているDVCO部と同一のDVCO部を組み込んで前記第2のクロック生成手段を構成する。

(もっと読む)

PLL回路及びディスク装置

【課題】温度特性や経時変化がなく、線速度変化に合わせてループ特性をシームレスに補正できるPLL回路を提供する。

【解決手段】デジタルループフィルタ103は、位相比較器102が出力する位相誤差を入力し、デジタル周波数値を生成する。このデジタル周波数値は、D/A変換器104でアナログ電圧に変換され、VCO105は、D/A変換器104が出力する電圧に応じた周波数の同期クロックを出力する。位相比較器102が出力する位相誤差は、デジタルループフィルタ103の出力に所定の係数Aを乗じたものでゲイン補正され、デジタルループフィルタ103に入力される。デジタルループフィルタ103に入力する位相誤差を、出力クロック周波数に比例して変化させることで、PLLループ全体として、出力クロック周波数に依存して線形にループ特性が制御できる。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

タイムトゥデジタルコンバータ

【課題】タイムトゥデジタルコンバータを提供する。

【解決手段】タイムトゥデジタルコンバータは、高い解像度と広い測定範囲のために低解像度タイムトゥデジタルコンバータと高解像度タイムトゥデジタルコンバータとを含む。低解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔で測定する。高解像度タイムトゥデジタルコンバータは、第1信号と第2信号との時間差を第1量子化間隔よい更に小さい第2量子化間隔で測定する。低解像度タイムトゥデジタルコンバータは、高解像度タイムトゥデジタルコンバータより広い測定範囲を有する。

(もっと読む)

61 - 80 / 104

[ Back to top ]