Fターム[5J106CC46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | デジタル型 (163)

Fターム[5J106CC46]の下位に属するFターム

D/A変換器出力型 (31)

アップダウンカウンタ出力型 (28)

Fターム[5J106CC46]に分類される特許

81 - 100 / 104

数値制御型オシレータ(NCO)出力クロック位相平滑化

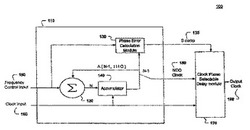

【課題】 入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを発生する形態とされている数値制御型オシレータ(NCO)を包含する位相平滑化回路が記載される。

【解決手段】 該複数個のNCOクロックパルスのエッジは該入力クロックのエッジに整合している。位相エラー計算モジュールが該NCOへ結合されており且つ該複数個のNCOクロックパルスの各々に対する対応する位相エラーを発生する形態とされている。クロック位相選択可能遅延が該位相エラー計算モジュールへ結合されており且つ該選択可能周波数において出力クロックを発生するために該対応する位相エラーに従って該複数個のNCOクロックパルスの各々を調節する形態とされている。

(もっと読む)

デジタルPLL回路およびデータ再生装置

【課題】回路規模の増大を抑制しながら、異なるPRMLに円滑に対応し得るデジタルPLL回路およびそれを採用するデータ再生装置を提供する。

【解決手段】PR(1,2,2,2,1)に従うデータ補間回路104の他にPR(1,2,2,1)に従うデータ補間回路110を配する。データ補間回路104には、デジタルVCO109によって生成されたPR(1,2,2,2,1)に従う位相情報が供給される。データ補間回路110には、デジタルVCO109によって生成された位相情報の位相を180°遅延させた位相情報が供給される。データ補間回路110に供給される位相情報は、位相調整回路113によって生成される。この構成によれば、デジタルVCO109からの位相情報をもとにデータ補間回路110のための位相情報が生成されるため、別途、データ補間回路110のためのPLL回路を配する必要がない。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】スイッチオーバーから発生する出力信号における不所望の位相変化を信頼性を持って回避することが可能なフェーズロックループ。

【解決手段】制御可能オシレータDCOが出力信号CKoutを発生し、PLL12入力クロックとして使用するために第一クロック/第二クロックCKin2、CKin1を切り換えることが可能である。使用中のCKin1又はCKin2と、CKoutのプリセットされ、位相シフトされたCK<1:8>間の位相差を決定し、DCOを制御するために使用され、使用されていないCKin2又はCKin1がCKoutを発生するために、位相が調節される。入力クロックの幾つかのCKin1,CKin2,CKin3間の位相差がスイッチオーバーの前に調節されることで、スイッチオーバーから発生するPLL出力信号における不所望の位相変化を高い精度で回避し且つヒットレススイッチングを達成する。

(もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

PLL回路、復調回路、ICカード及びICカード処理装置

【課題】本発明は、PLL回路、復調回路、ICカード及びICカード処理装置に関し、例えば非接触により種々のデータを入出力するICカードと、このICカードとデータ通信するICカード処理装置に適用して、簡易な構成で、入力信号が劣化した場合でも確実に入力信号を処理することができるようにする。

【解決手段】90度位相の異なる発振出力信号による位相比較結果の正負を基準にして制御方向を決定し、この制御方向に発振出力信号を制御する。

(もっと読む)

PLL回路

【課題】 従来のPLL回路では、位相雑音の抑圧特性は温度や個体差によってばらつき、更に、広い周波数帯域で安定した抑圧特性を得るのは困難であったが、温度や個体差による位相雑音特性の変動を吸収し、広い周波数帯域で安定した位相雑音の抑圧特性を得ることができるPLL回路を提供する。

【解決手段】 位相比較器の後段に、ループ利得を調節する第1のパラメータを格納する第1のレジスタ6と、位相比較器4の出力に第1のパラメータを乗算する第1の乗算器7と、応答特性を調節する第2のパラメータを格納する第2のレジスタ12と、第1の乗算器の出力に第2のパラメータを乗算する第2の乗算器13と、使用周波数帯・周囲の温度・装置の個体差に基づいて第1及び第2のレジスタに最適なパラメータを設定するCPU20とを備え、ループ利得及び応答特性を最適な値に調整して広い周波数帯で良好な抑圧特性を得るPLL回路である。

(もっと読む)

位相同期回路

【目的】 入力信号のジッタのみに応じて適切なループフィルタ特性を適用可能なことを課題とする。

【構成】 入力信号INと発振出力OUTとの間の位相差を検出する位相比較器11と、該位相比較器の比較出力を積分するループフィルタ12と、該ループフィルタの出力に対応する周波数の前記発振出力を生成する発振回路13とを備え、入力信号に位相同期した発振信号を出力する位相同期回路であって、入力信号に位相同期し、十分に位相雑音の少ない基準信号PLを生成するPLL回路21と、入力信号と基準信号間の位相差を検出する位相比較器22と、該位相比較器の比較出力を積分するローパスフィルタ23と、該ローパスフィルタの出力を周波数解析して得られた周波数成分に基づき第1の周波数f1を求めると共に、該第1の周波数よりも低い一定の関係にある第2の周波数f2によってループフィルタ12の帯域幅を制御するフィルタ制御部24とを備える。

(もっと読む)

クロック生成回路

【課題】クロック源となる発振器の経年変化によって生じた周波数変動を定期的な保守時に周波数測定を行うことなく検出する。

【解決手段】制御電圧によって制御されるOCVCXO102の出力に応じたクロック信号を生成する現用系クロック生成回路100と、OCVCXO102の出力を用いて生成されたリファレンス信号REFnを用いて現用系クロック生成回路100と同期するように決定される制御電圧によって制御されるOCVCXOの出力に応じたクロック信号を生成する予備系クロック生成回路200とからなり、制御電圧の値を監視することにより、OCVCXO102における周波数変動を検出する。

(もっと読む)

ホールドオーバ機能付きDPLL回路

【課題】デジタル同期網に関し、特にホールドオーバ時において自走周波数制御のために温度補正を行った高精度な基準クロックを生成するホールドオーバ機能付きDPLL回路を提供する。

【解決手段】ホールドオーバ機能付きDPLL回路は、DDSを使用したDPLL回路のホールドオーバモードにおいて、ホールドオーバ検出時における固定のDDS制御値にスレーブ発振器の温度特性から算出した補正値を加算することで、前記DDS制御値を前記温度特性に応じて可変する。

(もっと読む)

クロック信号発生装置、クロック信号発生方法及びプログラム

【課題】位相の変化に迅速に追従しつつ、クロックスリップが起こり難い(安定した)クロック信号を再生するクロック信号発生装置等を提供することである。

【解決手段】位相比較器1Aは、データ信号と、デジタルVCO1Cの再生クロック信号を基準としたデータ信号の位相の遅れ及び進みを検出する。ランダムウォークフィルタ1Bは、この遅れ進みの回数差を計測して、回数差の絶対値が所定値に達すると、差を打ち消す方向に再生クロック信号の位相を変化させるようデジタルVCO1Cを制御し、計測結果をリセットして計測を再開する。再生位相比較器3は、デジタルVCO1C及び2Cの各再生クロック信号の位相差を検出してランダムウォークフィルタ1Bに通知する。ランダムウォークフィルタ1Bは、通知された位相差が所定量に達している間は、計測結果のリセットやデジタルVCO1Cの再生クロック信号の位相の変更を行わない。

(もっと読む)

デジタル位相検出器

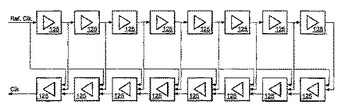

【課題】 従来、デジタル位相検出器における位相検出限界は、遅延素子の遅延時間により決定されるため、例えば、PLL回路に低ジッタ特性が要求される場合には、全デジタルPLL回路は不適当であった。

【解決手段】 第1のクロックCLKfを遅延する複数の第1の遅延素子1011〜101nと、第2のクロックCLKrを遅延する複数の第2の遅延素子1021〜102nと、前記第2の遅延素子により順次遅延された前記第2のクロックREF1〜REFnに従って、前記第1の遅延素子により順次遅延された前記第1のクロックFB1〜FBnを取り込み、相対的な位相関係を表すデジタル値Q1〜Qnを保持する複数のデータ保持回路1031〜103nと、を備えるように構成する。

(もっと読む)

マルチプレクサ機能と補間機能とが埋め込まれた電圧制御遅延線(VCDL)

電圧制御遅延線(VCDL)である。VCDL(120)は1つ以上のセル(125)を含む。この1つ以上のセルの各々は2つ以上の入力(Va、VaX、Vb、VbX)と出力(Vout、VoutX)とを含む。この1つ以上のセルの各々は、補間機能ならびにマルチプレクサ機能に加えて、遅延をもたらすように構成されている。VCDLは、遅延ロックループ(DLL)にて遅延をもたらすように使用される。  (もっと読む)

(もっと読む)

PLL回路およびデータ再生装置

【課題】 処理速度の高速化を円滑に図ることができるPLL回路およびそれを用いたデータ再生装置を提供する。

【解決手段】 固定クロックによってサンプリングされた一連のADデータに対し、時系列上交互に補間処理が施されるよう、2つのデータ補間回路203、204によって、並行して、補間処理を施す。このとき、各補間回路は、固定クロックの周期を1/2に低減した共通の動作クロック(1/2クロック)によって、対応するデータに補間処理を施す。このように、共通の動作クロックによって補間処理を並列的に行うことにより、動作クロックの周波数を固定クロックの1/2程度にまで低減させることができる。従って、その後段側に配される位相比較器107、LPF108、デジタルVCO109の動作周波数も同様に低減することができ、PLL回路の高速化を図ることができる。

(もっと読む)

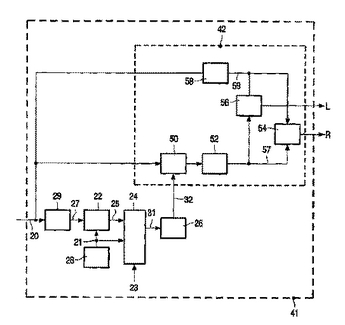

位相同期ループを用いない信号の回復

デジタル入力信号(20)から第1のデジタル信号(7、31)を回復するための構成が、デジタル入力信号(20)をフィルタリングするためのデジタル・フィルタ(29)と、デジタル基準信号(21)を生成するためのデジタル制御発振器28と、フィルタリングされたデジタル入力信号(27)とデジタル基準信号(21)との位相差(25)を求めるためのデジタル位相検出器(22)とを備える。第1のデジタル信号(7、31)は、求められた位相差(25)を、デジタル基準信号(21)の位相に加えることによって回復することができる。  (もっと読む)

(もっと読む)

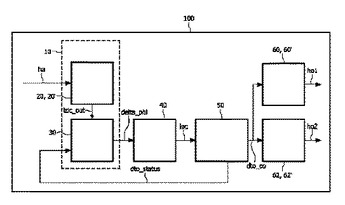

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

スイッチトキャパシタフィルタ及びフィードバックシステム

【課題】完全に平滑化された信号を出力するスイッチトキャパシタフィルタを実現する。

【解決手段】スイッチトキャパシタフィルタは、3個のスイッチトキャパシタ回路(32)を備えている。各スイッチトキャパシタ回路(32)は、容量(321)を有し、容量(321)が電流信号の入力端に接続された第1の状態、容量(321)が電圧信号の出力端に接続された第2の状態、及び容量(321)がフィルタ容量(31)の側に接続された第3の状態が循環する。そして、これら3個のスイッチトキャパシタ回路(32)は、互いに第1から第3の状態が重ならないようにインターリーブ制御される。

(もっと読む)

光ディスク装置及びPLL回路

【課題】PLL回路の安定化を図ることによって,良好な再生性能を実現する光ディスク装置を提供する。

【解決手段】FIRフィルターの前後の信号に対して,それぞれ位相検出器を設け,PLLの動作状況に応じて,それらを選択的に使用することにより,PLL回路の動作の安定化を図る。

【効果】ビタビ復号器の動作限界を引き出すように再生性能を向上した光ディスク装置を提供することができた。

(もっと読む)

記録媒体再生装置及び方法並びにディジタルPLL回路

【課題】 再生信号の品質が劣化したときのディジタルPLL回路におけるデッドロックを防止し、エラーレートを改善することを可能とする。

【解決手段】 制御信号に応じて発振周波数が変化する仮想VCO(電圧制御発振器)35と、入力信号の位相を位相検出部32で検出して得られる入力位相と上記仮想VCO35からのVCO位相とを比較して位相誤差を出力する位相比較部34と、この位相比較部34からの位相誤差をフィルタリングして制御信号として上記仮想VCO35に送るループフィルタであるLPF36とを有して成るディジタルPLL回路を有し、端子39には再生信号の品質劣化を検出して得られるリセット信号が入力される。このリセット信号によりLPF36をリセットすることにより、仮想VCO35の発振周波数を自走発振周波数にリセットする。

(もっと読む)

デジタルPLL回路

【課題】ホールドオーバ時の初期周波数偏差を抑えることを可能とするDPLL回路を提供する。

【解決手段】デジタル同期網の基準クロックに位相同期した内部クロックを生成するデジタルPLL回路であって,制御信号値の大きさに対応する周波数信号を生成するスレーブ発振器と,前記スレーブ発振器の出力と,入力する基準クロックの位相差を検知し,前記検知される位相差に対応する所定ビット数のデジタル信号を出力する位相差検知回路と,前記位相差検知回路の出力に基づき補正値を生成するホールドオーバ部とを有し,ホールドオーバが検知される時に前記ホールドオーバ部は,前記位相差検知回路の出力に周期的に補正値を加算して前記スレーブ発振器に対する制御値とする。

(もっと読む)

81 - 100 / 104

[ Back to top ]